逐次比较式ADC 采样频率的选取及应用

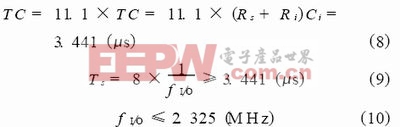

在Ci = 100 (pF) 及R i = 1 (kΩ) 时, 另测得信号放大电路的输出R s = 2 1 (kΩ)

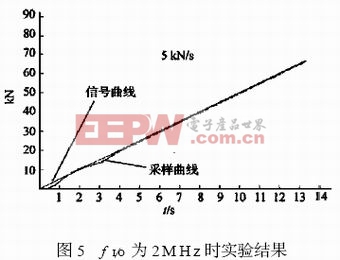

为保证TLC2543 的采样误差在1/16 L SB 之内, 单片机提供给TLC2543 的f I/O 不应高于2。 325MHz。当单片机提供给TLC2543 的f I/O 分别为4MHz 和2MHz 时, 其等速加载的控制结果见图4 和图5。

由图4 可见, 由于其f I/O 大于2。 325 MHz,TLC2543 的内部等效电容充电不完全, 因此采样误差较大, 从而控制品质较差。图5 中f I/O 小于2。 325MHz, TLC2543 的内部等效电容充电完全, 保证了其采样误差在1/16 L SB 之内, 因此其控制品质较好。

总 结

通过简化测控系统前向通道的等效模型, 说明了如何控制逐次比较式ADC 的采样频率与等效信号源的输出阻抗匹配, 从而保证ADC 的采样误差在1/16L SB 之内L。并通过实验对比, 验证了其有效性。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码