逐次比较式ADC 采样频率的选取及应用

在试验机测控系统中采样时间的计算及比较

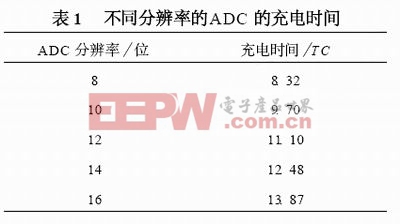

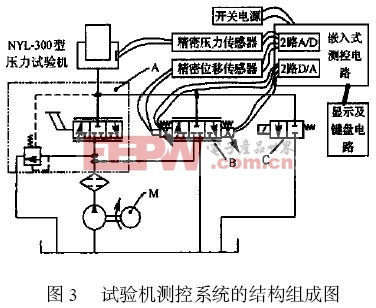

为了验证上述等效模型的有效性, 本文选用试验机测控系统等速加载来试验, 见图3。系统中的ADC 为TLC2543, TLC2543 是12 位精度SP I 接口的串行ADCL由TLC2543 数据手册可知, 其前8个I/O clock 为采样时间。在第12 个I/O clock 的下降沿开始AD 转换。因此其采样时间为

其中f I/O 为TLC2543 的I/O clock 频率。

由表1 知12 位的TLC2543 的充电时间及公式(5)。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码