分布式测控系统通信卡的研制

随着数字技术的发展,以计算机为站点的分布式系统在工程中得到日益广泛的应用。例如分布式目标监控系统,数据采集系统以及工业自动化系统等,这些系统的各站点需要向主机或互相之间进行数据的交换及通信。

目前,有些系统的站间通信仍然采用异步串行通信方式中的RS-232C接口标准和比较老的电流回路等。采用这种信号传输方式,随着信号传输距离的增加和速率的提高,传输线上的衰减、共地噪声等干扰的影响会显著加强,从而引起信号的畸变,由此限制了通信距离和传输速率。而在工程上的长距离通信应用中,RS-485接口标准有其独特优势。该标准采用平衡发送和差分接收,因此具有抑制共模干扰的能力,而且灵敏度高,能检测出低至200mV的电压,所以传输信号能在千米以外得以准确恢复;并且以此标准只用一根双绞线就可以实现多站联网,构成分布式系统的设备简单、价格低廉,故能在工程项目中得到广泛的应用。

现今市场上已有应用于网络通信、DCS或PLC系统的RS-485通信卡产品,但一般价格较高,且硬件内部对系统设计者不开放,所以作者研制了一个便于系统设计者使用的通信卡,该卡的硬件设计开放,使用者可以对其进行灵活方便的编程,且适用于多种工业环境。以下介绍该卡的研制开发过程。

2通信卡的总体设计

2.1要求

在分布式测控系统中,通信卡主要用于测控下位计算机与上位计算机的数据交换。分布式系统中的一个上位机要带多个远程测量单元,因此首先在通信距离上不能少于500米。其次,在构成通信网时,站与站之间可能会有很高的共模电压,而且传输线要经过工业现场,有可能会受到强大的干扰,因而通信卡必须要有很好的抗干扰能力。另外,通信线路还有可能经过某些特殊环境,如电厂、变电站、架空等等。实践表明,在这些环境里通信线上有时会寄生强静电,还有可能遭受雷电感应袭击,这种瞬间干扰对通信卡以及上、下位计算机的破坏都是具有毁灭性的,因此必须设计出周密的保护方法。当然,通信卡的成本不宜太高,而且在组成分布式通信网时越简单、越廉价越好。

2.2方案

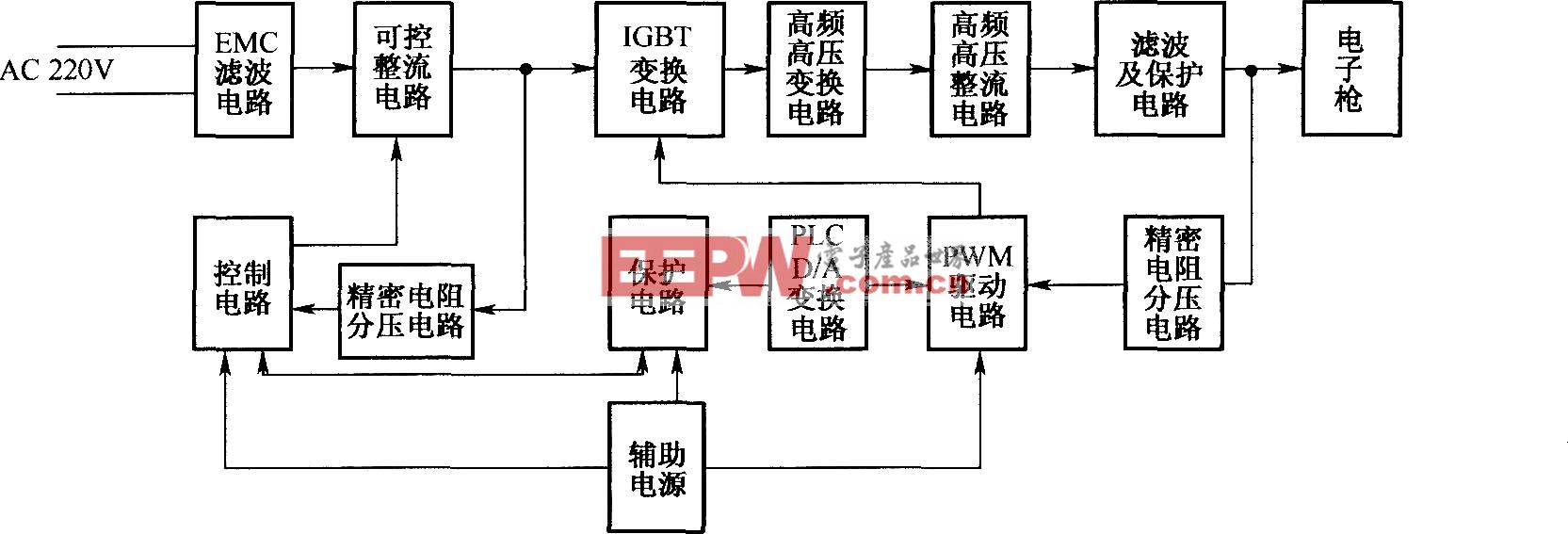

通信卡总体框图如图1所示。

方案的核心部分是可编程异步串行通信接口芯片8250,在经过与PC总线进行I/O扩展之后,8250能够读写总线上的并行数据,并可在程序的驱动下将这些数据以串行方式输入输出。输出的是TTL电平的串行信号,再经过光电耦合电路,实现信号的电气隔离,然后由RS-485收发器将这个信号变换成差分信号发送。通信卡上还有RS-232收发器,这主要是考虑到在某些特殊场合,需要与有RS-232接口的仪器交换数据而设计的。

3主要电路的实现及原理分析

3.1总线扩展及板号发生电路

图1通信卡组成框图

图2为通信卡的总线扩展及板号发生电路。图2的左半部分为IBM-PC/XT系统的I/O扩展槽,具有62个引脚,常称为PC总线或XT槽。XT槽的62个引脚分布在两面,分别标注为A1~A31和B1~B31,其中A面对应扩展卡的元件面,B面对应扩展卡的焊接面,引脚的标号从机箱的后部起始。引脚间距(中心距离)为1/10英寸,即2.54mm。XT槽的62个信号包括时钟与复位信号,20条地址线,8位双向数据线,存储器和I/O读写控制线,6个中断请求线,3个DMA总线请求线,各线均为TTL电平。此外,还有4组电源和地线等。

图2 板号扩展及板号发生电路

图2右半部分为通信卡与PC总线接口部分的电路。图中地址译码器74LS138的3个使能端

、

、E3分别接到PC机地址总线的A4、A5、A9,所以只有当A4、A5、A9分别为0、0、1时译码器才能工作。译码器的3个输入端C、B、A又分别接至A6、A7、A8,于是如表1所示当译码器工作时,A6、A7、A8为001时,输出

选中(300~30FH)地址,为101时输出

选中(340~34FH)地址。

是给8250和数据总线缓冲器74LS245提供片选;

给板号缓冲器提供片选。另外将3个低位地址A0、A1、A2直接接到8250的A0~A2,

(I/O接口读使能)接到缓冲器的方向控制和8250的

(读使能),

接到8250的DISTA(写使能)。这样计算机就可以寻址访问8250的内部寄存器,可以对扩展口进行读写。注意这种接口译码方式要避免与PC机固有地址冲突。PC机的地址分配见表2。

3.2可编程异步通信接口INS8250

INS8250是可编程的异步通信接口芯片,它的引脚及接线如图3所示,主要性能如下:

(1)完全双工、双缓冲器发送和接收的异步通信接口电路。

(2)通信波特率:50~9600,共分为50种。

(3)每字符可传5~8位。

(4)停止位可编程选择为1、1.5和2位。

(5)可产生中止字符(输出连续低电平,以通知对方中止通信)。

(6)可进行奇偶校验,可选择奇校验或偶校验。

(7)出错检测,具有奇偶、溢出和帧错误等检测电路。

(8)片内具有优先权中断控制逻辑,具有很强的中断控制功能。

简而言之,该电路可以在程序的控制下,把数据总线上的并行数据按设定从SOUT端串行发出,或把SIN端的串行数据按设定接收并变为可被总线读取的并行数据。至于芯片的内部结构及详细的程序控制方法,请参看参考文献1。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码