usb接口电路图大全(DS2490S/PDIUSBD12)

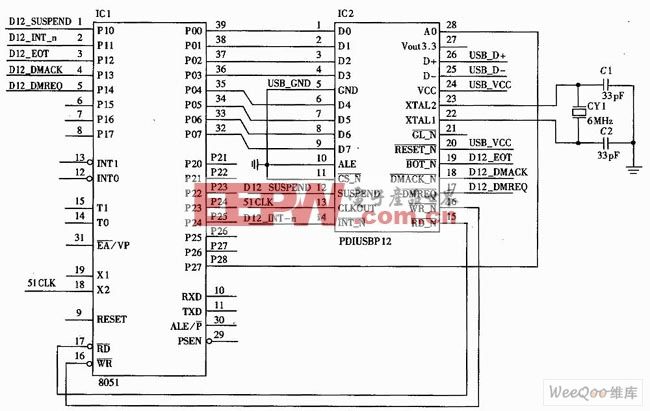

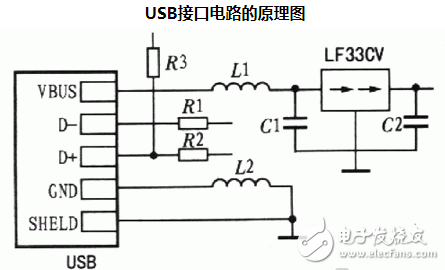

usb接口电路图(一)

USB接口电路的原理图中,R3是上拉电阻器,它可使USB口的D+端上拉到DS2490S的VB端,表示USB主机系统是高速设备,同时这个上拉电阻器告诉主机有USB设备插入。该上拉电阻器的设置对适配器的影响很大,它的负载值和1-Wire网络的总长决定1-Wire总线电压上升到5 V的速度。经过实验测试选择R3的阻值为27 Ω±lO%。R1、R2为USB数据线保护电阻器。L、L2具有禁止高频干扰并且减弱EMI辐射的功能。LF33CV为3.3 V电压稳压器,与周围元件C1、C2组成强上拉部分,给EEPROM或温度传感器等器件提供额外的电源。

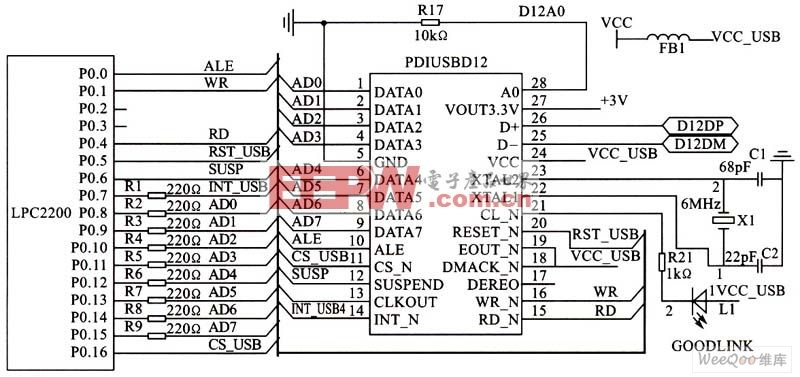

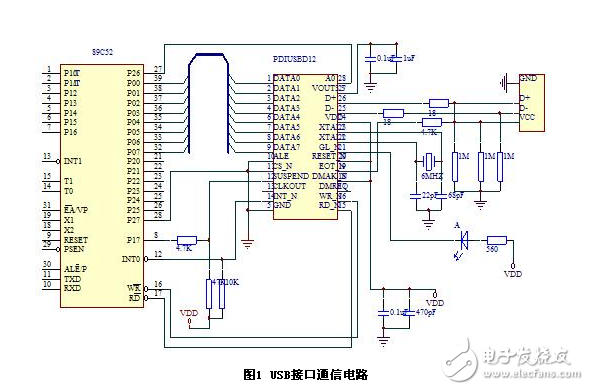

usb接口电路图(二)

采用PDIUSBD12芯片,这是一种价格便宜、功能完善的并行接口芯片,它支持多路复用、非多路复用和 DMA并行传输。PDIUSBD12接口芯片遵从协议USB1.1,适合于不同用途的传输类型。PDIUSBD12需要外接微控制器(MCU)来进行协议处理和数据交换,它对MCU没有特殊要求,而且接口方便灵活,因此设计师可以选用自己熟悉的MCU对芯片进行控制,也可利用Philips公司的固件 (firmware)结构来缩短开发时间、降低风险、减小投资。

性能特点

PDIUSBD12除了具有USB设备的一般特性外,还具有如下特点:

(1)是一种高性能的USB接口芯片,其内部集成有 SIE(Serial Interface Engine)、320字节的FIFO、收发器和电压调节器。

(2)适用于大部分设备类规范。可与任何外部微控制器/微处理器实现高速并行接口,其速度可高达2Mbit/s。

(3)可进行完全独立的DMA操作。

(4)主端点配置有双缓冲,因而可提高数据的吞吐量、减小数据传输时间,轻松实现数据的实时传输。

(5)当采用同步传输方式时,数据的传输速度为1Mbit/s;而采用批量传输方式的速度为1Mbyte/s。在使用上述方式进行数据传输时,可方便地使用多种中断方式。

(6)带有可编程的时钟输出,与USB总线的连接可通过软件来控制(Soft Connect TM)。

(7)有两种工作电压可供选择:分别为3.3±0.3V和3.6~5.5V。

(8)输出和数据传输状态可通过USB连接指示灯来监控。

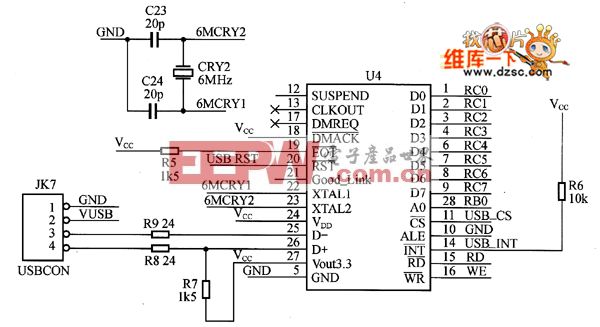

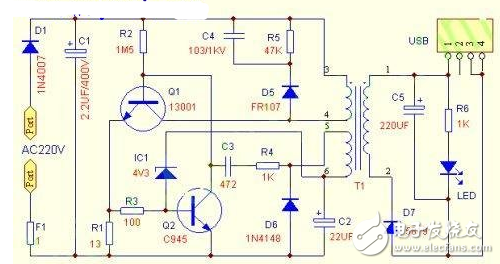

usb接口电路图(三)

图中用1欧的电阻F1起到保险丝的作用,用一个二极管D1完成整流作用。接通电源后,C1会有300V左右的直流电压,通过R2给Q1的基极提供电流,Q1的发射极有R1电流检测电阻R1,Q1基极得电后,会经过T1的(3、4)产生集电极电流,并同时在T1的(5、6)(1、2)上产生感应电压,这两个次级绝缘的圈数相同的线圈,其中T1(1、2)输出由D7整流、C5滤波后通过USB座给负载供电;其中T1(5、6)经D6整流、C2滤波后通过IC1(实为4.3V稳压管)、Q2组成取样比较电路,检测输出电压高低;其中T1(5、6)、C3、R4还组成Q1三极管的正反馈电路,让Q1工作在高频振荡,不停的给T1(3、4)开关供电。当负载变轻或者电源电压变高等任何原因导致输出电压升高时,T1(5、6)、IC1取样比较导致Q2导通,Q1基极电流减小,集电极电流减小,负载能力变小,从而导致输出电压降低;当输出电压降低后,Q2取样后又会截止,Q1的负载能力变强,输出电压又会升高;这样起到自动稳压作用。

本电路虽然元件少,但是还设计有过流过载短路保护功能。当负载过载或者短路时,Q1的集电极电流大增,而Q1的发射极电阻R1会产生较高的压降,这个过载或者短路产生的高电压会经过R3让Q2饱和导通,从而让Q1截止停止输出防止过载损坏。因此,改变R1的大小,可以改变负载能力,如果要求输出电流小,例如只需要输出5V100MA,可以将R1阻值改大。当然,如果需要输出5V500MA的话,就需要将R1适当改小。注意:R1改小会增加烧坏Q1的可能性,如果需要大电流输出,建议更换13003、13007中大功率管。

C4、R5、D5起什么作用呢?T1变压器是电感元件,Q1工作在开关状态,当Q1截止时,会在集电极感应出很高的电压,这个电压可能高达1000伏以上,这会使Q1击穿损坏,现在有了高速开关管D5,这个电压可以给C4充电,吸收这个高压,C4充电后可以立即通过R5放电,这样Q1不会因集电极的高电压击穿损坏了,因此,这三个元件如有开关或者损坏,Q1是非常危险的,分分秒秒都可能会损坏。

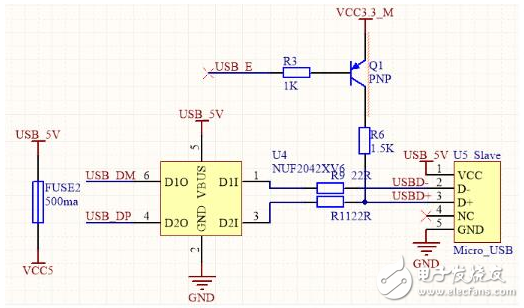

usb接口电路图(四)

当F105配置为时, PA9/OTG_FS_VBUS是用来检测presense USB主机的。设计评估显示PA9/OTG_FS_VBUS引脚通过一个零欧姆电阻连接到5 VBUS 。有这种方法有两个潜在的问题。该第一电势的问题是, PA9/OTG_FS_VBUS输入,虽然它是5V容限,可能损坏(如每ST支持)如果连接到5V时的STM32F105 VDD为0V。这可能发生在两个自供电和主机供电的应用。当电源关闭/拔出,而USB连接到主机仍处于活动状态,这将发生在一个自供电的应用。这将发生在一个主机供电应用过程中所花费的VDD稳压器来达到它的稳压输出电压所需的时间。一些设计师建议之间的PA9/OTG_FS_VBUS引脚和5V VBUS串联电阻。

1、Vcc脚会与主机的5v电源接通。子机这边可以悬空,也可以做供电,还可以做连接识别(电阻分压之后高即为连接主机)。

2、存在D+上拉或者D-上拉两种情况,告诉主机当前的USB通信速度,FS或者HS。

3、电阻接IO上拉,往往是子机为了实现自我复位,通知主机重新识别,效果等同于拔掉USB接头重新插入一次。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码