异步DSP设计:更低功耗,更高性能

目前,处理器性能的主要衡量指标是时钟频率。绝大多数的集成电路 (IC) 设计都基于同步架构,而同步架构都采用一致的时钟。这种架构非常普及,许多人认为它也是数字电路设计的途径。然而,有一种截然不同的设计技术即将走上前台:异步设计。

这一新技术的主要推动力来自硅技术的发展状况。随着硅产品的结构缩小到 90 纳米以内,降低功耗就已成为首要事务。异步设计具有功耗低、电路更可靠等优点,被看作是满足这一需要的途径。

异步技术由于诸多原因曾经备受冷落,其中重要的是缺乏标准化的工具流。IC 设计团队面临着巨大的压力,包括快速地交付设备,使用编程语言和标准的事件驱动架构 (EDA) 工具,帮助实施合成、定时和验证等任务。如果异步设计可以使用此类工具,那么可以预计将会出现更多采用异步逻辑组件的设备。

在过去,小型异步电路仅用作同步电路的补充。仅仅在近,新发布的商用设备才主要基于异步设计。但是此类设备主要针对小众市场,如要求超低功耗和稳定电流的嵌入式感应器。

我们正在见证一款完全基于异步逻辑的通用数字信号处理器(DSP)横空出世。无论是 IC 设计人员还是终用户,它带来的好处数不胜数。

同步与异步

目前的数字设计事实上采用的是同步设计技术。由于历史原因,这种方法得到了改良,设计工具也不断演化。目前有一种标准流以语言为基础,可实现快速开发。同步设计还可以轻松地扩展设备性能。设计人员只须提高时钟频率,就能使设计变得更快。

同步法包括建立功能模块,每个模块由一个按时钟信号控制的有限状态机(FSM)驱动。触发器被用于存储当前状态。当接收到时钟信号时,触发器将更新所存储的值。

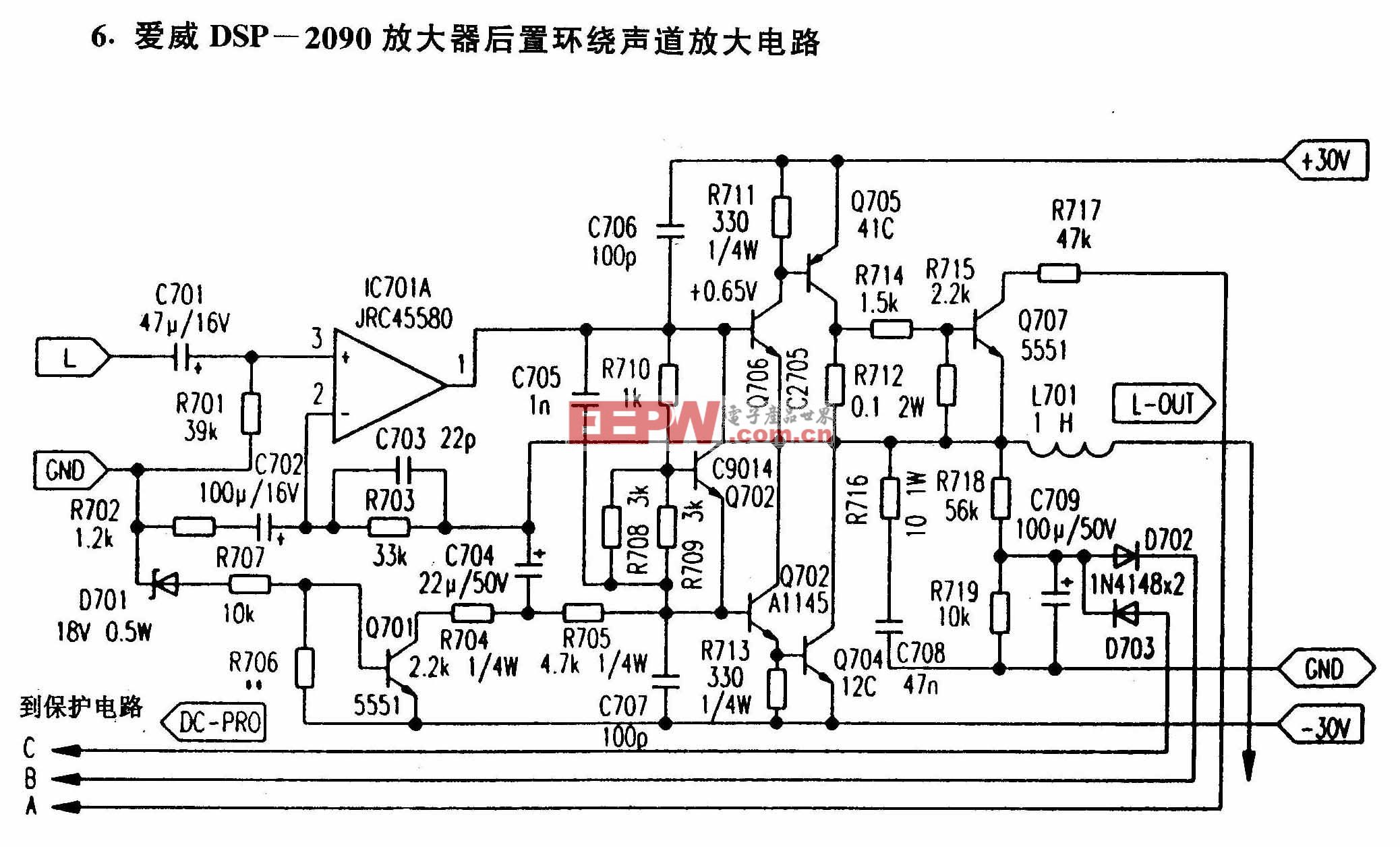

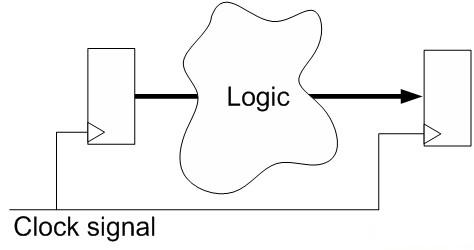

在 DSP 的设计过程中,逻辑阶段必不可少。这些阶段实施操作并将结果传递到下一阶段。下图表示单个阶段的简单模型。异步逻辑用于在两个触发器之间计算电路的新状态。例如,该逻辑云可执行加法或乘法。

Logic 逻辑

Clock signal 时钟信号

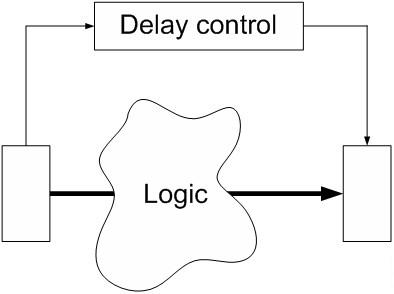

对于异步 DSP ,逻辑阶段被调整以消除时钟。下图显示了这种DSP 架构的基本构造。不是由时钟控制门闩线路,而实际上是传递了一个完成信号给下一逻辑阶段。根据逻辑云所执行的操作,在恰当时候可生成完成信号。

这种本地延迟控制可以保证电路的稳定。由于控制电路时间的逻辑就在本地,它就可以相应地改变电压、处理速度和温度。

Delay control 延时控制

Logic 逻辑

异步设计有许多种不同的途径,而前提是电路不受单一时钟控制。多数情况下,异步逻辑被用于通过专门的电路设计来解决具体问题。但是,异步逻辑也可用作完整DSP的基础,而不仅仅是设计中偶尔需要的一种工具。其好处包括降低功耗、可靠性提高以及电磁干扰(EMI)低。

异步设计的好处

采用异步设计的理由非常吸引人。在正确使用中,这种方法可以实现更低的能耗、更好的EMI 性能;由于消除了时钟偏差,真正地简化了设计。

功耗更低:与同步DSP相比,异步DSP重要的好处就是功耗更低。事实上,这种异步的能效数量级高于的同步DSP。

随着硅产品尺寸的缩小,功耗问题越来越重要。由于线路长度为线性而面积为平方,单位面积硅功耗将随着尺寸的缩减而增加。目前,通过降低电压,数字设计人员已经成功地解决了这个问题;但由于电压阈值的限制,目前的半导体技术无法再有效地降低电压。要想有效地利用新增加的功能,必须降低各个功能的功耗。

在CMOS 技术中,门电路切换状态时将消耗能量。在同步电路中,时钟需要进行多次切换,从而造成功耗。在设备或者设备的分区中分配时钟需要时钟缓冲器。时钟缓冲器必须足够大,以确保限度降低时钟偏差。换言之,电路中的所有点必须同时接受时钟变换。时钟分配通常被称为时钟树(Clock Tree),一般会消耗几乎一半的总系统能量。树底部的时钟缓冲器具有相当大的扇出量和很大的体积,因此功耗较高。

目前开发有多种技术消除切换逻辑的能耗,如时钟门控。迄今为止,这些技术都无法实现异步设计的更低功耗。

时钟门控对于异步电路来说并非必备。实际上,异步电路仅在执行有效操作时耗能。换言之,无需增加电路的情况下,异步电路的功耗将根据所提供的性能相应地增加。这意味着,不需要更多调整,这种设备就拥有低待机电流,其功耗也将随实际提供的性能而增加。

切换性能更出色:除了功耗更低外,含有异步逻辑的设备还将拥有极低的EMI。无论是IC设计人员还是终用户,它带来的好处数 不胜数。

或当地时钟是影响EMI 的一个因素。由于同步电路中的时钟需要同时随处进行切换,因此同步设备所发出的 EMI 在特定频率时将拥有相当明显的峰值。

高速设备所发出的 EMI 噪音将进入 PCB 的电源层。随后该噪音将出现在外部 I/O 或布线中,在线缆中引起多余且通常超标的辐射。道防线采用解耦电容,而更昂贵的屏蔽或共模扼流线圈将用作一道防线。

电源层上的EMI也使得电源的设计更加复杂。对于高速运转的同步电路,电源必须经过过滤或过量储备,以符合电源层上所产生的电压尖脉冲。

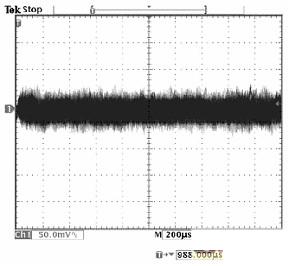

这些噪音和电源问题加在一起,增加了设计人员的设计难度,尤其在特定设计中使用大量高速 DSP 时。通过消除对于同步时钟的需要,异步逻辑设计可以减轻或解决这些问题。可以显着地降低 EMI,使 PCB 设计更简单并提高系统的可靠性。异步电路电源波纹的缺失相当引人注目,它表明可以获得更好的切换性能。

下列图显示了同步和异步DSP电源噪音之间的典型差异。这些图是示波器的屏幕截图,测量了高性能DSP在电源层上产生的噪音。

图 1:同步DSP电压波纹

图 2:异步DSP电压波纹

在IC设计人员眼中,更出色的切换性能代表更可靠的电路。电路同时发生大规模切换时,将产生非常大的瞬时电流。在设备的电网上显示为IR降。这意味着电网的某一区域在此时的电压较低。这是意料之中的正常情况,通常都通过设计验证来确保电网能承受预计的电压下降。有时这也是一种限制因素,妨碍设计人员在逻辑的特定区域进行进一步设计。

消除时钟偏差:采用异步设计还有很多原因。低于90纳米的硅片是生产的趋势。这可以从硅制造商大力投入以纠正一系列问题上得以证明。他们已着手开发干涉计量学(Interferometric Metrology)等技术,

尽量使光罩的特征尺寸小于当前的曝光波长。

由于这些变量会提高设备的偏差量,因此在过程中控制它们非常重要。时钟偏差被定义为时钟信号到达电路中不同点的时间差。

由于相同时钟上的所有逻辑必须有序地运行,因此时钟偏差必须保持在水平,以确保电路正确运行。设备的时钟频率越高,可允许的偏差越小。

随着特征尺寸的减少,时钟偏差的问题将更加严重。相比以前,特定晶片中将分为“慢速”芯片和“快速”芯片;由于密度大幅增加,单个芯片中的变量也将有所体现。这种状况的性质对于大型单片同步设备意义非常重大。

采用异步 DSP 可避免此类问题。DSP 基于小型自计时电路。因此所有定时对于该逻辑块相关的小区域都是本地的。

稳定性更高:半导体主要受三大物理属性影响:制作流程速度、电源电压电平和温度。如果这些特征发生任何变化,将造成晶体管运转更快或更慢的情况。

同步电路必须在上述参数的和差状态值下进行静态时序分析(static timing analysis),以确保设备工作正常。换而言之,同步电路有一个可以使电路停止工作的“切断点”。

由于异步电路是自计时电路,因此它们在物理特征变化时只须加速或减速。因为控制自计时的逻辑与处理逻辑处于相同区域,所以温度和电压等环境变化都会对两者造成影响。所以,异步电路针对抵抗动态电压下降等瞬时变化的抗影响性能更好,还将根据长期温度和电压变化进行自动调整。

横空出世:通用异步 DSP

由于成功采用异步设计技术的各种设备不断出现,异步设计正受到越来越多的关注。异步逻辑的优点众所周知。包括低功耗和更稳定的设计等等。

直到近,异步电路仅仅在非常必要时才使用。由于学术界的偏见,它们通常被视为边缘产品。现在,许多商用设备已经开发了上述针对各类小众市场的功能。

完全基于异步逻辑的通用 DSP 的出现表明,现有的工具、技术和知识创造的商用产品可应用于更大的客户群体。更吸引人的是,该设备可与任何现有DSP一样进行同样的编程和操作。也就是说,这个解决方案在丝毫不影响可用性的基础上,实现了异步技术的所有优点。

关键词: DSP

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码