具有高功率因数和超宽输出电压的LED驱动器

2. 具有较宽输出电压范围的 LED 驱动器

2.2. 系统设计

本小节介绍基于FL7733的单级反激式 LED 驱动器的设计步骤。选择了50 W 离线 LED 驱动器作为设计示例。设计指标如下:

● 输入电压范围: 90 ~ 277 VAC、 50 ~ 60 Hz

● 标称输出电压和电流: 50 V/1.0 A

● 工作输出电压: 12 V ~ 50 V

● 频率: 88%

● 工作开关频率: 65 kHz

● 占空比: 40%

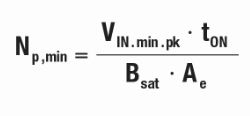

初级匝数由法拉第定律确定。Np,min是由初级绕组两端的线路输入电压峰值和导通时间固定。可避免磁芯饱和的变压器初级端匝数可由下式给出:

(3)

(3)

其中Ae为磁心横截面积(以 mm2为单位),而 Bsat为饱和通量密度(以特斯拉为单位)。

(4)

(4)

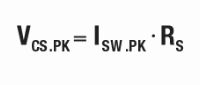

根据等式(3),初级到次级匝比由检测电阻和输出电流确定如下:

(5)

(5)

(6)

(6)

(7)

(7)

由于饱和通量密度随着温度的升高而减小,如果变压器用于封闭外壳内,应考虑高温特性。

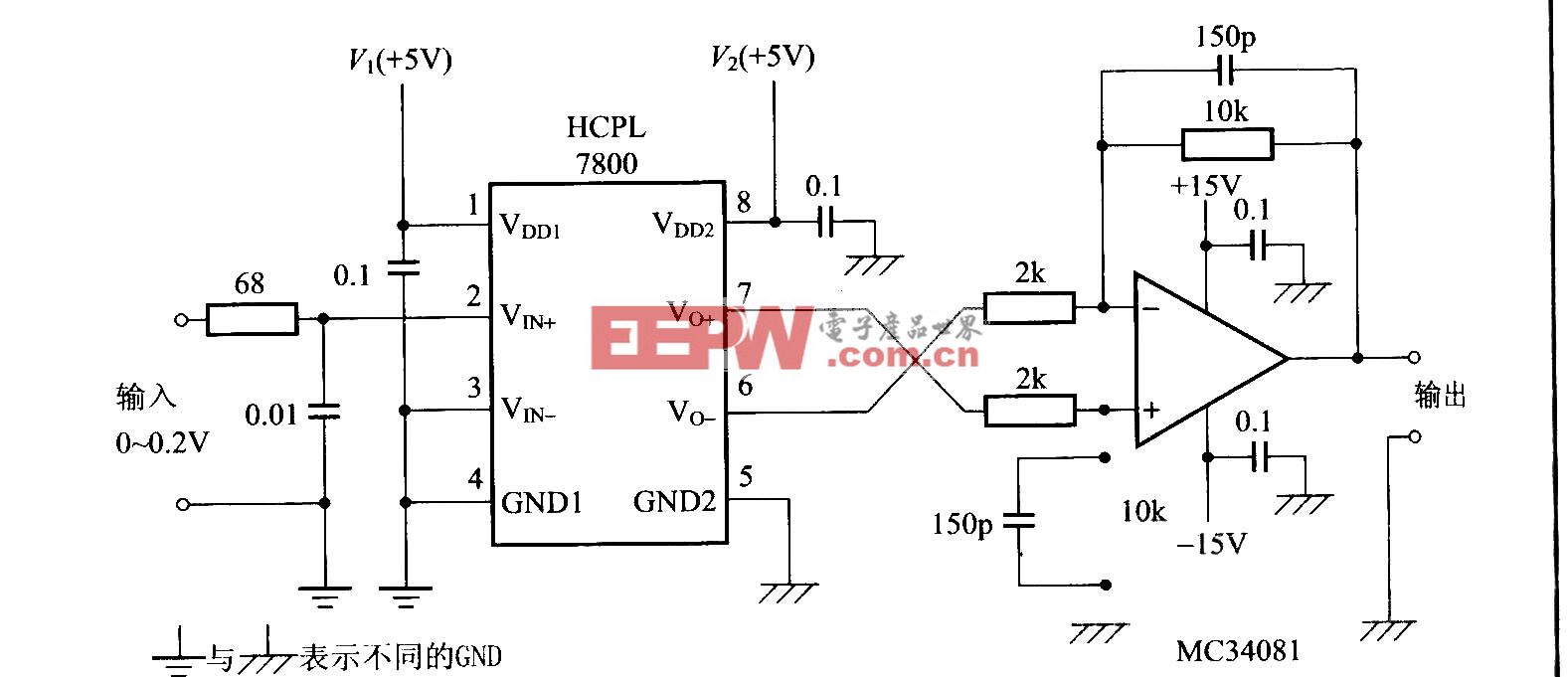

图 3. 实现较宽输出电压范围的 VS 电路

选择 R1 和 R2的个考虑因素是将 VS设置为 2.7 V,以确保额定输出功率下能够以高频率运行。第二个考虑因素是 VS 消隐。输出电压由辅助绕组和连接到 VS 引脚的电阻分压器检测。然而,在不包含 DC 母线电容器的单级反激式转换器中,在低线路电压下由于较小的 Lm 电流会引起 VS 电压检测错误,辅助绕组电压无法箝位至反射的输出电压。在线路电压过零点,频率快速下降,可能导致 LED 灯闪烁。为了在整个正弦线路电压范围内维持恒定频率,VS 消隐会通过检测辅助绕组在低于特定线路电压 VIN.bnk时禁用 VS 采样。第三个考虑因素是 VS 电平,应该介于 0.6 V 与 3 V 之间,以避免在宽输出应用中触发 SLP 和 VS OVP。

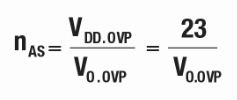

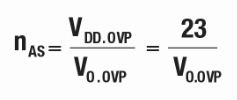

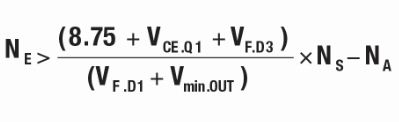

由于 FL7733 的 VDD工作范围是 8.75 ~ 23 V,如果输出电压低于 VOUT-UVLO (8.75×NS /NA),应该通过触发 UVLO 关断 MOSFET开关。因此,应该在较宽的输出电压范围内12 ~ 50不触发 UVLO,从而提供合理的 VDD。通过添加外部绕组 NE和包含电压调节器的 VDD电路,可以提供VDD。NE的设计应该确保以输出电压 (Vmin.OUT) 提供 VDD时,不会触发 UVLO。外部绕组 NE可通过下式确定:

(9)

(9)

其中,VCE.Q1是 Q1 的集电极-发射极饱和电压,VF.D3是 D3 的正向电压,VF.D1是输出电压下 D1的正向电压。

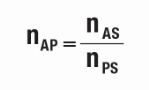

(10)

(10)

其中,VIN.bnk是实现 VS 消隐的线路电压电平,而IVS.bnk是实现 VS 消隐的电流电平。

(11)

(11)

2.2. 设计测试结果

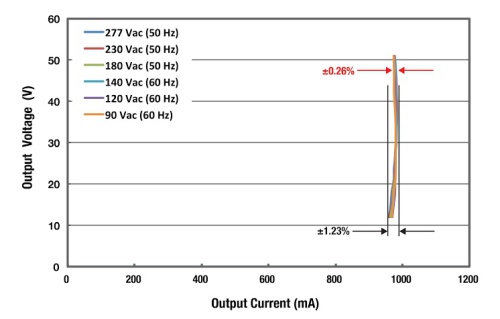

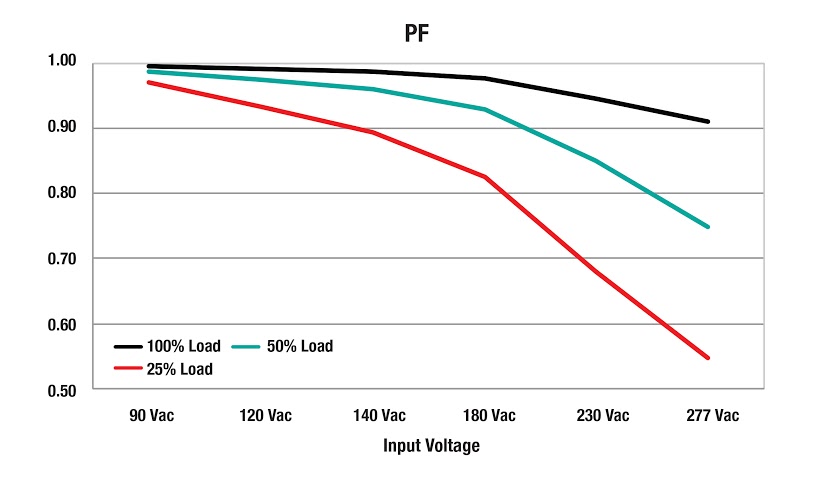

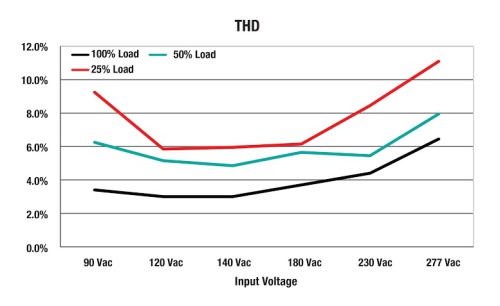

为了展示本应用指南中所介绍设计步骤的有效性,构建并测试了设计示例中介绍的转换器。图 4显示在整个线路和输出电压范围内测得的 CC 容差。额定输出电压下通用线路上的 CC 低于 ±0.26 % 而整个线路和输出电压范围 (12 V ~ 51 V) 内的总 CC 调节是 ±1.23%。图 5和图 6 显示分别在各种负载条件下测得的 PF和 THD 性能。

图 4. 整个输入和输出电压范围内的 CC 性能

图 5. 根据负载条件变化的 PF 性能与输入电压

图 6. 根据负载条件变化的 THD 性能与输入电压

3. 结论

为了针对各种 LED 灯规范和 LED 特性提高灵活性和兼容性,本文介绍了覆盖较宽输出电压范围的 LED 驱动器。Fairchild 的 PSR 控制器 FL7733 提供出色的高 PF 和低 THD 性能,并在非常宽的输出电压范围内提供恒流调节。此外,本文中设计的 LED 驱动器可用于具有简单设计和较低成本的各种 LED 照明灯具。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码