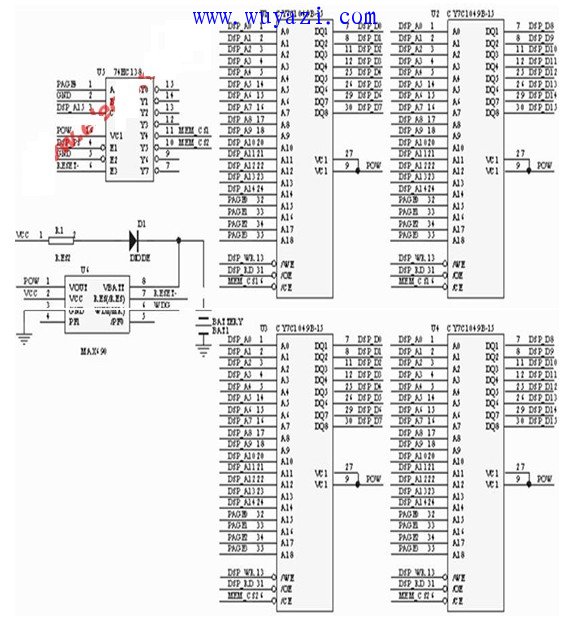

信息存储器模块的电路图

作者:dolphin

时间:2017-09-15

由于ARM的读写速度很快,防止ARM访问片外存储单元出现“瓶颈”现象,应选用快速存储器芯片,不需要ARM插入等待状态,只要将存储器芯片的地址线、数据线与MC9328MX1的数据线、地址线相连,再辅以必要的控制信号和译码电路,就可以使ARM全速运行。在系统中,我们选用4片CY7C1049B-15 SRAM(512K X 8bits)用作信息存储器,再附加上掉电保护电路,将其构成1M字存储单元。它在系统中分配的存储地址为8000H-FFFFH单元(注:0000H-7FFFH为其它存储用),故1M字存储单元共可分成1M/32K=32个页面。其中页面寄存器利用可编程器件FPGA设计实现。信息存储器模块的电路图如下图所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码