TI TMS320C5515 心电图(ECG)MDK开发方案

作者:angelazhang

时间:2015-08-06

TI 公司的TMS320C5515 DSP医疗开发套件(Rev. B)支持完整的医疗应用开发如心电图(ECG),数字听诊器和脉冲血氧计等。典型应用包括模拟前端(AFE),信号处理算法以及用户控制与交互。TMS320C5515是低功耗定点数字信号处理器(DSP),采用TMS320C55x™ DSP处理器核,内核工作电压1.05V/1.3V,I/O电压为1.8/2.5/2.75/3.3V。

16.67/13.33/10/8.33-ns 指令周期,时钟速率60-,75-,100-,120-MHz,具有320KB 片内RAM。本文介绍了 TMS320C5515主要特性,方框图以及医疗开发套件(MDK)硬件方框图,ECG 前端方框图,前端板电路图详细电路图和所用材料清单(BOM)。

ECG Implementation on the TMS320C5515 DSP Medical Development Kit (Rev. B)

The TMS320C5515 Fixed-Point Digital Signal Processor is a member of TI’s TMS320C5000™ fixed-point Digital Signal Processor (DSP) product family and is designed for low-power applications.

The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32-bit data read bus and two 16-bit data read buses, two 16-bit data write buses, and additional buses dedicated to peripheral and DMA activity. These buses provide the ability to perform up to four 16-bit data reads and two 16-bit data writes in a single cycle. The device also includes four DMA controllers, each with 4 channels, providing data movements for 16-independent channel contexts without CPU intervention. Each DMA controller can perform one 32-bit data transfer per cycle, in parallel and independent of the CPU activity.

The C55x CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit x 17-bit multiplication and a 32-bit add in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the Address Unit (AU) and Data Unit (DU) of the C55x CPU.

The C55x CPU supports a variable byte width instruction set for improved code density. The Instruction Unit (IU) performs 32-bit program fetches from internal or external memory and queues instructions for the Program Unit (PU). The Program Unit decodes the instructions, directs tasks to the Address Unit (AU) and Data Unit (DU) resources, and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution of conditional instructions.

The general-purpose input and output functions along with the 10-bit SAR ADC provide sufficient pins for status, interrupts, and bit I/O for LCD displays, keyboards, and media interfaces. Serial media is supported through two MultiMedia Card/Secure Digital (MMC/SD) peripherals, four Inter-IC Sound (I2S Bus™) modules, one Serial-Port Interface (SPI) with up to 4 chip selects, one I2C multi-master and slave interface, and a Universal Asynchronous Receiver/Transmitter (UART) interface.

The device peripheral set includes an external memory interface (EMIF) that provides glueless access to asynchronous memories like EPROM, NOR, NAND, and SRAM, as well as to high-speed, high-density memories such as synchronous DRAM (SDRAM) and mobile SDRAM (mSDRAM). Additional peripherals include: a high-speed Universal Serial Bus (USB2.0) device mode only, and a real-time clock (RTC). This device also includes three general-purpose timers with one configurable as a watchdog timer, and an analog phase-locked loop (APLL) clock generator.

In addition, the device includes a tightly-coupled FFT Hardware Accelerator. The tightly-coupled FFT Hardware Accelerator supports 8 to 1024-point (in power of 2) real and complex-valued FFTs. Furthermore, the device includes three integrated LDOs (DSP_LDO, ANA_LDO, and USB_LDO) to power different sections of the device. The DSP_LDO can provide 1.3 V or 1.05 V to the DSP core (CVDD). To allow for lowest power operation, the programmer can shutdown the internal DSP_LDO cutting power to the DSP core (CVDD) while an external supply provides power to the RTC (CVDDRTC and DVDDRTC). The ANA_LDO is designed to provide 1.3 V to the DSP PLL (VDDA_PLL), SAR, and power management circuits (VDDA_ANA). The USB_LDO provides 1.3 V to USB core digital (USB_VDD1P3) and PHY circuits (USB_VDDA1P3). The RTC alarm interrupt or the WAKEUP pin can re-enable the internal DSP_LDO and re-apply power to the DSP core.

The device is supported by the industry’s award-winning eXpressDSP™, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, Texas Instruments’ algorithm standard, and the industry’s largest third-party network. Code Composer Studio IDE features code generation tools including a C Compiler and Linker, RTDX™, XDS100™, XDS510™, XDS560™ emulation device drivers, and evaluation modules. The device is also supported by the C55x DSP Library which features more than 50 foundational software kernels (FIR filters, IIR filters, FFTs, and various math functions) as well as chip support libraries.

TMS320C5515主要特性:

HIGHLIGHTS:

High-Perf/Low-Power, C55x™ Fixed-Point DSP

16.67/13.33/10/8.33-ns Instruction Cycle Time

60-, 75-, 100-, 120-MHz Clock Rate

320K Bytes On-Chip RAM

16-/8-Bit External Memory Interface (EMIF)

Two MultiMedia Card/Secure Digital I/Fs

Serial-Port I/F (SPI) With Four Chip-Selects

Four Inter-IC Sound (I2S Bus™)

USB 2.0 Full- and High-Speed Device

LCD Bridge With Asynchronous Interface

Tightly-Coupled FFT Hardware Accelerator

10-Bit 4-Input SAR ADC

Real-Time Clock (RTC) With Crystal Input

Four Core Isolated Power Supply Domains

Four I/O Isolated Power Supply Domains

Three integrated LDOs

Industrial Temperature Devices Available

1.05-V Core, 1.8/2.5/2.75/3.3-V I/Os

1.3-V Core, 1.8/2.5/2.75/3.3-V I/Os

图1。TMS320C5515方框图

医疗开发套件(MDK)

A number of emerging medical applications such as electrocardiography (ECG), digital stethoscope, and pulse oximeters require DSP processing performance at very low power. The TMS320C5515 digital signal processor (DSP) is ideally suited for such applications. The C5515 is a member of TI’s C5000™ fixed-point DSP platform. To enable the development of a broad range of medical applications on the C5515, Texas Instruments has developed an MDK based on the C5515 DSP. A typical medical application includes:

• An analog front end, including sensors to pick up signals of interest from the body

• Signal processing algorithms for signal conditioning, performing measurements and running analytics on measurements to determine the health condition

• User control and interaction, including graphical display of the signal processing results and connectivity to enable remote patient monitoring

The MDK is designed to support complete medical applications development. It includes the following elements:

• Analog front-end boards (FE boards) specific to the key target medical applications of the C5515 (ECG, digital stethoscope, pulse oximeter), highlighting the use of the TI analog components for medical applications

• C5515 DSP evaluation module (EVM) main board

• Medical applications software including example demonstrations

图2。医疗开发套件(MDK)硬件方框图

MDK Hardware Overview

An electrocardiogram (ECG/EKG) is the recording of the electrical activities of the heart and is used in the investigation of heart disease. The electrical waves can be measured by selectively placed electrodes (electrical contacts) on the skin.

医疗开发套件(MDK)ECG主要特性:

The key features of the MDK ECG system are:

• 12 lead ECG output using 10 electrode input

• Defibrillator protection circuitry

• Diagnostic quality ECG with bandwidth of 0.05 Hz to 150 Hz

• Heartbeat rate display

• Leads off detection

• Real-time 12 lead ECG waveform display on EVM LCD screen, one lead selectable at a time

• Zoom option for the Y-axis (amplitude) on EVM LCD screen

• Real-time 12 lead ECG waveform display on PC, three leads at a time

• Zoom function on X-axis (time) and Y-axis (amplitude) on PC application

• Freeze screen option on PC Application

• Recording of ECG data and offline view option of recorded ECG data on PC application Several elements of the MDK ECG system are:

• C5515 EVM

• ECG front-end board

• ECG cable

1)C5515 EVM

The EVM comes with a full compliment of on-board devices that suit a wide variety of application environments.

For further details on the C5515 EVM, see the Medical Devlopment Kit provided with your EVM.

Key components and interfaces of the C5515 EVM used in the MDK ECG system include:

• Texas Instrument’s TMS320C5515 operating at 100 MHz

• User universal serial bus (USB) port via the C5515

• Inter-integrated circuit (I2C) /serial peripheral interface (SPI) electrically erasable programmable read-only memory (EEPROM)

• External memory interface (EMIF), I2C, universal asynchronous receiver/transmitter (UART), SPI interfaces

• SAR

• External IEEE Standard 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture (JTAG) emulation interface

• Embedded JTAG controller

• Color LCD display

• Keys (user switches)

The EVM operates from a + 5 V external power supply or battery and is designed to work with TI’s Code Composer Studio™ integrated development environment (IDE). Code Composer Studio communicates with the EVM board through the external emulator, or on-board emulator.

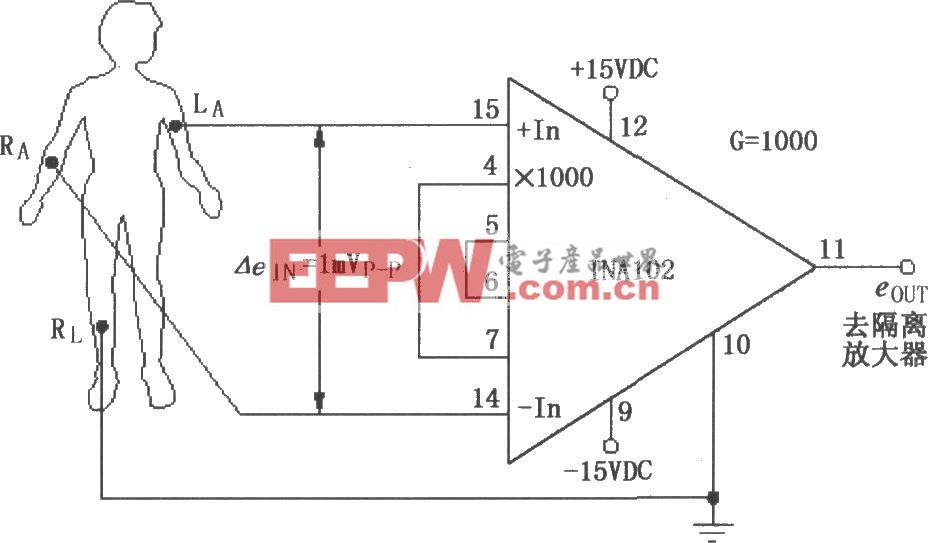

2)ECG Front-End Board

Figure 3 shows the ECG front-end board. The potentials captured by the electrodes are passed through

the defibrillator protection (DP) circuit in the ECG front-end board. Then, the front end board derives 8 out

of 12 ECG leads and provides the digital input to the DSP subsystem. The front-end board can be

interfaced with the EVM board through a universal front-end connector. The front-end board is interfaced

with and powered by the C5515 EVM board through the universal front-end connector by using I2C and

I2S interfaces.

The 16 channel analog-to-digital converter (ADC) (ADS1258) on the front-end board is configured for 500

Hz sampling with 24-bit data resolution. ADC is interfaced with the C5515 using the SPI bus.

图3。ECG板外形图

3)ECG Cable

The ECG cable consists of four limb and six chest electrodes. This cable is connected to the front-end board through the DB15 connector. The ECG electrodes pick up ECG signals from the ECG simulator/patient and send them to the ECG front-end board; an off-the-shelf ECG cable is used. For more details regarding ECG cable

图4。安装在C5515 EVM的ECG前端外形图

图5。ECG 前端方框图

图6。DSP软件架构图

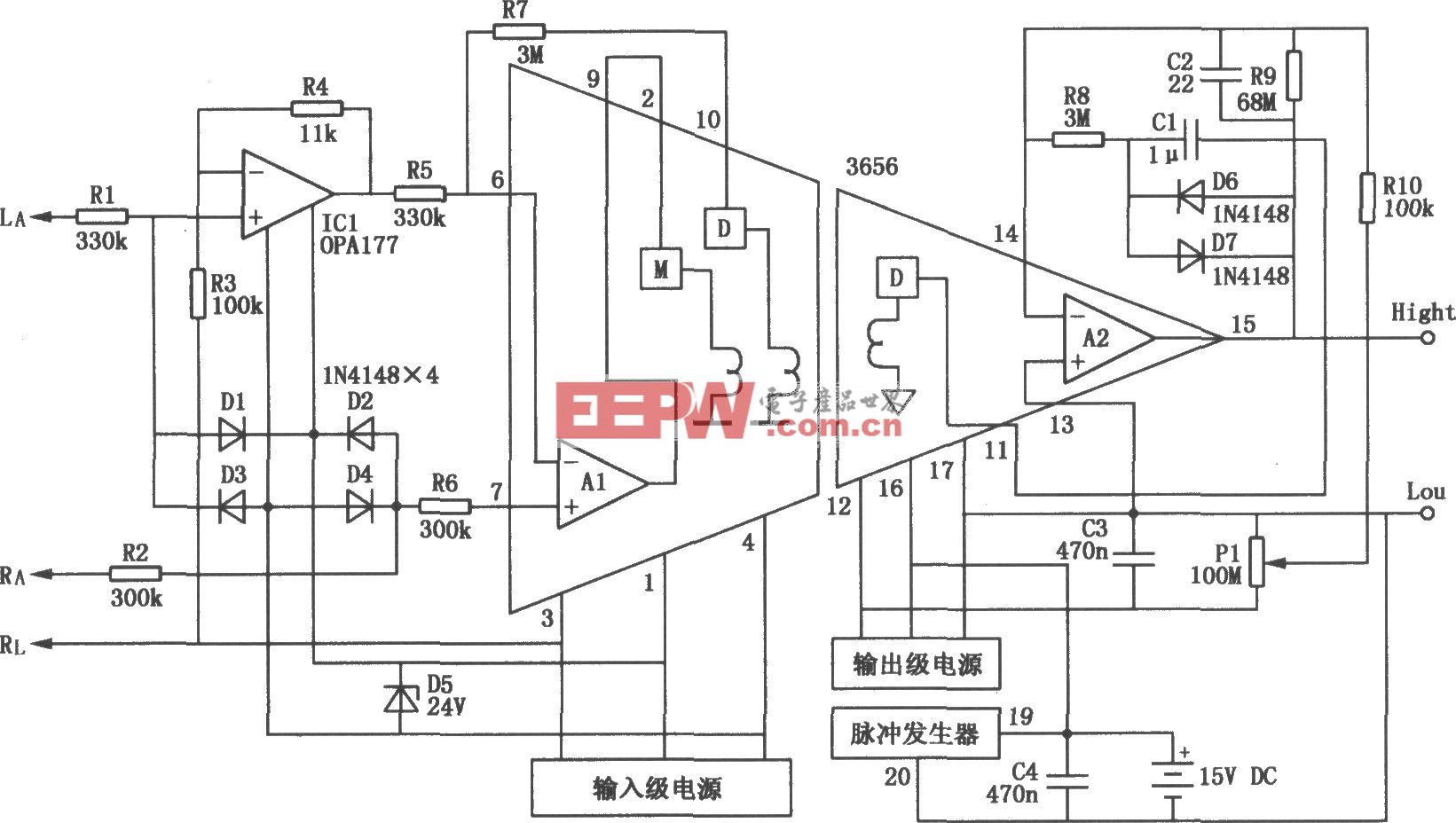

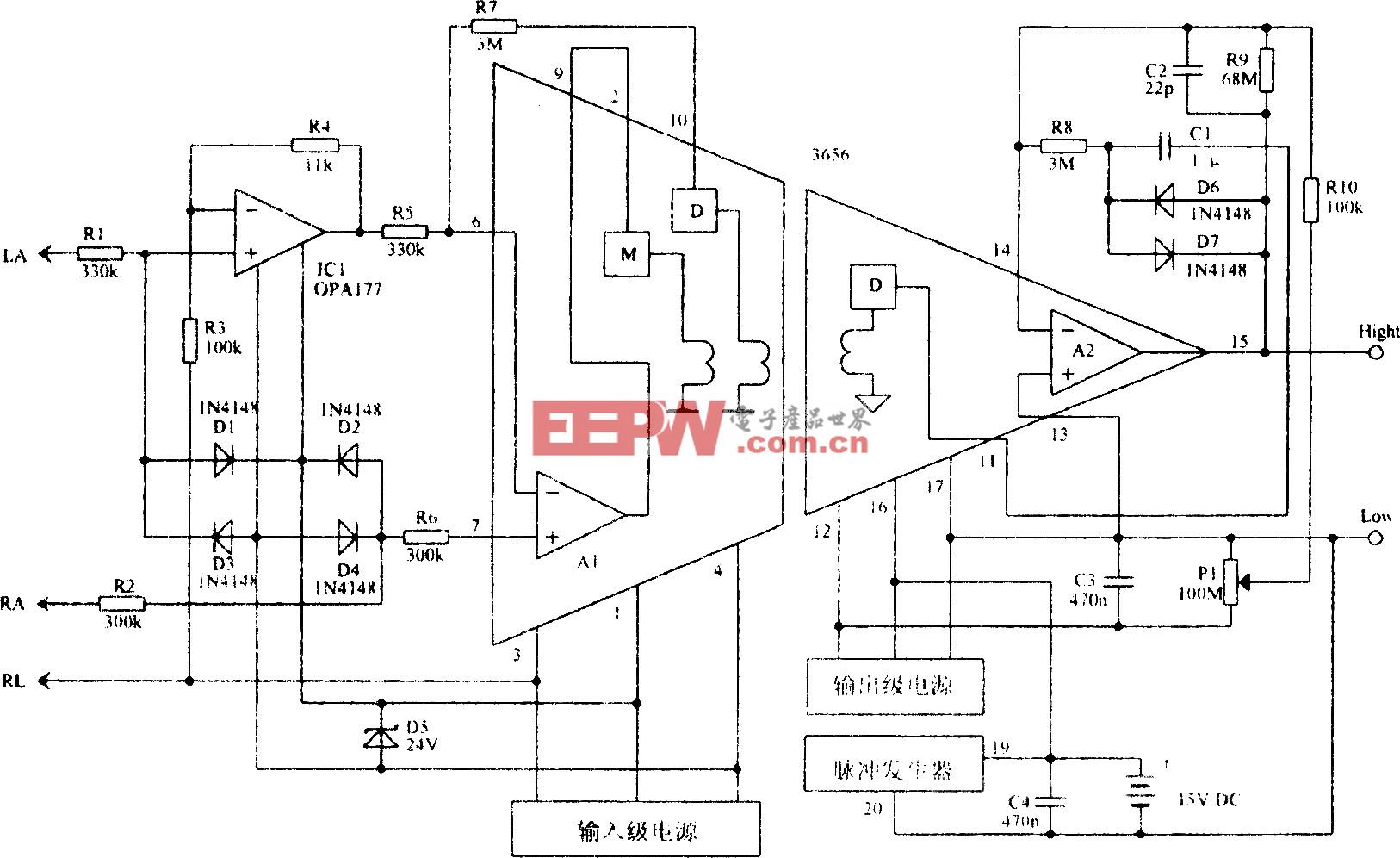

前端板电路图

图7。前端板电路图:ECG_I_II

图8。前端板电路图:ECG_LEAD_V1_V2_V3

图9。前端板电路图:CG_LEAD_V4_V5_V6

图10。前端板电路图:ECG_ADC

图11。前端板电路图:ECG_LEAD_OFF_DET

图12。前端板电路图:右腿驱动电路

图13。前端板电路图:PWR_CONN_INTRFCE

前端板材料清单(BOM):

图14。ECG 电缆详图

16.67/13.33/10/8.33-ns 指令周期,时钟速率60-,75-,100-,120-MHz,具有320KB 片内RAM。本文介绍了 TMS320C5515主要特性,方框图以及医疗开发套件(MDK)硬件方框图,ECG 前端方框图,前端板电路图详细电路图和所用材料清单(BOM)。

ECG Implementation on the TMS320C5515 DSP Medical Development Kit (Rev. B)

The TMS320C5515 Fixed-Point Digital Signal Processor is a member of TI’s TMS320C5000™ fixed-point Digital Signal Processor (DSP) product family and is designed for low-power applications.

The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32-bit data read bus and two 16-bit data read buses, two 16-bit data write buses, and additional buses dedicated to peripheral and DMA activity. These buses provide the ability to perform up to four 16-bit data reads and two 16-bit data writes in a single cycle. The device also includes four DMA controllers, each with 4 channels, providing data movements for 16-independent channel contexts without CPU intervention. Each DMA controller can perform one 32-bit data transfer per cycle, in parallel and independent of the CPU activity.

The C55x CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit x 17-bit multiplication and a 32-bit add in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the Address Unit (AU) and Data Unit (DU) of the C55x CPU.

The C55x CPU supports a variable byte width instruction set for improved code density. The Instruction Unit (IU) performs 32-bit program fetches from internal or external memory and queues instructions for the Program Unit (PU). The Program Unit decodes the instructions, directs tasks to the Address Unit (AU) and Data Unit (DU) resources, and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution of conditional instructions.

The general-purpose input and output functions along with the 10-bit SAR ADC provide sufficient pins for status, interrupts, and bit I/O for LCD displays, keyboards, and media interfaces. Serial media is supported through two MultiMedia Card/Secure Digital (MMC/SD) peripherals, four Inter-IC Sound (I2S Bus™) modules, one Serial-Port Interface (SPI) with up to 4 chip selects, one I2C multi-master and slave interface, and a Universal Asynchronous Receiver/Transmitter (UART) interface.

The device peripheral set includes an external memory interface (EMIF) that provides glueless access to asynchronous memories like EPROM, NOR, NAND, and SRAM, as well as to high-speed, high-density memories such as synchronous DRAM (SDRAM) and mobile SDRAM (mSDRAM). Additional peripherals include: a high-speed Universal Serial Bus (USB2.0) device mode only, and a real-time clock (RTC). This device also includes three general-purpose timers with one configurable as a watchdog timer, and an analog phase-locked loop (APLL) clock generator.

In addition, the device includes a tightly-coupled FFT Hardware Accelerator. The tightly-coupled FFT Hardware Accelerator supports 8 to 1024-point (in power of 2) real and complex-valued FFTs. Furthermore, the device includes three integrated LDOs (DSP_LDO, ANA_LDO, and USB_LDO) to power different sections of the device. The DSP_LDO can provide 1.3 V or 1.05 V to the DSP core (CVDD). To allow for lowest power operation, the programmer can shutdown the internal DSP_LDO cutting power to the DSP core (CVDD) while an external supply provides power to the RTC (CVDDRTC and DVDDRTC). The ANA_LDO is designed to provide 1.3 V to the DSP PLL (VDDA_PLL), SAR, and power management circuits (VDDA_ANA). The USB_LDO provides 1.3 V to USB core digital (USB_VDD1P3) and PHY circuits (USB_VDDA1P3). The RTC alarm interrupt or the WAKEUP pin can re-enable the internal DSP_LDO and re-apply power to the DSP core.

The device is supported by the industry’s award-winning eXpressDSP™, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, Texas Instruments’ algorithm standard, and the industry’s largest third-party network. Code Composer Studio IDE features code generation tools including a C Compiler and Linker, RTDX™, XDS100™, XDS510™, XDS560™ emulation device drivers, and evaluation modules. The device is also supported by the C55x DSP Library which features more than 50 foundational software kernels (FIR filters, IIR filters, FFTs, and various math functions) as well as chip support libraries.

TMS320C5515主要特性:

HIGHLIGHTS:

High-Perf/Low-Power, C55x™ Fixed-Point DSP

16.67/13.33/10/8.33-ns Instruction Cycle Time

60-, 75-, 100-, 120-MHz Clock Rate

320K Bytes On-Chip RAM

16-/8-Bit External Memory Interface (EMIF)

Two MultiMedia Card/Secure Digital I/Fs

Serial-Port I/F (SPI) With Four Chip-Selects

Four Inter-IC Sound (I2S Bus™)

USB 2.0 Full- and High-Speed Device

LCD Bridge With Asynchronous Interface

Tightly-Coupled FFT Hardware Accelerator

10-Bit 4-Input SAR ADC

Real-Time Clock (RTC) With Crystal Input

Four Core Isolated Power Supply Domains

Four I/O Isolated Power Supply Domains

Three integrated LDOs

Industrial Temperature Devices Available

1.05-V Core, 1.8/2.5/2.75/3.3-V I/Os

1.3-V Core, 1.8/2.5/2.75/3.3-V I/Os

图1。TMS320C5515方框图

医疗开发套件(MDK)

A number of emerging medical applications such as electrocardiography (ECG), digital stethoscope, and pulse oximeters require DSP processing performance at very low power. The TMS320C5515 digital signal processor (DSP) is ideally suited for such applications. The C5515 is a member of TI’s C5000™ fixed-point DSP platform. To enable the development of a broad range of medical applications on the C5515, Texas Instruments has developed an MDK based on the C5515 DSP. A typical medical application includes:

• An analog front end, including sensors to pick up signals of interest from the body

• Signal processing algorithms for signal conditioning, performing measurements and running analytics on measurements to determine the health condition

• User control and interaction, including graphical display of the signal processing results and connectivity to enable remote patient monitoring

The MDK is designed to support complete medical applications development. It includes the following elements:

• Analog front-end boards (FE boards) specific to the key target medical applications of the C5515 (ECG, digital stethoscope, pulse oximeter), highlighting the use of the TI analog components for medical applications

• C5515 DSP evaluation module (EVM) main board

• Medical applications software including example demonstrations

图2。医疗开发套件(MDK)硬件方框图

MDK Hardware Overview

An electrocardiogram (ECG/EKG) is the recording of the electrical activities of the heart and is used in the investigation of heart disease. The electrical waves can be measured by selectively placed electrodes (electrical contacts) on the skin.

医疗开发套件(MDK)ECG主要特性:

The key features of the MDK ECG system are:

• 12 lead ECG output using 10 electrode input

• Defibrillator protection circuitry

• Diagnostic quality ECG with bandwidth of 0.05 Hz to 150 Hz

• Heartbeat rate display

• Leads off detection

• Real-time 12 lead ECG waveform display on EVM LCD screen, one lead selectable at a time

• Zoom option for the Y-axis (amplitude) on EVM LCD screen

• Real-time 12 lead ECG waveform display on PC, three leads at a time

• Zoom function on X-axis (time) and Y-axis (amplitude) on PC application

• Freeze screen option on PC Application

• Recording of ECG data and offline view option of recorded ECG data on PC application Several elements of the MDK ECG system are:

• C5515 EVM

• ECG front-end board

• ECG cable

1)C5515 EVM

The EVM comes with a full compliment of on-board devices that suit a wide variety of application environments.

For further details on the C5515 EVM, see the Medical Devlopment Kit provided with your EVM.

Key components and interfaces of the C5515 EVM used in the MDK ECG system include:

• Texas Instrument’s TMS320C5515 operating at 100 MHz

• User universal serial bus (USB) port via the C5515

• Inter-integrated circuit (I2C) /serial peripheral interface (SPI) electrically erasable programmable read-only memory (EEPROM)

• External memory interface (EMIF), I2C, universal asynchronous receiver/transmitter (UART), SPI interfaces

• SAR

• External IEEE Standard 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture (JTAG) emulation interface

• Embedded JTAG controller

• Color LCD display

• Keys (user switches)

The EVM operates from a + 5 V external power supply or battery and is designed to work with TI’s Code Composer Studio™ integrated development environment (IDE). Code Composer Studio communicates with the EVM board through the external emulator, or on-board emulator.

2)ECG Front-End Board

Figure 3 shows the ECG front-end board. The potentials captured by the electrodes are passed through

the defibrillator protection (DP) circuit in the ECG front-end board. Then, the front end board derives 8 out

of 12 ECG leads and provides the digital input to the DSP subsystem. The front-end board can be

interfaced with the EVM board through a universal front-end connector. The front-end board is interfaced

with and powered by the C5515 EVM board through the universal front-end connector by using I2C and

I2S interfaces.

The 16 channel analog-to-digital converter (ADC) (ADS1258) on the front-end board is configured for 500

Hz sampling with 24-bit data resolution. ADC is interfaced with the C5515 using the SPI bus.

图3。ECG板外形图

3)ECG Cable

The ECG cable consists of four limb and six chest electrodes. This cable is connected to the front-end board through the DB15 connector. The ECG electrodes pick up ECG signals from the ECG simulator/patient and send them to the ECG front-end board; an off-the-shelf ECG cable is used. For more details regarding ECG cable

图4。安装在C5515 EVM的ECG前端外形图

图5。ECG 前端方框图

图6。DSP软件架构图

前端板电路图

图7。前端板电路图:ECG_I_II

图8。前端板电路图:ECG_LEAD_V1_V2_V3

图9。前端板电路图:CG_LEAD_V4_V5_V6

图10。前端板电路图:ECG_ADC

图11。前端板电路图:ECG_LEAD_OFF_DET

图12。前端板电路图:右腿驱动电路

图13。前端板电路图:PWR_CONN_INTRFCE

前端板材料清单(BOM):

图14。ECG 电缆详图

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码