基于DSP的USB接口设计与实现

摘要:介绍了一种基于DSP的USB 接口设计方案,分别从接口的硬件设计、接口操作原理、软件设计流程以及中断服务程序设计要点等方面进行阐述,并利用Cypress 公司提供的USB2.0 接口芯片CY7C68001 实现了USB2.0 从机接口设计,通过硬件平台的搭建和软件程序设计,实现了PC 机与DSP 之间高速双向地传输数据。

1 引言

近年来,随着数字信号技术的发展,需要处理的数据量越来越大,处理的速度也越来越快,因此具有高速性能DSP 芯片的应用得到了广泛重视。而通过DSP 处理的数据往往要传输给PC 机进行存储和再处理,那么就必须解决DSP 与 PC 机之间的高速通信问题。本设计方案以德州仪器(TI)的C5000 系列DSP 芯片TMS320VC5416为微处理器,利用Cypress公司提供的USB2.0接口芯片CY7C68001 实现了USB2.0 从机接口设计,从而使PC机与DSP 通过USB2.0 接口实现高速双向地传输数据。

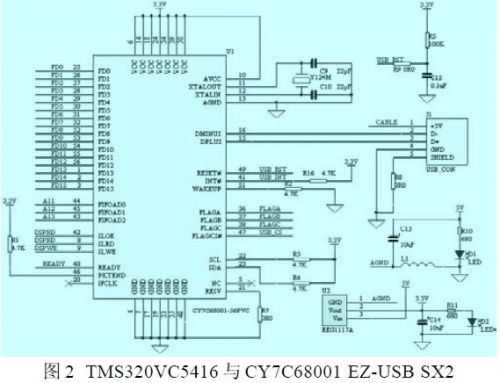

2 TMS320VC5416 与CY7C68001 EZUSBSX2硬件接口设计

系统方案采用PC机作为上位机,负责USB总线上检测到设备接入并进行枚举、识别的过程,并且可以通过在PC机上运行应用程序来控制数据的传输。USB芯片作为USB设备端,连接DSP与上位机的数据交换。DSP用于实现USB协议,通过DSP编程实现DSP数据通过USB接口与PC机通信,且USB芯片的描述符写入及各种命令状态的处理均通过DSP编程实现。

TMS320VC5416 是TI 的一款16bit 定点高性能DSP,由于VC5416的功耗低、性能高,其分开的指令和数据空间使该芯片具有高度的并行操作能力,在单周期内允许指令和数据同时存取,再加上高度优化的指令集,使得该芯片具有很高的运算速度,同时该芯片本身具有丰富的片内存储器资源以及多种片上外设,因此在工程界得到了广泛的应用。

Cypress 公司的CY7C68001 EZ-USB SX2 是一款高性能、使用方便的USB2.0 接口芯片,满足USB2.0 协议,可工作在高速(480Mbps)或全速(12Mbps)模式下,提供一个控制端点用于处理USB设备的请求以及四个可配置端点用于传输控制和数据信号,这四个端点共享一个4KB的FIFO空间,具备标准的8位或16位外部主机接口,可无缝连接多种标准微处理器,比方说DSP、ASIC和FPGA等,并可根据需求设置为同步或异步接口,片内集成锁相环(PLL),该芯片广泛应用于DSL调制解调器、MP3、读卡器、数码照机、扫描仪、打印机等设备。

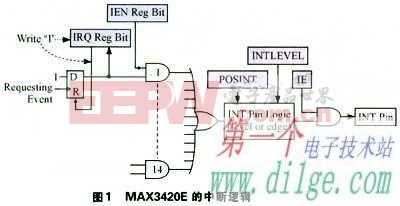

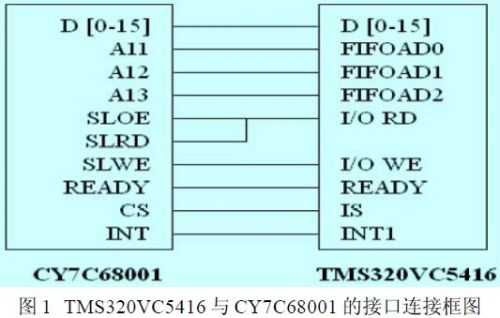

系统的硬件接口设计如图1、图2所示,两者通过数据、地址总线以及读、写信号线等进行通信,CY7C68001的片选信号连接至TMS320VC5416 的I/O空间片选信号上,CY7C68001 的FIFO扩展在VC5416 的I/O 空间上。

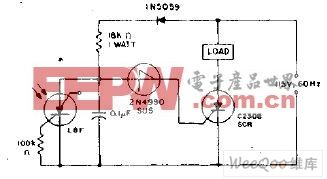

电源部分采用一片1117 将5V 转为3.3V供给CY7C68001EZ-USB SX2,模拟地与数字地之间采用磁珠连接,复位部分采用RC电路设计,且芯片资料上介绍有典型值100KΩ和0.1μF。

3 接口操作原理

CY7C68001 有两个外部接口:

(1) 命令接口:用来访问CY7C68001 寄存器、Endpoint 0缓冲器,以及描述表。

(2) FIFO数据接口:用来访问4个1K字节的FIFO中的数据。

这两个外部接口均可以通过同步或异步的方式进行访问。

本设计采用异步的方式进行访问。根据图3 的地址分配,利用TMS320VC5416 的三根高位地址线(A11、A12、A13)连接CY7C68001 的FIFOAD0/1/2,用以选择FIFO2、FIFO4、FIFO6、FIFO8以及命令接口,其地址表如图3所示。CY7C68001的地址线FIFOADR[2:0]为100B 时,选中CY7C68001 的命令口(Command)。通过CY7C68001的命令口,可以访问37个寄存器、Endpoint 0缓冲器(64个字节FIFO)和描述表(500个字节FIFO)等,对这些寄存器进行读写方式采用二次寻址方式,即首先通过命令口将要寻址的寄存器的子地址和操作类型(读或写)写入,然后再通过命令口将数据读出或写入相应的寄存器。

写入命令口的内容称为命令字,命令字包含要寻址的寄存器的子地址,或要写入寄存器的数据的高4位或低4位。读命令口必须要跟在给命令口写读命令字之后,读出的为相应寄存器的8位数据。所以,寄存器的写操作由3 个步骤组成:

4 USB 接口的软件设计

USB接口的软件设计由两部分组成:一是在PC机Windows中运行USB 2.0 Utility 工具,是一个Windows 图形用户界面软件,提供CY7C68001 与Windows 操作系统的接口程序,使得CY7C68001的开发变得简单。二是在在DSP中运行嵌入式应用程序代码,提供硬件的驱动,用来管理CY7C68001进行不同方式的数据处理,从而实现USB2.0 传输协议。

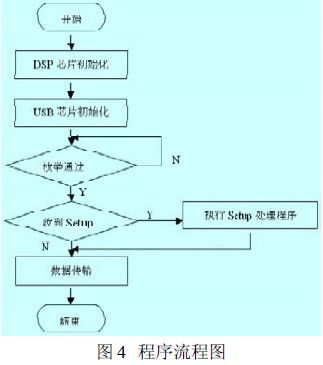

4.1 USB 接口的软件设计流程

USB接口的软件设计,DSP端代码大致包括DSP芯片初始化(vc5416_init 函数)、USB芯片初始化(sx2_init 函数)、USB芯片配置程序( s x 2 _ s e t u p 函数) 以及USB 芯片数据读写程序(sx2_processdata 函数),程序流程如图4 所示。

DSP芯片初始化(vc5416_init函数)主要负责设置VC5416的工作频率,配置SWCR以及SWWSR寄存器,另外本应用系统采用一个GPIO引脚作为68001的复位信号,所以还需要对其进行相关设置。

USB芯片初始化(sx2_init函数)主要负责清除Buffer缓冲区以及使能VC5416 的外部中断INT1,待初始化结束后发出READY中断,此时DSP将描述符写入68001,进行枚举过程,待枚举通过后发出ENUMOK中断,枚举方式可以采用外部EEPROM通过I2C总线上电后从外部导入描述符,也可采用通过运行DSP程序从DSP导入到68001,本应用系统采用第二种枚举方式。

USB芯片配置程序(sx2_setup函数)是在命令通道(0节点)收到无法自动处理的上位机请求,68001向VC5416发出SETUP中断后执行的程序,此时VC5416 通过对SETUP寄存器连续执行八次读操作流程即可得到8字节请求,系统可以响应该请求或STALL该请求。

USB 芯片数据读写程序(sx2_processdata 函数)即PC 机与USB从设备端遵照USB传输协议进行数据通信。

CY7C68001的地址FIFOAD[2:0]为100时,选中CY7C68001的命令接口。对于命令接口的读写要分两步进行,即在READY有效时,先通过命令接口写入要寻址寄存器的子地址和操作类型(读或写),之后,在READY再次有效时分两次读写命令接口,即可读写一个字节的数据。

4.2 中断服务程序设计要点

DSP使用一个外部中断引脚(INT1)与CY7C68001的INT脚相连,USB总线上产生一系列的活动,均会触发相应的中断,一旦中断产生,DSP 会从CY7C68001 的Command 口中读取相应的值,来判断产生的是何种中断。

CY7C68001 EZ-USB SX2 包括六个中断源:SETUP(收到来自于USB 上位机(PC)发送过来的Set-up 包时产生的中断)、EP0BUF(端点0 缓存可用时产生的中断)、FLAGS(OUT 端点FIFO的状态从空变为非空时产生的中断)、ENUMOK(SX2枚举完成后产生的中断)、BUSACTIVITY(SX2检测到总线活动时产生的中断)以及READY(SX2上电并且复位完毕后产生的中断),每一个中断源都可以通过置位或清除INTENABLE寄存器中相应位来使能或禁止。

CY7C68001芯片采用中断缓冲机制,每次只会有一个中断源,其他中断源只有在上一个中断被读走后才会发出新的中断请求。

因此,当一个中断产生时,INT引脚为低电平状态,同时中断状态位会置入命令接口,在进入中断程序后应先对中断源进行判断,首先判断是否是读寄存器所产生的中断,如果是则将数据准备好标志位置1然后返回,否则外部PC通过选通SLRD/SLOE信号从命令接口中读取中断状态位来判断产生的是何种中断,然后根据中断源进行相应操作,DSP读取中断状态位后自动清除中断标志位。

5 结束语

基于上述方法实现的USB接口电路,为DSP构筑与PC机之间的高速双向传输通路。通过硬件平台的搭建和软件程序的实现,验证了该接口电路可以满足高速信号处理的数据传输要求,并具有速度快和可靠性高等优点,相信随着嵌入式技术的发展以及基于USB2.0 协议的芯片的普遍应用,基于USB的接口技术将得到更加广泛的应用。

关键词: 接口设计 中断 CY7C680011 嵌入

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码