新思科技携手台积公司简化多裸晶系统复杂性,推出面向台积公司N3E工艺的“从架构探索到签核” 统一设计平台和经验证的UCIe IP

摘要:

● 新思科技3DIC Compiler集成了3Dblox 2.0标准,可用于异构集成和完整的“从架构探索到签核”完整解决方案。

● 新思科技 UCIe PHY IP在台积公司N3E工艺上实现了首次通过硅片的成功(first-pass silicon success),可提供低延迟、低功耗和高带宽的芯片间连接。

● UCIe PHY IP与3DIC Compiler的结合将有效优化多裸晶系统设计,能够以更低的集成风险实现更高的结果质量。

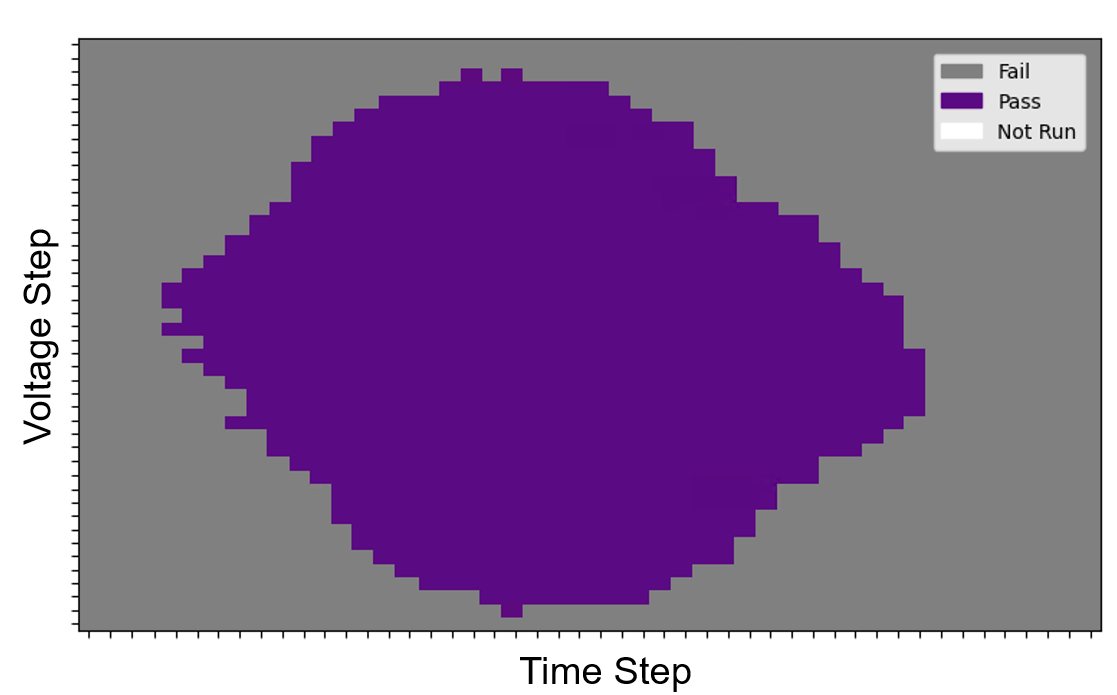

图 新思科技UCIe PHY IP在台积公司N3E工艺上首次通过硅片的成功,展示了出充足的链路裕量

新思科技(Synopsys, Inc.)近日宣布进一步扩大与台积公司的合作,双方携手通过可支持最新3Dblox 2.0标准和台积公司3DFabric™技术的全面解决方案不断优化多裸晶系统(Multi-Die)设计。新思科技多裸晶系统解决方案包括 “从架构探索到签核”统一设计平台3DIC Compiler,可提供行业领先的设计效率,来实现芯片的容量和性能要求。此外,新思科技 UCIe IP也已在台积公司领先的N3E先进工艺上取得了首次通过硅片的成功,实现die-to-die高速无缝互连。

台积公司设计基础设施管理部负责人Dan Kochpatcharin表示:“台积公司长期与新思科紧密合作,为芯片开发者提供差异化的解决方案,帮助他们解决从早期架构到制造过程中面临的高度复杂挑战。我们与新思科技的长期合作,让我们的共同客户能够采针对性能和功耗效率优化的解决方案,以应对高性能计算、数据中心和汽车应用领域的多裸晶系统设计要求。”

新思科技EDA事业部战略与产品管理副总裁Sanjay Bali表示:“我们与台积公司强强联合,为多裸晶系统提供了全面、可扩展的解决方案,实现了前所未有的芯片性能和设计效率。采用3Dblox 2.0等通用标准在统一设计平台上进行多裸晶系统设计的架构探索、分析和签核,并结合在台积公司N3E工艺上已实现首次通过硅片成功的新思科技 UCIe PHY IP,客户能够进一步加速从早期架构探索到制造的系统设计全流程。”

新思科技3DIC Compiler设计平台已通过台积公司认证,可在统一的裸片/封装探索、协同设计和分析平台上使用3Dblox 2.0标准和3DFabric技术进行全栈设计。新思科技集成系统分析功能可与3Dblox 2.0系统原型设计相结合,协同优化热和电源完整性,有助于确保设计可行性。新思科技和Ansys持续合作,将新思科技 3DIC Compiler和Ansys多物理分析技术相集成,提供系统级效果的签核准确性。新思科技3DIC Compiler还可与新思科技测试产品互操作,以确保批量测试和质量。

新思科技UCIe PHY IP已在台积公司 N3E工艺上实现首次通过硅片的成功,并获多家全球领先企业采用,能够帮助开发者高效地将die-to-die互联的业界标准集成到他们的多裸晶系统中。结果显示,该IP在16Gbps时可实现行业领先的功耗效率和性能,并可扩展至24Gbps,同时具有强大的链路裕量。新思科技的完整UCIe Compiler、PHY和验证IP解决方案目前已支持标准和先进封装,提供了测试、修复和监测功能,即使在以确保多裸晶系统在现场操作中的可靠性。此外,新思科技还提供了面向HBM3技术的完整IP解决方案,以满足Multi-Die系统的高内存带宽需求。新思科技IP产品与新思科技3DIC Compiler的组合通过自动化布局布线、中介层研究和信号完整性分析,支持3Dblox 2.0 die-to-die可行性研究,从而提高生产力并降低IP集成风险。

上市情况

● 新思科技面向台积公司N3E工艺的UCIe PHY IP和3DIC Compiler现已上市。

● 新思科技面向台积公司先进工艺的 HBM3 IP现已上市。

关键词: 新思科技 台积 多裸晶系统 N3E工艺 签核 UCIe IP

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码

相关文章

-

-

2024-07-11

-

-

-

-

-

-