基于线性提升和高速低噪声比较器技术的10 bit 160 MSPS SAR ADC设计

编者按:基于采样管p阱浮空技术用于寄生电容电荷补偿,实现采样开关高线性度。使串联的两个寄生电容的容值变化方向相反,从而实现了容值的相互补偿,使输入管的寄生电容容值不随输入信号幅度变化,相较传统技术,采样开关的线性度得到进一步提高。另一方面,提出了一种高速低噪声动态比较器技术,减小了MOS管的导通电阻,增加了比较器速度,通过衬底自举技术,使比较器输入管的阈值电压明显降低,跨导增加,从而降低了比较器的等效输入噪声,解决了动态比较器速度和噪声之间必须进行折中的技术难点。

中图分类号:TN432文献标识码:A

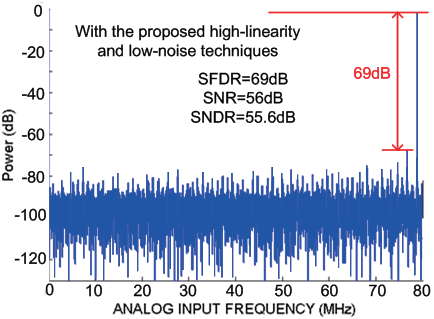

摘要:为了验证上述技术,基于标准65 nm CMOS工艺,设计了一款10 bit 160 MSPS SAR ADC。1 V工作电压下,芯片实测功耗为2 mW,无杂散动态范围(SFDR)>69 dB,信号噪声失真比(SNDR)>55.6 dB,ADC核的芯片面积仅为0.023 mm2,在莱奎斯特采样情况下,优值(FoM)为25.4 fJ/步。

0 引言

近年来,随着CMOS 工艺尺寸越来越小,(8~12)bit 逐次逼近型模数转换器(SAR ADC)在消耗较小面积的情况下,采样速度可以达到几十甚至上百MHz[1-8],时间交织结构[9-10] 和多位每周期的ADC[11] 可以提高ADC 的速度,但该结构带来的通道失配和比较器失调问题会影响ADC 线性度。共模电压变化技术[12] 可以降低SAR ADC 的功耗,但会引起比较器失调的变化。流水线型SAR ADC 中,校正过程会非常复杂。SAR ADC设计中,采样开关是影响整个SAR ADC 线性度的最重要因素之一。随着采样速度提升,需要增加采样开关的面积来减小采样开关的导通电阻。但采样开关面积增加,采样开关源/ 漏极和衬底之间寄生电容也随之增加。另一方面,对于SAR ADC 而言,为了实现较高信噪比,输入信号通常为轨对轨信号,采样开关的寄生电容值会随着输入信号变化,使采样开关的线性度进一步恶化。在文献[16] 中,输入信号和采样开关衬底直接相连,可以消除采样开关源/ 漏和衬底的寄生电容及体效应。但是,在深N 阱管中,NMOS 衬底和N 阱之间的寄生电容仍然会限制整个ADC 的线性度。文献[21] 中提出了一种采样开关线性化技术,通过采样开关寄生电容补偿技术提高了采样开关的线性度。但是,这种技术会使采样开关寄生电容的绝对值增加,使采样开关线性度的提升不明显。另一方面,文献[17-21] 提出的高速低功耗比较器技术,随着比较器速度提升,比较器输入对管工作饱和区的时间变短,造成比较器噪声性能下降。因此,比较器的噪声性能和工作速度之间的折中关系也是SARADC 中高性能比较器设计的难点。

基于上述SAR ADC 中的技术难点,本文针对采样开关提出了一种p 阱悬浮技术,该技术能够降低采样开关的非理想寄生电容,可以明显抑制采样开关的寄生电容值随输入信号变化的效应。同时,提出了一种动态比较器衬底电压自举技术,可以降低MOS 管的导通电阻和阈值电压。MOS 管导通电阻的降低可以降低比较器的延迟时间,MOS 管阈值电压的降低,可以增加比较器输入MOS 管的跨导,降低比较器的等效输入噪声。在160 MSPS 采样率下,SAR ADC 的SFDR>69 dB,SNDR>55.6 dB,在莱奎斯特采样情况下,优值(FoM)为25.4 fJ/ 步。

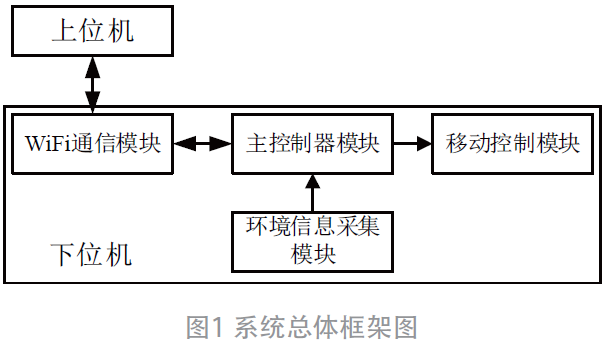

1 SAR ADC总体架构

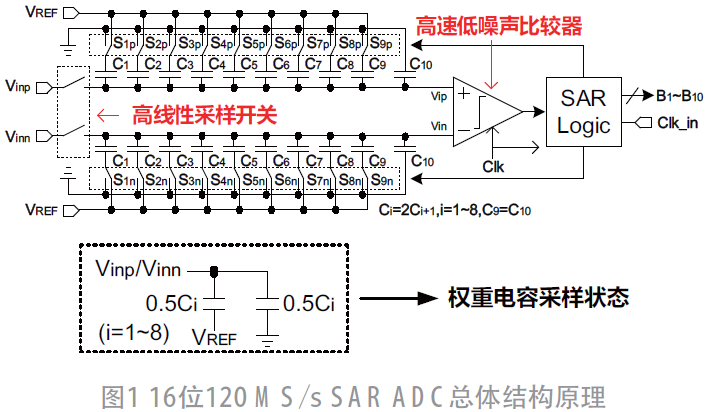

本设计所提出的SAR ADC 总体结构如图1 所示。当ADC 处于采样相时,高线性度的采样开关导通,电容阵列对输入信号Vinp/Vinn 进行采样。当ADC 处于逐次逼近相时,时钟信号Clk 触发比较器和SAR logic,产生10 bit 输出码。如图1 所示,权重电容C1~C8 分裂为两个相等的子电容,在采样过程中,这两个子电容的一端接输入信号,另一端分别接负基准地和正基准VREF[21]。

本文采用共模电压恒定的开关切换方式来提高比较器的共模抑制比。单位电容的容值为1 fF,单端的电容容值为512 fF。通过1 000 次蒙特卡洛仿真后,单位电容失配不超过0.2%,表明上述电容设计值满足10 bit ADC 的精度要求。为了减小采样极板和地之间的寄生电容,电容阵列中的电容采样高层金属M7 进行设计,使比较器输入端的寄生电容约为9 fF。因此,采样极板主要的寄生电容为采样开关的寄生电容。通过本文所提出的采样开关p 阱浮空技术,采样开关源/ 漏和衬底之间的寄生电容约为35 fF。因此,总的采样电容约为556 fF。本设计中,1 LSB 约为1.4 mV,kT/C 约为0.1 mV rms。

2 高速高线性采样开关技术

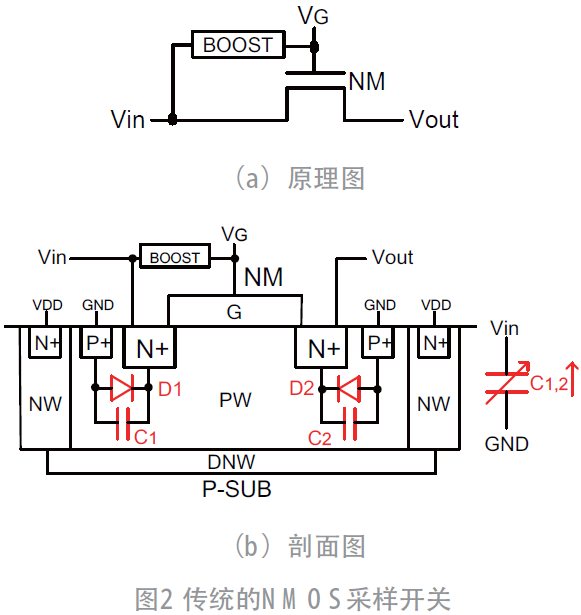

SAR ADC 的线性度主要取决于采样开关源/ 漏和衬底之间的寄生二极管所产生的寄生电容,该寄生电容值会随输入信号幅度改变而变化。在高速采样情况下,为了减小导通电阻,采样开关的面积会比较大,采样开关的寄生电容对线性度的影响会随之增大。图2 为采用栅压自举技术的传统NMOS 采样开关的原理图和剖面图,由图2(b)可知,在采样状态下,寄生二极管D1和D2 均处于反偏状态,其寄生电容为势垒电容C1 和C2。由文献[21] 可知,C1 和C2 会随着输入信号Vin 的变化而变化。在文献[16] 中,采用输入信号和衬底短接的方式消除了源/ 漏和衬底之间的寄生电容。但是,p阱PW 和n 阱NW 之间的寄生电容仍在存在,使采样开关的总寄生电容并没有减小,这会明显影响整个ADC的采样速度。

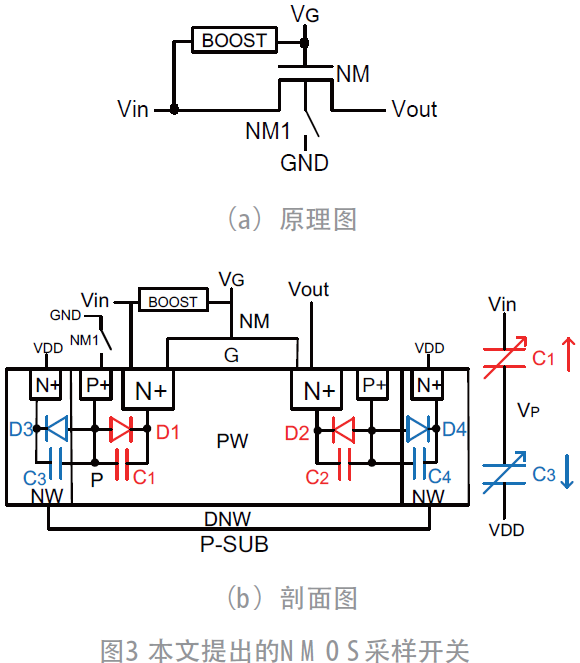

本文提出了一种基于p 阱浮空结构的采样开关线性度提升技术,如图3 所示。下拉开关NM1 连接采样开关NM 的衬底和地,由于NM1 的尺寸很小,因此,引入NM1 所产生的寄生电容远小于采样开关NM 本身的寄生电容。当采样开关NM 断开时,NM1 导通,NM的衬底电位被下拉到地。当采样开关NM 导通时,NM1断开,采样开关NM 的衬底处于浮空状态。图3(b)给出了该结构的剖面图,下面以电容C1 和C3 的变化情况为例进行说明。

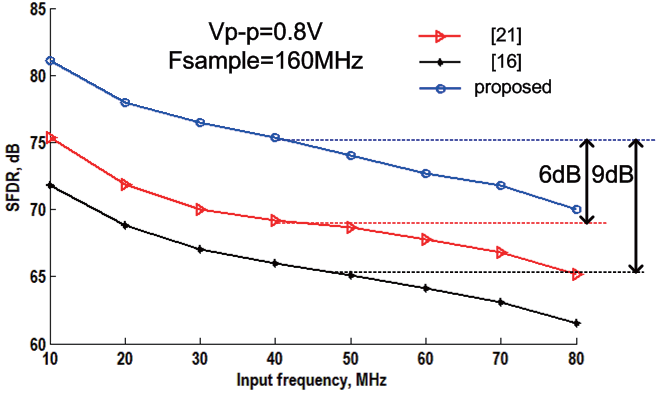

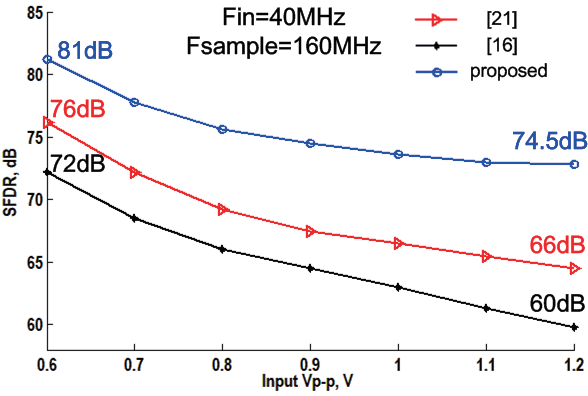

图4 采样开关寄生电容和输入信号幅度的关系

(a)频率

(b)幅度的变化情况

图5 SFDR 随输入信号(a)频率(b)幅度的变化情况

当ADC 处于逐次逼近相时,采样开关NM 的衬底通过NM1 和地相连,二极管D1、D3 都处于反偏状态。当ADC 处于采样相时,采样开关NM 的衬底浮空,则寄生电容C1 和C3 为串联关系,因此,此时采样开关的总寄生电容小于C1 和C3。同时,采样开关NM 的衬底电压为输入信号Vin,由于C1、C3 会带来分压,VP的变化取决于输入信号Vin、C1 和C3 的值。通过小信号等效,由基尔霍夫电流定律可知,如果C1 = C3,VP电压的变化为输入信号Vin 变化的0.5 倍,这表示C1 和C3 两端的电压变化相同。通过势垒电容的计算公式可知,Vin 在(0.2~1)V 变化范围内的情况下,寄生电容C1、C3 的容值最大变化量分别为-10% 与12%,因此,C1 和C3 容值的变化几乎相同,而变化方向相反。由于C1 和C3 的串联关系,和文献[16] 相比,C1 的变化所造成的总寄生电容变化被减小了1/2。

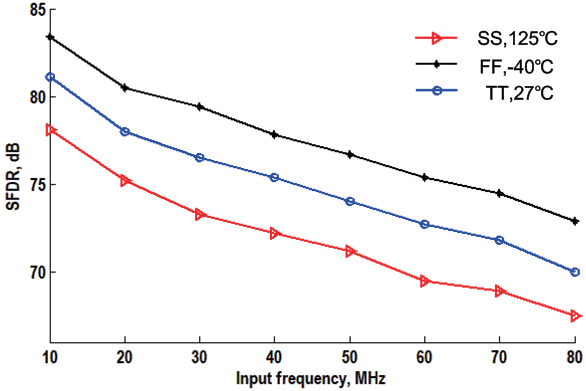

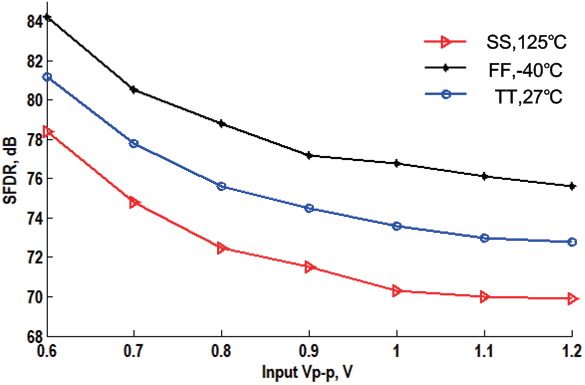

(a)随输入差分信号频率的变化

(b)随输入差分信号幅度的变化

图6 工艺角和温度变化情况下,SFDR随输入差分信号的频率、幅度的变化情况

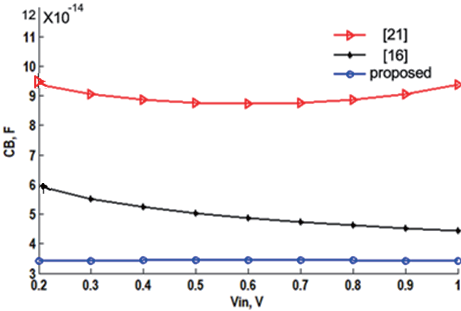

为了证明该技术和文献[16] 和[21] 相比的优势,基于标准65 nm CMOS 工艺,设计了上述采样开关,将寄生参数导入MATLAB 中进行仿真。采样开关的寄生电容和输入信号幅度之间的关系如图4 所示,当输入信号Vin 在(0.2~1)V 时间变化时,文献[16] 和[21] 中采样开关的寄生电容值变化分别约为31.3% 和9%。本结构中采用了p 阱浮空技术,这样采样开关的寄生电容值变化为1.4%。即使考虑到NM1 的寄生电容,本结构采样开关的总寄生电容也小于35 fF,该寄生电容是文献[16]和[21] 寄生电容的70% 和39%。因此,本文提出的采样开关和传统结构相比能提线性度。SFDR 随输入信号频率和幅度的变化情况分别如图5(a)和图5(b)所示。在图5(a)中,本结构的SFDR 与文献[16] 和[21] 相比,分别提升了9 dB 和6 dB。在图5(b)中,输入差分信号峰- 峰值(Vp-p)在(0.6~1.2)V 范围内变化时,文献[16] 和[21] 的SFDR 下降分别为10 dB 和12 dB,本结构的SFDR 下降仅为6.5 dB。在工艺角和温度变化情况下,SFDR 随输入差分信号频率和幅度变化分别如图6(a)和图6(b)所示。可以看出,在PVT 变化的情况下,输入信号的频率在(10~80)MHz 之间变化时,和文献[16] 和[21] 相比,本文比较器的SFDR 分别提升10 dB 与6 dB。当输入差分信号幅度在(0.6~1.2)V 范围变化时,和文献[16] 和[21] 相比,本比较器的SFDR分别提升14 dB 与8.8 dB。

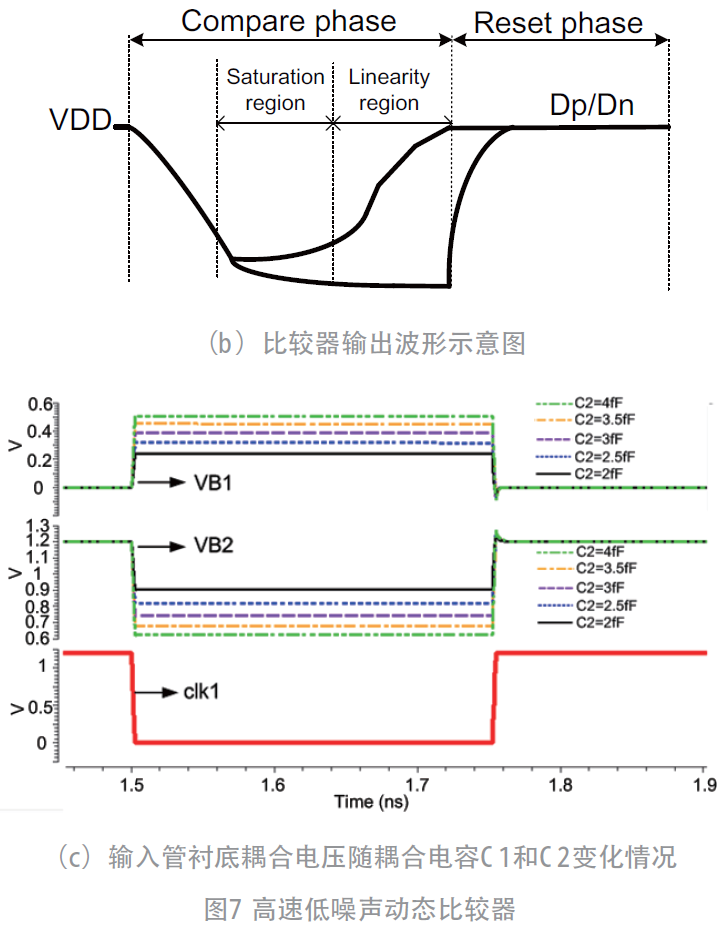

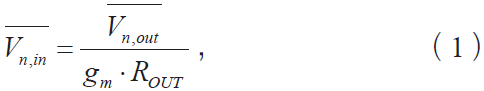

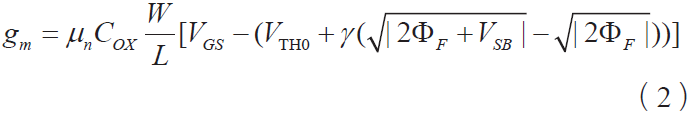

动态比较器是SAR ADC 设计中的一个关键单元,随着CMOS 工艺尺寸不断缩小,动态比较器的速度不断提升,文献[17-19] 给出了几种高速动态比较器的结构,但是,比较器的等效输入噪声随着比较器的速度增加而增加。为了实现高速低噪声比较器,本文提出了一种比较器结构,如图7(a)所示,使用了互补型输入结构,针对输入管M1、M2、M3 和M4 采用了衬底电压自举技术。比较器的输出波形示意图如图7(b)所示,当输出信号Dp 和Dn 的值很接近时,比较器对噪声很敏感,此时,比较器输入级的MOS 工作在饱和区,此时,比较器可以看作1 个放大器,等效输入噪声可近似表示为:

图8 跨导与漏电流随耦合电容变化情况

这里的 和

和 分别表示比较器的等效输入和输出噪声,ROUT 表示比较器第1 级的输出阻抗,gm 表示第1 级输入级的跨导,为了实现低噪声要求,需要更大的输入级跨导或者更高的增益,通过增加输出阻抗来提高增益使带宽降低,从而影响速度。因此,可通过提高比较器第1 级跨导的方式来抑制噪声。NMOS 管的跨导表达式可表示为:

分别表示比较器的等效输入和输出噪声,ROUT 表示比较器第1 级的输出阻抗,gm 表示第1 级输入级的跨导,为了实现低噪声要求,需要更大的输入级跨导或者更高的增益,通过增加输出阻抗来提高增益使带宽降低,从而影响速度。因此,可通过提高比较器第1 级跨导的方式来抑制噪声。NMOS 管的跨导表达式可表示为:

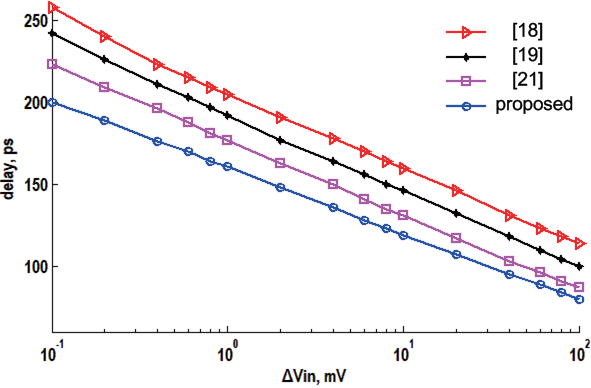

图9 比较器延迟对比情况

n 和COX 分别为电子迁移率和MOS 管氧化层电容,W/L 为MOS 管的宽长比,VGS,VSB 和VTH 分别为MOS管的栅- 源电压,源- 衬底电压和阈值电压,其余值为常数。当比较器工作在复位状态时,clk1 和clk1n 分别为0 和1,M8 和M9 导通,M1 和M2 的衬底电压(VB1)为0,M4 和M5 的衬底电压(VB2)为1。当比较器进入比较状态后,clk1 从0 变为1,M8 和M9 被clk1 和clk1n 关断。因此,VB1 和VB2 的电压分别被C1 和C2 耦合。这表明M1 和M2 的衬底电压会增加,M4 和M5 的衬底电压会降低。使M1、M2、M4 和M5 的阈值电压降低,增加输入管的跨导gm,从而达到降低比较器等效输入噪声的目的。因此,比较器速度和噪声之间的矛盾被缓解了,衬底耦合电压VB1、VB2 和C1、C2 之间的对应关系如图7(c)所示。跨导与漏电流随耦合电容变化情况如图8 所示,随着C1 和C2 从0 变化到4 fF,跨导增加了51%,此时的漏电流小于1.5 nA。为了对文献[18-20] 中比较器和该论文提供的比较器的性能进行对比,在65 nm CMOS 工艺下,对上述4 种结构的比较器进行了设计,该论文结构中的C1 和C2 取值为4 fF。4 种比较器的后仿真延迟对比如图9 所示,由图9 可知,本论文提出的比较器的速度最快,其速度分别为文献[18] 和[19] 的1.3 倍和1.2 倍,和文献[21] 相比,平均延时被压缩了17%。本论文提出的比较器结构与文献[19] 和[20]中比较器结构的噪声仿真对比如图10 所示,本论文所提出的比较器结构和文献[19] 和[20] 相比,等效输入噪声分别减小了25% 和40%。

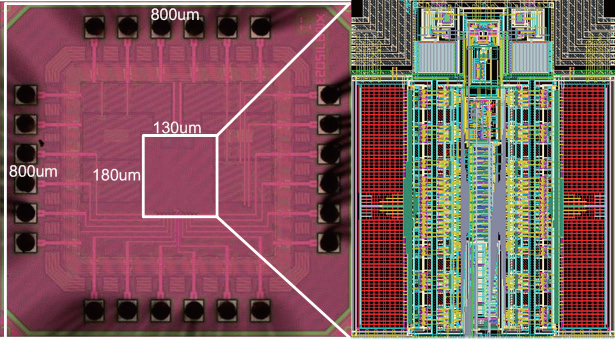

图11 ADC芯片照片

4 电路测试结果

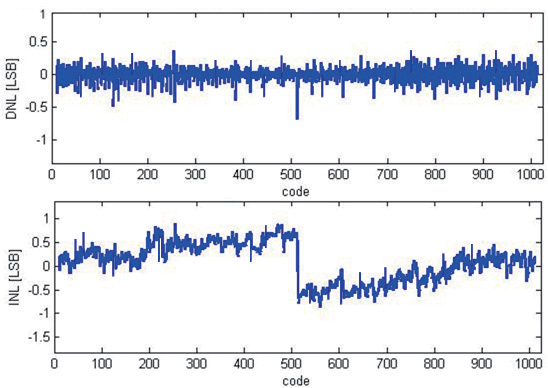

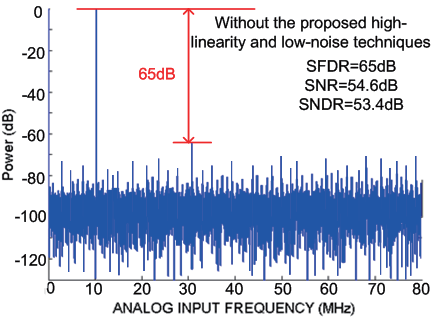

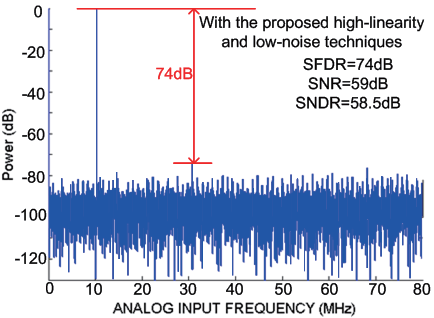

本文提出的SAR ADC 基于标准65 nm CMOS 工艺设计,图11 为芯片照片,核心面积为0.13 mm×0.18 mm,静态误差如图12 所示,DNL 为-0.75/+0.47 LSB,INL为-0.97/+0.93 LSB。输入信号频率为10 MHz 时,如图13 所示,由于受到采样开关寄生电容影响,未采用本文技术的SFDR 仅为65 dB,同时受到比较器噪声影响,SNDR 仅为54.6 dB。如图14 所示,采用本文技术不仅提高了采样开关线性度,同时减小了比较器噪声,SFDR 与SNDR 分别提升了9 dB 和4.3 dB。

图12 DNL和INL测试结果

图13 没有采用本技术动态性能低频测试结果

图14 采用本技术动态性能低频测试结果

图15 采用本技术动态性能高频测试结果

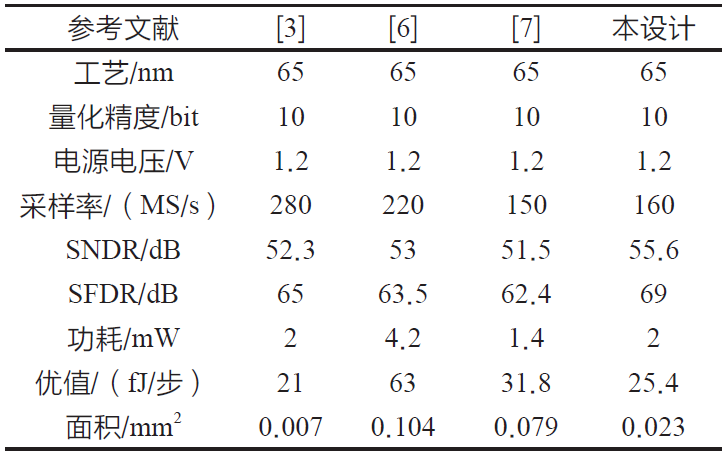

采用本技术动态性能高频测试结果如图15 所示,在莱奎斯特输入频率下,SFDR 为69 dB、SNDR 为56 dB。表1 为本设计SAR ADC 与其他研究进行对比的结果,通过对比可知:本设计在较高的采样速度下,有更好的线性度,更低的功耗和更低的优值(FoM)。

表1 SAR ADC主要性能参数对比

5 结束语

本设计通过采用采样管p 阱浮空技术,大大提升了采样开关线性度,通过比较器输入管的衬底电压耦合技术,比较器不仅实现高速工作,同时实现低噪声性能。通过上述技术,设计了一个10 位160 MSPS 采样率的SAR ADC,在莱奎斯特采样率下,SFDR 为69 dB,SNDR 为55.6 dB,功耗仅为2 mW,优值为25.4 J/ 步。测试结果表明,上述技术提升了高速SAR ADC 的性能。

参考文献:

[1] LIU C,CHANG S,HUANG G,et al.A 10b 100MS/s1.13mW SAR ADC w i t h b i n a r y - s c a l e d e r r o r c o m p e n s a t i o n[C]. ISSCC 2010:386–387.

[2] CRANINCKX J,PLAS G V D. A 65 fJ/Conversion-Step 0-to-50MS/s 0-to-0.7mW 9b Charge-sharing SAR ADC in 90nm Digital CMOS[C].ISSCC 2007:246-247.

[3] QIU L,TANG K,ZHENG Y,et al.A flexible-weighted nonbinary searching technique for high-speed SARADCs[J].IEEE Transactions on Very Large Scale Integration(VLSI) Systems,2016,24(8):2808-2812.

[4] NAKANE H,UJIIE R,OSHIMA T,et al.A fully integrated SAR ADC using digital correction technique for triplemode mobile transceiver[J].IEEE Journal of Solid-State Circuits,2014(11):2503-2514.

[5] PALANI R K,HARJANI R.A 220-MS/s 9-bit 2x timeinterleaved SAR ADC with a 133-fF input capacitance and a FOM of 37 fJ/conv in 65-nm CMOS[J].IEEE Transactions on Circuits and Systems ІI- Express Briefs,2015,62(11):1053-1057.

[6] VITEK R,GORDON E,MAERKOVICH S,et al.A 0.015 mm2 63 fJ/conversion-step 10 bit 220 MS/s SAR ADC with 1.5 b/step redundancy and digital metastability correction[C].Proceedings of the IEEE 2012 Custom Integrated Circuits Conference,2012:1-4.

[7] LI D Q,ZHU Z M,DING R X,et al.A 1.4-mW 10-bit 150- MS/s SAR ADC with nonbinary split capacitive DAC in 65nm CMOS[J].IEEE Transactions on Circuits and Systems II,2017,40(12):1012-1016.

[8] TSAI J H,et al.A 0.003 mm2 10 b 240 MS/s 0.7 mW SAR ADC in 28 nm CMOS with digital error correction and correlated-reversed switching[J].IEEE J.Solid-State Circuits,2015,50(6):1382-1398.

[9] XING D,YAN Z,CHAN C H,et al.Seven-bit 700- M S / s f o u r - w a y t i m e - i n t e r l e a v e d S A R A D C w i t h p a r t i a l V c m - b a s e d s w i t c h i n g . I E E E T r a n s [ J ] . V L S I Syst.,2017,25(3):1168-1172.

[10] FANG J,THIRUNAKKARASU S,YU X,et al.A 5-GS/s 10-b 76-mW Time-Interleaved SAR ADC in 28 nm CMOS [J].IEEE Transactions on Circuits and Systems І-Regular Papers,2017,64(4):1673-1683.

[11] CHAN C H,YAN Z,SIN S W,et al.A 5.5mW 6b 5GS/s 4×interleaved 3b/cycle SAR ADC in 65nm CMOS[C].IEEE ISSCC Dig.Tech.Papers,2015:466-467

[12] LIU C,CHANG S; HUANG G,et al.A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure[J].IEEE Journal of Solid-State Circuits,2010,45(4):731-740.

[13] LIU J,ZHU Y,CHAN C,et al.Uniform quantization theory-based linearity calibration for split capacitive DAC in an SAR ADC[J].IEEE Trans.Very Large Scale Integr.(VLSI) Syst.,2016,24(7):2603-2607.

[14] ZHU Y,CHAN C,SIN S,et al.A 35fJ 10 b 160 MS/s Pipelined-SAR ADC with decoupled flip-around MDAC and self-embedded offset cancellation[C].Solid State Circuits Conference,2011:61-64.

[15] ZHONG J,ZHU Y,CHAN C,et al.A 12b 180MS/s 0.068mm2 pipelined-SAR ADC with merged-residue DAC for noise reduction[C].ESSCIRC Conference 2016:42nd European Solid-State Circuits Conference,2016:169-172.

[16] ZANCHI A,CHANG D Y.A 16-bit 65-MS/s pipeline ADC with 80-dBFS SNR using analog auto-calibration in SiGe SOI complementary BiCMOS[J].IEEE Trans.Circuits Syst.II,Express Briefs,2008,55(12):2166-2177.

[17] ABBAS M,FURUKAWA Y,Komatsu S,et al.Clocked c o m p a r a t o r f o r h i g h - s p e e d a p p l i c a t i o n s i n 6 5 n m t e c h n o l o g y [ C ] . B e i j i n g : S o l i d S t a t e C i r c u i t s Conference,2010:1-4.

[18] GAO J,LI G,LI Q.High-speed low-power commonmode insen sitive dyn amic compara tor[J].Ele ctron . Lett.,2015,51(2):134-136.

[19] XU D,XU S,CHEN G.High-speed low-power and lowpower supply voltage dynamic comparator[J].Electron. Lett.,2015,51(23):1914-1916.

[20] XIN X,CAI J,XIE R,et al.Ultra-low power comparator with dynamic offset cancellation for SAR ADC[J].Electron. Lett.,2017,53(24):1572-1574.

[21] XU D,QIU L,ZHANG Z,et al.A Linearity-Improved 8 - b i t 3 2 0 M S / s S A R A D C W i t h M e t a - S t a b i l i t y Immunity Technique[J].IEEE Trans.Very Large Scale Integr.2018,26(8):1545-1553.

[22] CAO Z,YAN S,LI Y.A 32 mW 1.25 GS/s 6 b 2 b/step SAR ADC in 0.13μm CMOS[C].IEEE ISSCC Dig.Tech. Papers,2008:542–543.

[23] CHIO U F,WEI H G,ZHU Y.A self-timing switch-driving register by precharge-evaluate logic for high-speed SAR ADCs[C].IEEE Asia Pacific Conference on Circuits and Systems.2008:1164-1167.

[24] CHEN L,RAGAB K,TANG X,et al.A 0.95-mW 6-b 700- MS/s Single-Channel Loop-Unrolled SAR ADC in 40- nm CMOS[J].IEEE Transactions on Circuits and Systems II.,2017,64(3):244-248.

[25] SHU G,LUO L,SHU C,et al.Settling optimised sampleand- hold circuit with high-linearity input switch in 65 nm CMOS[J].Electron.Lett.,2010,46(22):553-555.

(本文来源于必威娱乐平台 杂志2021年12月期)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码