带有硅化物阻挡层的可控硅器件对维持电压的影响*

编者按:基于0.18 μm双极CMOS-DMOS(BCD)工艺,研究并实现了一种阳极和阴极两侧均加入硅化物阻挡层(SAB)的可控硅(SCR)器件,可用于高压静电放电保护(ESD)。利用二维器件仿真平台和传输线脉冲测试系统(TLP),预测和验证了SAB层对可控硅性能的影响。测量结果表明,在不增加器件面积的情况下,通过增加SAB层,器件的维持电压(Vh)可以从3.03 V提高到15.03 V。与传统SCR器件相比,带有SAB层的SCR器件(SCR_SAB)具有更高的维持电压。

*基金项目:国家自然科学基金(61704145,61774129,61827812);湖南省自然科学基金(2019JJ50609)

作者简介:曹佩,硕士研究生,主要研究方向为静电保护器件。E-mail:1207845172@qq.com。

汪洋,通讯作者,教授,主要研究方向为静电保护器件。E-mail:wangyang@xtu.edu.cn。

0 引言

在半导体器件的制造、运输和使用过程中,静电放电(ESD)是一种常见的现象。静电放电产生的瞬间的高压静电脉冲流经芯片引脚时,将会对芯片内部电路造成不可逆的破坏。可控硅(SCR)是一种用于ESD 保护的传统器件结构。与其他ESD 保护器件相比,传统的SCR 器件具有电导调制效应好、单位面积放电效率高、单位寄生电容小、鲁棒性好等优点[1]。然而,由于SCR 器件中的寄生三极管NPN 和PNP 开启之后,将会形成正反馈,使得SCR 器件的维持电压较低。目前关于提高可控硅的维持电压的报道包括增加额外寄生晶体管NPN[2]和堆叠[3],这些技术不仅增加了器件的维持电压Vh ,而且增加了面积。分割器件的发射极[4]和在N 阱中加入浮空N + 注入[5]来增加可控硅的维持电压,虽然很大程度上维持电压得到了提升,但是器件的失效电流明显减小,同时器件泄放电流的能力降低。本文基于 0.18 μm 双极 CMOS-DMOS(BCD)工艺制备了传统SCR 器件以及SCR_SAB 器件,通过理论分析、公式推导和TCAD 仿真研究了SAB 层对维持电压的影响。通过TLP 测试结果表明,采用SAB 层的SCR 器件可以在不增加器件面积的情况下获得更高的维持电压。

1 器件结构

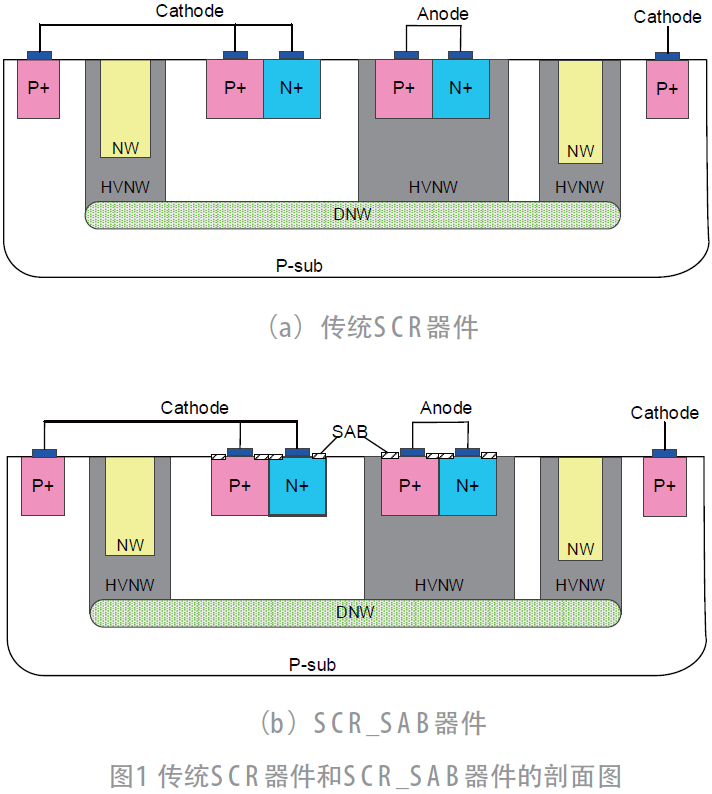

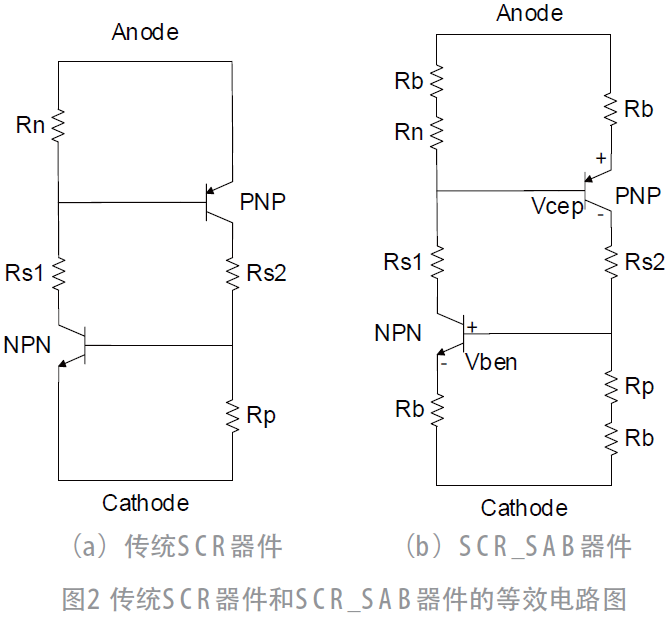

传统SCR器件的剖面图和等效电路图分别如图1(a)和图2(a)所示。寄生PNP管的发射极P + 连接器件阳极,寄生NPN 管的发射极N + 连接器件阴极。Rs1 和Rs2 分别表示半导体中的寄生电阻。Vcep 和Vben 分别是寄生三极管PNP 和NPN 的集电极- 发射极电压和基极- 发射极电压[6]。传统SCR 器件的等效电路如图2a 所示,包括NW 电阻Rn 和P-sub 电阻Rp,以及寄生晶体管NPN和PNP。SCR_SAB 器件的剖面图和等效电路图分别如图1(b)和图2(b)所示。Salicide-blocking(SAB)层用于阻止硅化物的形成,从而形成镇流电阻( Rb )[7]。因此,与传统SCR 器件相比,SCR_SAB 器件的路径上增加了镇流电阻Rb。

2 工作原理

如图1(a)所示,当正的ESD电流冲击器件的阳极时,当电压达到一定程度时,反偏结HVNW 和P-epi 会发生雪崩击穿,雪崩击穿会产生大量的电子- 空穴对,空穴将经过P-epi 电阻Rp 到达器件阴极的P + 注入,此时随着空穴数量的增多,寄生NPN 管的BE 结电压Vbe 将会逐渐增大,当Vbe增加至0.7 V 时,寄生的NPN 管将会开启。开启后的NPN 管会给寄生PNP 管的基极提供电流,使得寄生PNP 管随着寄生NPN 管的开启而开启,2 个寄生的三极管之间将会形成正反馈机制,SCR 器件此时处于闩锁状态,器件开始泄放大电流[8],等效电路图如图2(a)所示。

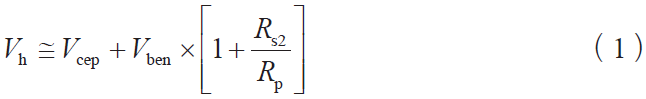

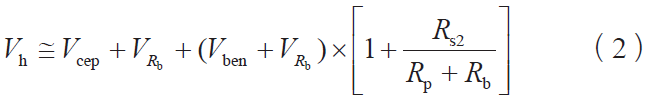

当寄生NPN 管和PNP 管都被触发时,SCR 器件开启。此时,SCR 器件的维持电压的计算公式可以表示为[9]:

对于SCR_SAB 器件来说,由于增加了SAB 层,所以电流路径上增加了镇流电阻Rb 。当SCR 路径完全开启时,器件的维持电压将会发生变化。此时,SCR_SAB 器件的维持电压公式可以表示为:

其中,VRb是镇流电阻的电压。对比式(1)和式(2),镇流电阻Rb可以提高SCR_SAB 器件的维持电压。镇流电阻Rb越大,器件的维持电压越大。

3 TCAD仿真结果与分析

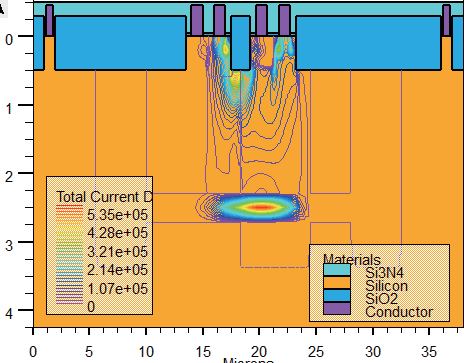

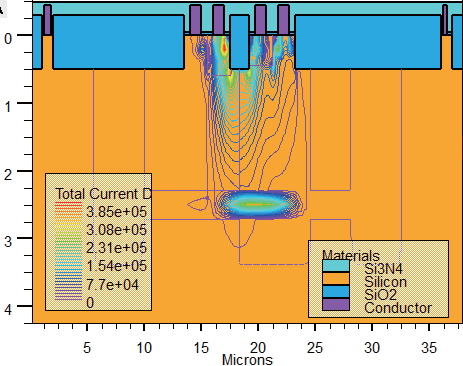

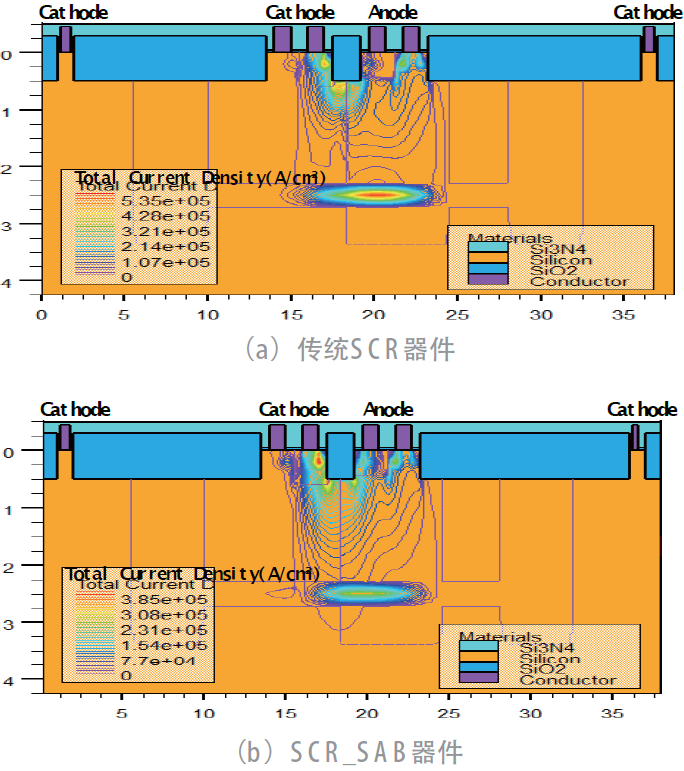

为了进一步了解该器件的工作原理,通过TCAD 二维瞬态器件仿真研究了传统SCR 器件和SCR_SAB 器件的工作机理。图3 显示了在80 ns , 0.06 A 的正向电流脉冲下传统SCR 器件和SCR_SAB 器件的总的电流密度分布情况。

图3(a)显示了在80 ns 的情况下传统SCR 器件的总的电流密度分布,从图中可以看出大部分的电流集中在厚氧附近。图3(b)显示了在80 ns 的情况下SCR_SAB 器件的总的电流密度分布,对比传统SCR 器件,在SCR_SAB 器件的电流路径中加入了镇流电阻Rb ,使得放电电流分布更加分散和深入。

(a)传统SCR器件

(b)SCR_SAB器件

图3 在80 ns、0.06 A的正向电流脉冲下,传统SCR器件和SCR_SAB器件的总的电流密度分布

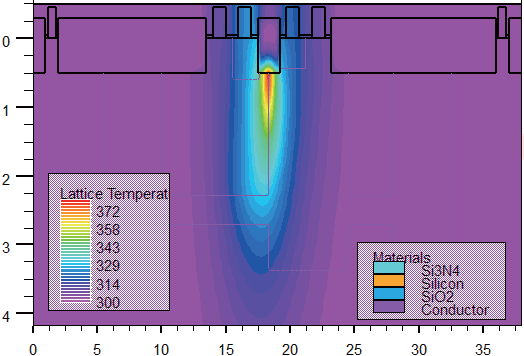

与传统SCR 器件相比,SCR_SAB 器件的电流路径流的更深。这是因为器件增加了SAB 层之后,该区域增加了镇流电阻,进而使得该区域的表面电场增大,而强电场则会抑制通过该区域的ESD 电流,并将其推入硅衬底的深部,电流路径将更长,最终获得更高的维持电压。热击穿作为ESD 保护器件的主要失效机制之一,经常被用来验证器件的失效能力。静电放电器件的热失效是由于器件内部的局部热效应引起的[10]。通过对晶格温度分布的瞬态模拟,比较了整个器件的温度。

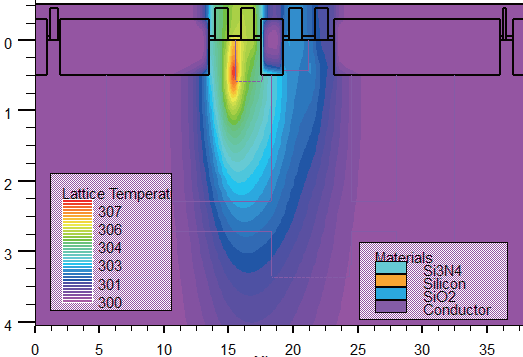

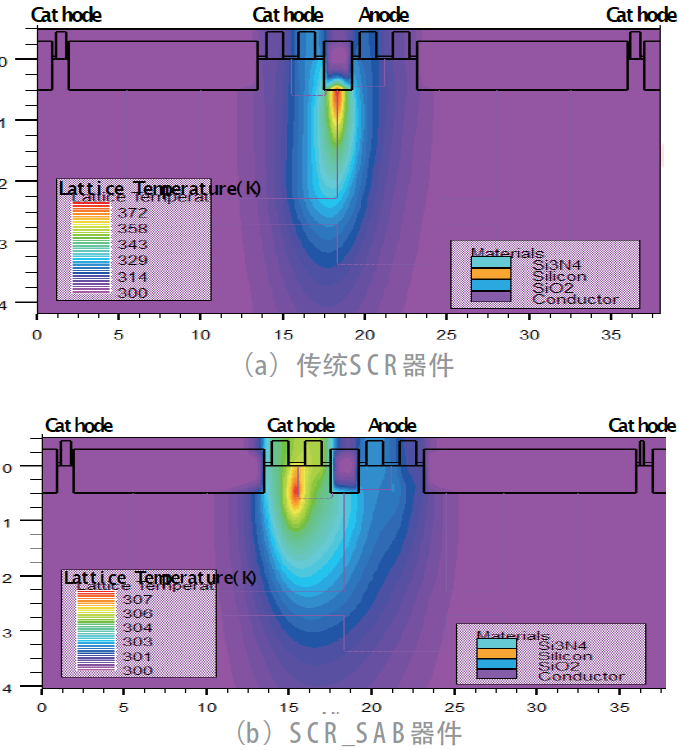

(a)传统SCR器件

(b)SCR_SAB器件

图4 在80 ns、0.06 A的正向电流脉冲下,传统SCR器件和SCR_SAB器件的晶格温度分布

为了观察传统SCR 器件和SCR_SAB 器件的晶格温度,在阳极上施加脉冲宽度为100 ns , 0.06 A 的电流脉冲。两种器件的晶格温度模拟图如图4 所示,当电流脉冲宽度为80 ns 时,传统SCR 器件的最高晶格温度约为372 K ,热点分布较小且位于器件表面。SCR_SAB器件的最高晶格温度为307 K ,热点分布面积较大且位于器件内部。由上述仿真结果分析可知,SCR_SAB 器件由于SAB 层的作用,使得电流路径更长,维持电压更高。由晶格温度分布图可知,加了SAB 层之后的SCR 器件的热点分布更大。

4 测试结果和讨论

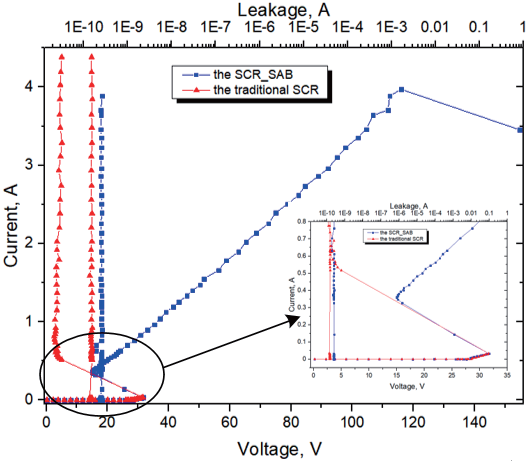

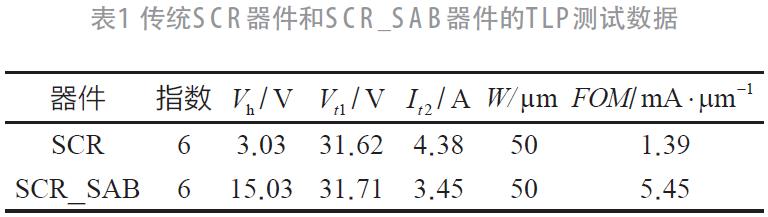

为了验证上述分析,采用Thermo Scientific Celestron(TLP)测试系统对器件的I −V曲线进行了测试。采用的是上升时间为10 ns ,宽度为100 ns 的电流脉冲方波。

图5 传统SCR器件和SCR_SAB器件的TLP特性对比

两种器件的测试结果如图5 和表1 所示。可以看出,这两种器件的触发电压相似,约为31 V 。这是因为器件的雪崩击穿面是相同的。如表1 所示,SCR_SAB 器件的维持电压高达15.03 V,而传统SCR 器件的维持电压仅为3.03 V 。与传统SCR器件相比,SCR_SAB 器件的失效电流由4.38 A 减小到3.45 A ,且导通电阻很大。以上分析表明,在传统SCR

器件中加入SAB 层可以提高器件的维持电压。为了进一步评估传统SCR 器件和SCR_SAB 器件的ESD 保护性能,在这里采用以下定义的公式来评估器件的ESD 性能:

其中,FOM 是器件的品质因子,W是器件的总宽度,Vt1是触发电压, Vh是维持电压, It2是失效电流。如表1 所示,传统SCR 器件的FOM 为1.39 mA/μm ,SCR_SAB 器件的FOM 为5.45 mA/μm 。对比两种器件,SCR_SAB 器件的FOM 有显著提高。

5 结束语

本文研究和讨论了传统SCR 器件和SCR_SAB 器件的维持电压。通过理论分析和TCAD 二维器件仿真,分析了SCR_SAB 器件的维持电压升高的原因。通过 TLP 测试,得到了该器件的I −V曲线。测试和仿真分析表明,SAB 层提高了SCR 器件的维持电压。在相同的器件面积下,SCR_SAB 器件的维持电压高达15.03 V ,是传统SCR 器件的5 倍。分析结果表明,SAB 层对提高器件的维持电压具有指导意义。

参考文献:

[1] KEPPENS B,MERGENS M P J,TRINH C S,et al.ESD protection solutions for high voltage technologies[J]. Microelectronics Reliability,2005,46(5):677-688.

[2] HUANG Y C,KER M D.A latchup-immune and robust SCR device for ESD protection in 0.25μm 5V CMOS process[J].IEEE Electron Device Letters,2013,34(5):674-676.

[3] DAI C T,KER M D.Comparison between high-holdingvoltage SCR and stacked low-voltage devices for ESD protection in high-voltage applications[J].IEEE Transactions on Electron Devices,2018:798-802.

[ 4 ] L I U Z W , L I O U J J , V I N S O N J . N o v e l s i l i c o n - controlled rectifier(SCR) for high-voltage electrostatic discharge (ESD) applications[J].IEEE Electron Device Letters,2008:753-755.

[5] KO J,KIM H,JEON J.Gate bounded diode triggered high holding voltage SCR clamp for on-chip ESD protection in HV ICs[C].35th Electrical Overstress/Electrostatic Discharge Symposium Las Vegas,NV 2013,2013:1-8.

[ 6 ] K E R M D , C H E N Z P . S C R d e v i c e w i t h d y n a m i c holding voltage for on-chip ESD protection in a 0.25-um fully salicided CMOS process[J].IEEE Trans Electron Devices,2004,51(10):1731-1734.

[7] HSU H C,CHEN C M,KER M D.Methods to improve machine-model ESD robustness of NMOS devices in fullysalicided CMOS technology[J].IEEE VLSI-TSA International Symposium on VLSI Technology,2005:19-20.

[8] CHEN X J,WANG Y,JIA D D,et al.An ESD robust high holding voltage dual-direction SCR with symmetrical I-V curve by inserting a floating P+ in PWell[J].Solid State Electronics,2019:107627.

[9] BANDYOPADHYAY A,VERMA P R,BHATTACHARYYA A B.LATCHSIM-a latch-up simulator in VLSI CAD environment for CMOS and BiCMOS circuits[C].Proceedings of 7th International Conference on VLSI Design,Calcutta,India,1994:339-342.

[10] LIANG W,DONG A H,LI H,et al.Characteristics of ESD protection devices operated under elevated temperatures[J].Microelectron Reliability,2016,66(Nov):46-51.

(本文来源于必威娱乐平台

杂志2021年9月期)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码