磁隔离栅驱动的电流双极调制和数字滤波解调技术研究

编者按:提出了一种适用于磁隔离栅驱动的电流双极调制和数字滤波解调技术,该技术以电流模式作为栅驱动在信号传输过程中的主要工作模式,使磁隔离线圈由重载变为轻载并降低信号驱动功耗;在信号检测方面,通过电平位移产生一对高电平互补信号,并在后续解调中使用数字逻辑电路滤除共模噪声,并以不同平台为主进行多次混合仿真,以改善磁隔离变压器模型与外围电路的匹配问题。最后,将信号的最大驱动电流减小到19 mA,通过数字滤波解调技术实现了50 kV/μs的共模噪声抑制能力,并实现了与脉冲极性编码传输方案相同级别的传输延迟(7.1 ns)

0 引言

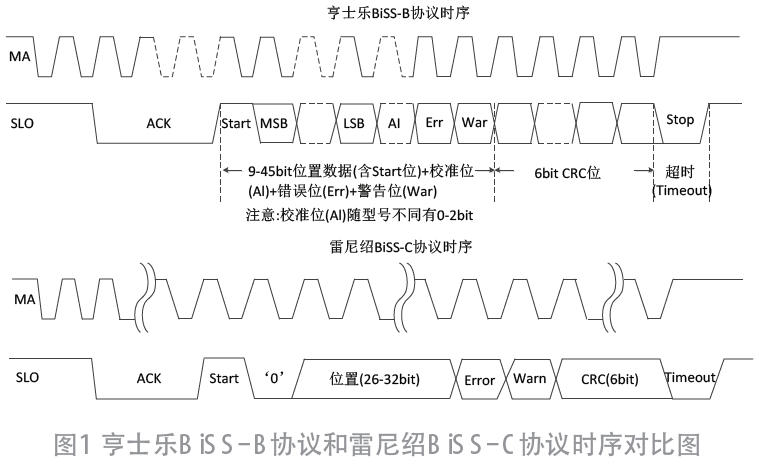

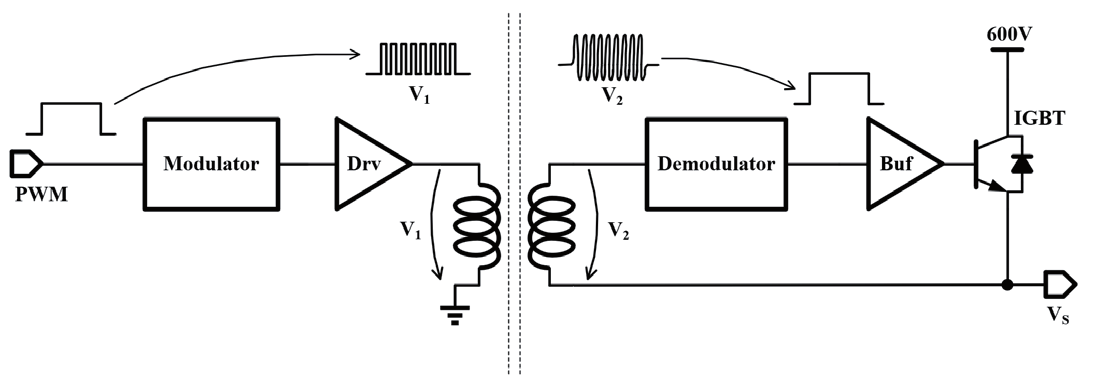

基于片上变压器的隔离式栅极驱动器已有广泛研究。然而,由于变压器线圈的驱动问题,难以同时实现磁隔离栅驱动的低功耗和高共模噪声抑制能力(CMR),也限制了传输延迟的进一步优化。图1 为磁隔离栅极驱动器的结构框图,其中PWM 信号经过调制后由初级驱动模块(Drv)驱动变压器初级线圈,并在次级线圈上感应出待解调信号V2。一种差分结构的片上变压器模型见图2,由于在集成中工艺和尺寸的限制,其通带频率的低频点一般需达到100 MHz,因此在工作频带内变压器的增益难以超过-3 dB,其电感也在100 nH 左右[1]。初级调制信号V1 需有足够驱动能力以在有限的增益下使待解调信号V2 的幅值能够被检测,这种情况下的峰值驱动电流将超过60 mA 以上[2],同时有限的dI/dt 也限制了电路延迟的减小。另一方面,不同的信号调制方式也将以通频带不同的方式影响变压器模型的设计,而当应用幅度调制时,电路功耗的增加换取了高的共模噪声抑制能力。

图1 简化的磁隔离栅驱动结构框图

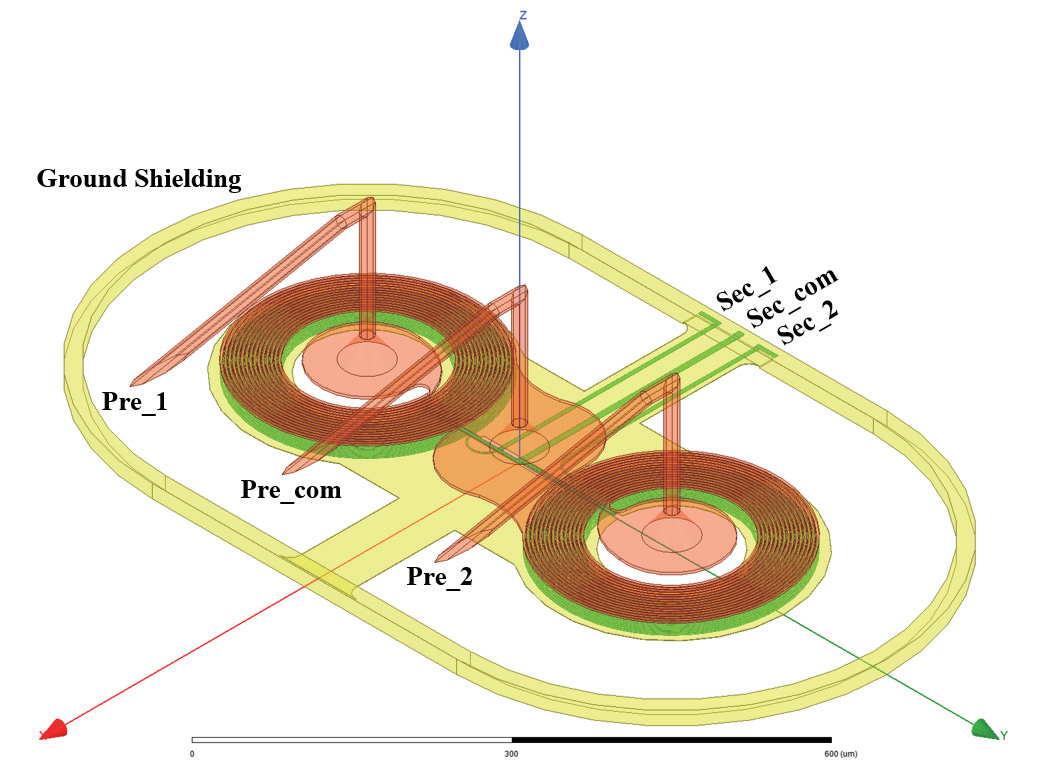

图2 片上差分变压器的ANSYS-HFSS模型

针对共模噪声抑制能力的进一步提升,已有多种方案:信号和噪声的不同传输路径,可提供磁隔离栅驱动(隔离器)的噪声分离和抑制思路。文献[3] 通过分析隔离器接收器侧线圈上电压偏移的噪声和信号频谱特征,利用高通滤波器和电压阈值来改善CMR;此外,还可通过时域的方法对噪声进行抑制。文献[4] 引入2个次级线圈,分别将两线圈的同名端和异名端作为高侧栅极控制信号输入和浮动地,这样通过次级线圈的交叉配置可将有用的差模信号加倍,抵消无用的共模噪声信号,以此来抑制隔离器的噪声;文献[5] 另辟蹊径,以数字的方式改善隔离器的信噪比。其将隔离器的噪声考虑为栅极控制信号的信号抖动,该抖动信号通过随机改变信号转换的时间瞬间而将相当大的宽带噪声引入隔离器的输出。基于此种分析,文献在传统隔离器中新增了一路具有低频率抖动的时钟信号隔离通道,该时钟信号与控制信号共同作为触发器的输入,利用时钟信号屏蔽控制信号的抖动,从而达到抑制噪声,提高信噪比的目的。针对以上问题,本文以电流模式作为隔离器在信号传输过程中的主要工作模式,而在隔离器次级采用与上述传统共模噪声分离和抑制方案不同的数字滤波解调技术。本文完成了基于ANSYS Electromagnetics Suite 平台的混合仿真(见图3),并与Cadence 平台的结果进行了比较,以保证仿真的准确性。最后,实现了磁隔离栅驱动的低功耗,高CMR 和低传输延迟。

1 电路分析

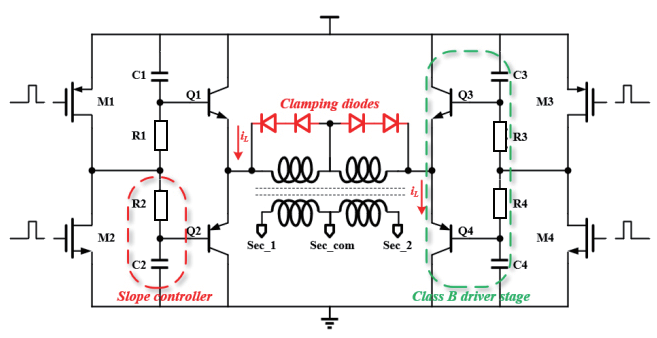

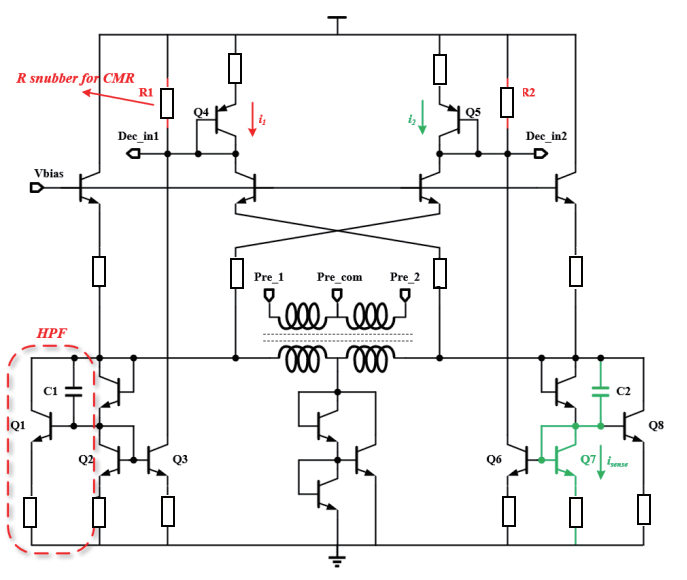

如图4 所示,Q1~Q4 构成双极性调制电路,其形成的B 类驱动级用作电流源,并将变压器从重负载变为轻负载。在这种情况下,磁场的变化直接受到dI/dt 的影响,相比电压模式,反向的dI/dt 使差分变压器完全消磁,并通过双极性电流调制产生更少的谐波。图中的钳位二极管进一步限制线圈驱动信号中的电压信号。次级线圈的信号检测仍然由电流主导(见图5),避免了初级线圈的驱动问题,并降低了峰值驱动电流。检测电路的高通滤波网络HPF 产生有效电流信号isecse,并通过电流镜生成i2(或i1)。为限制VDEC_in2(或VDEC_in1)超过电源轨,在图中设置了吸收电阻R1 和R2。

图3 基于ANSYS Electromagnetics Suite的混合仿真

图4 电流双极调制电路

图5 电流检测电路

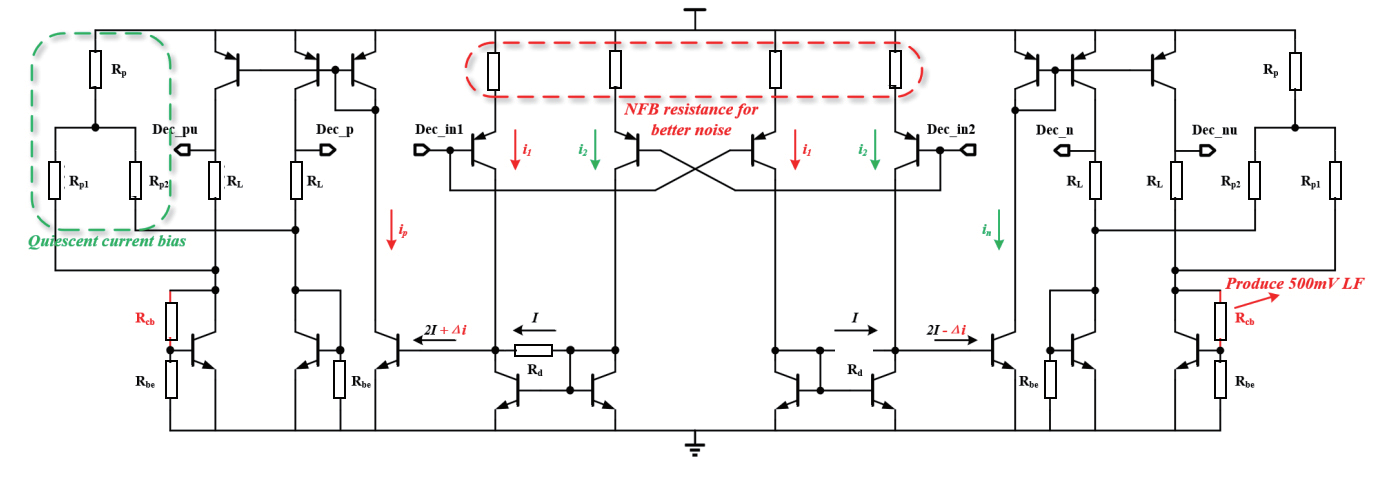

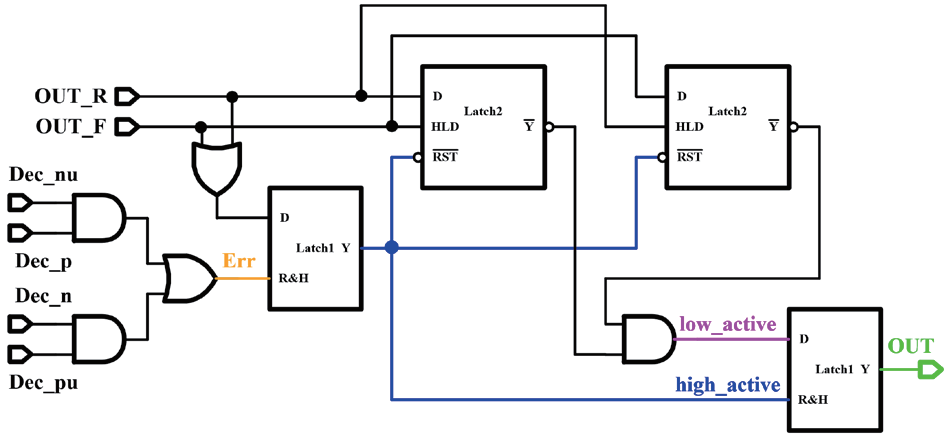

图6 为带电平位移输出的电流差分放大器,其由Rcb产生2 个500 mV 的电平移位信号Dec_pu 和Dec_nu。此两路信号配合Dec_p 和Dec_n 将得到一对高电平互补的数字逻辑信号,它们在PWM 高电平调制时互为反相,而在PWM 低电平调制时均为低电平。图7 为检测比较器的预放大电路,其输入部分与图6的电流差分放大器的输出仍可看为电流镜像的形式。该预放大电路具有额外的启动电路和正反馈环路,其输出具有锁存能力,能快速识别出5 ns 内两输入波形的大小。图8 为本文提出的数字滤波解调技术的简化核心电路,该电路能正常解调出PWM 控制信号,并分离出噪声信号。OUT_R 和OUT_F 信号为由比较器输出的一对高电平互补数字逻辑信号,图6 所示电流差分放大器输出的四路信号共同产生Err 信号,当其为高时表示可能存在错误。噪声分离的基本思路是利用锁存器、Err、OUT_R 和OUT_F 信号分别准确有效地识别PWM 控制信号的高电平和低电平,并分别输出包含该信息的数字信号low_active 和high_active,再通过锁存器合成最终解调信号OUT。表1 为图8 中两类锁存器Latch1 和Latch2 的真值表。

图6 电流差分放大器电路

图7 预放大电路

图8 简化的电流滤波解调电路

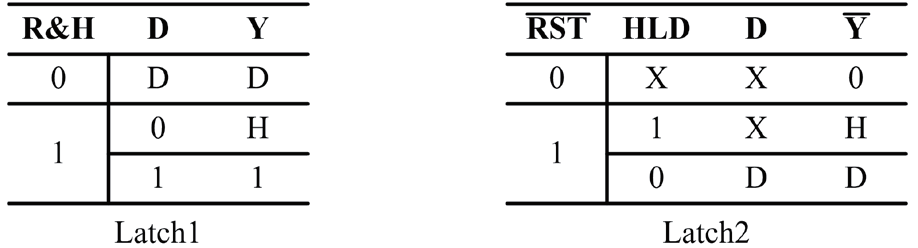

表1 Latch1和Latch2的真值表

注: D = Input data H =Hold X = Don’t care.

2 仿真结果与讨论

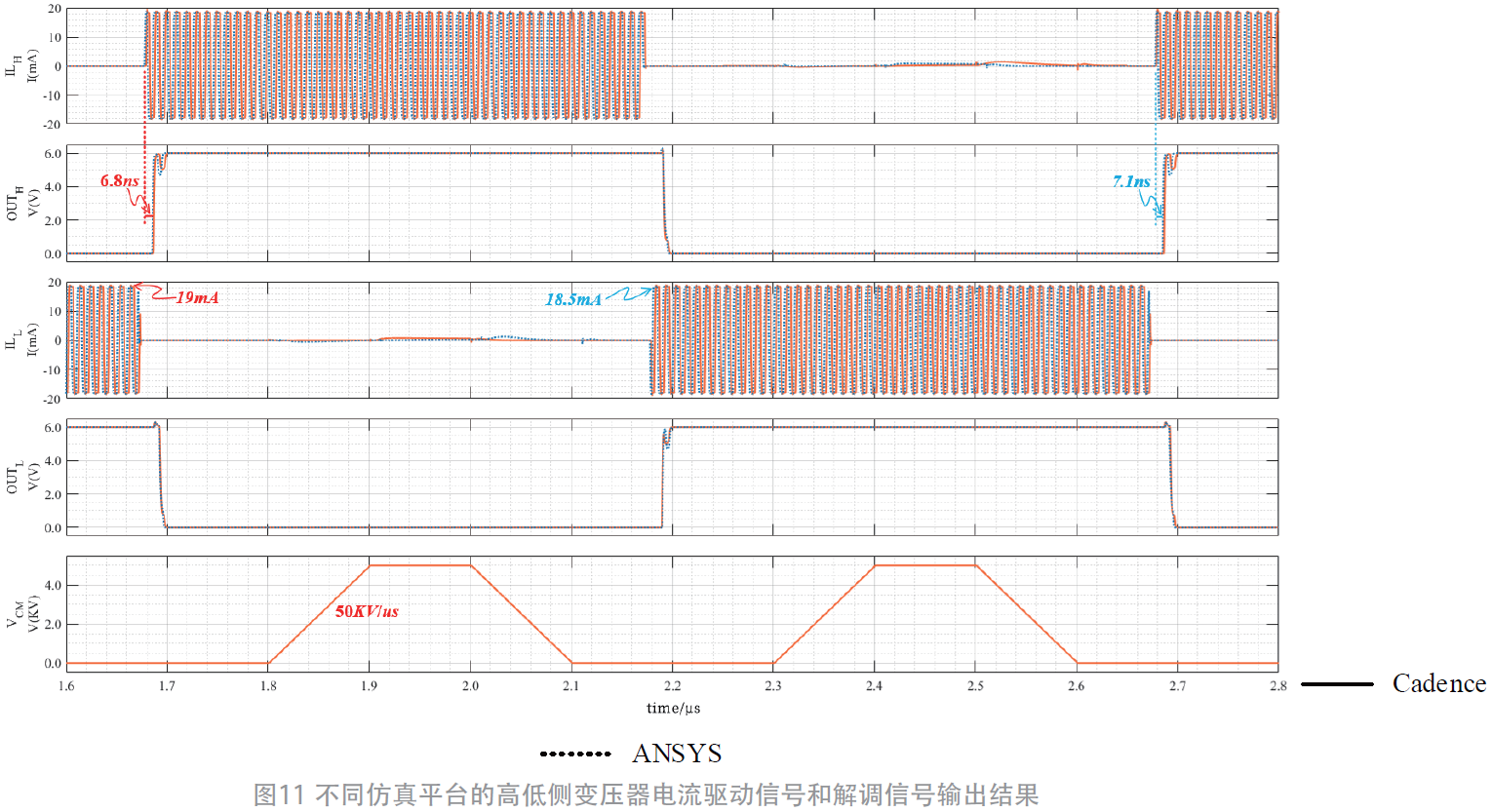

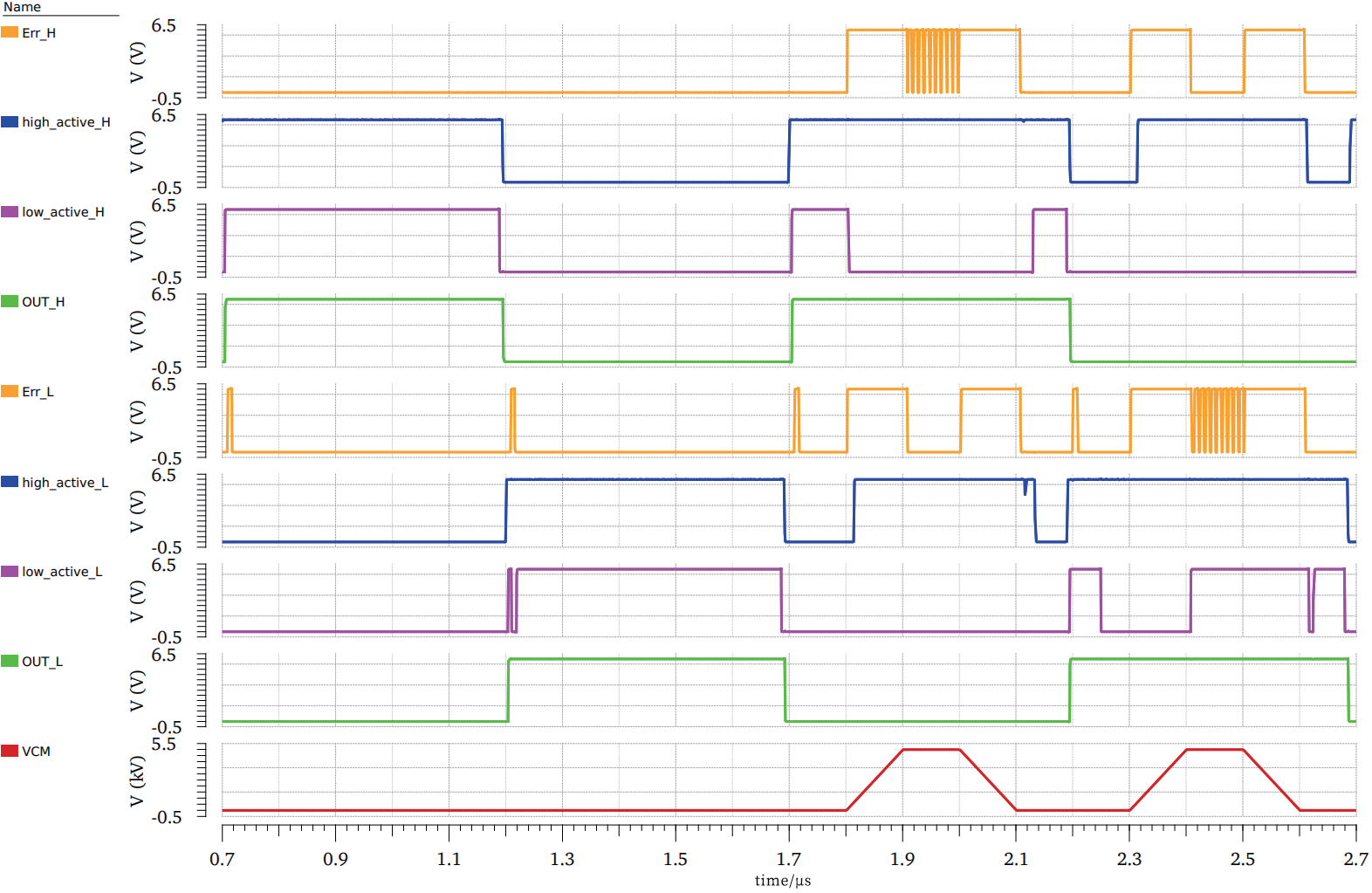

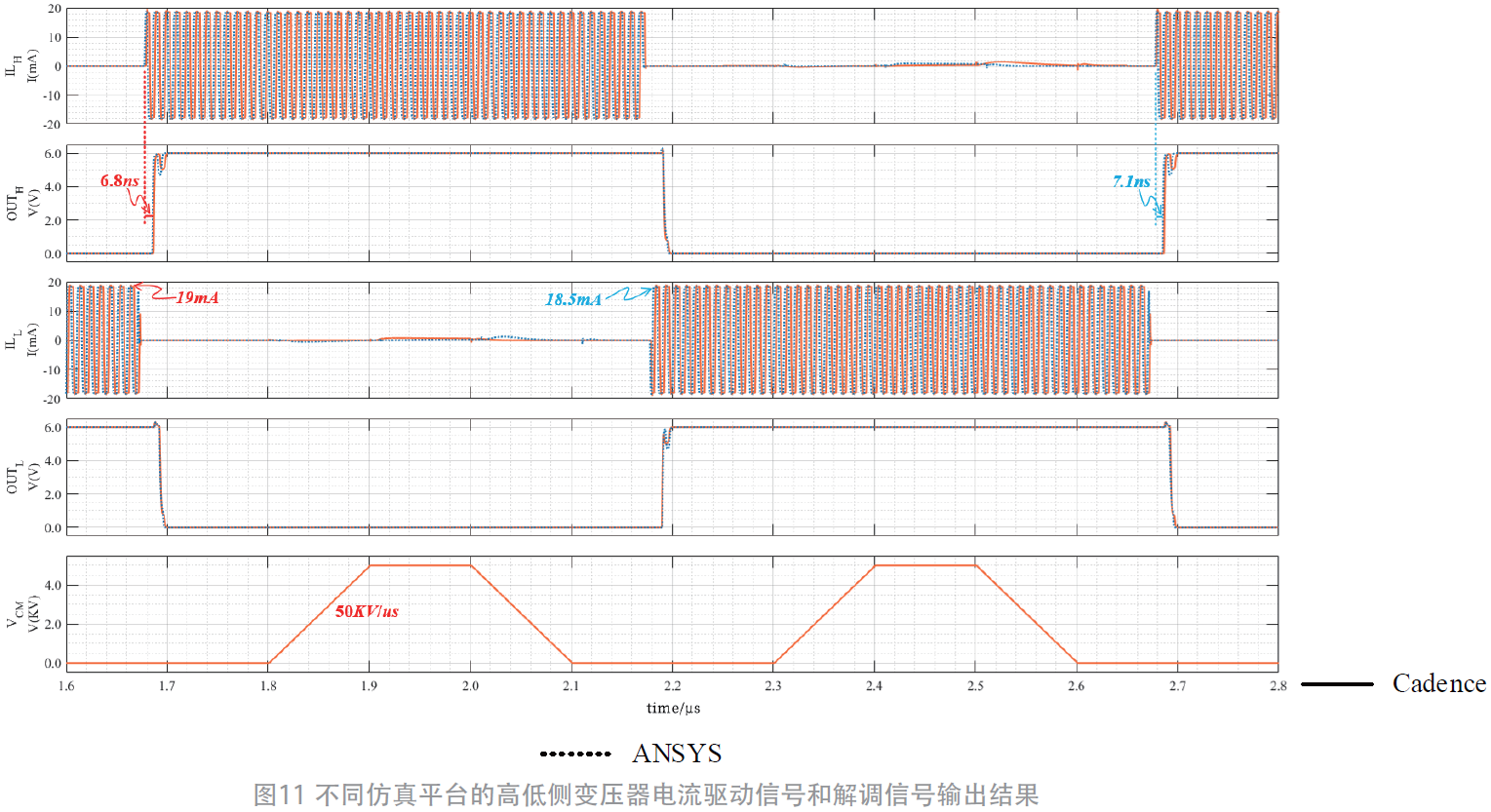

图9 展示了由图6 电流差分放大器输出的四路信号通过比较得到一对高电平数字逻辑信号的过程。Design & Application 元器件图10 为图8 所示数字滤波解调电路滤除共模噪声并输出正常PWM 控制信号的过程,图中分别给出了单个IGBT 桥高侧和低侧驱动解调过程的信号波形。VCM为模拟的50 kV/μs 共模噪声信号,该信号加在低侧磁隔离栅驱动次级输出级的浮动地和初级信号输入级的理想地之间。在未出现共模噪声时,高低侧的low_active和high_active 均正常并正常输出OUT 控制信号;当共模噪声信号在高侧的PWM 信号高电平和低侧的PWM低电平出现时,高低侧的Err 信号做出反应并分别破坏low_active_H 和high_active_L 信号的正常电平状态,而不影响low_active_L 和high_active_H 信号;同样,当共模噪声信号在高侧的PWM 信号高电平和低侧的PWM 低电平出现时,高低侧的Err 信号仍做出反应,并不影响low_active_H 和high_active_L 信号。如此,再经过图8 的锁存器Latch1 的处理,输出正常控制信号OUT,屏蔽了共模噪声信号VCM 对正常控制信号的输出的影响。图11 展示了分别以Cadence 和ANSYS 平台为主进行混合仿真所得结果的对比, 图中比较了单个IGBT 桥高侧和低侧驱动的变压器电流和解调后的信号,所得变压器峰值驱动电流小于19 mA(Cadence) 和18.5 mA(ANSYS),传输延迟为6.8 ns(Cadence)和7.1 ns(ANSYS)。

图9 电平位移信号和其比较结果

图10 通过数字滤波解调得到正常输出信号

3 结束语

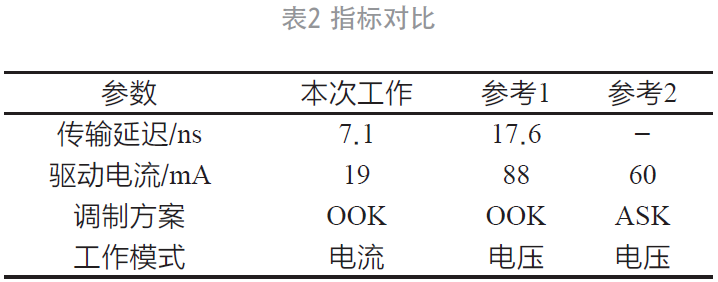

本文提出了一种适用于磁隔离栅驱动的电流双极调制和数字滤波解调技术,进一步降低了磁隔离栅驱动的动态功耗,并确保了其50 kV/μs 的共模噪声抑制能力。磁隔离栅驱动采用OOK 调制模式,其变压器的峰值驱动电流降低至19 mA,为文献[6] 和文献[2] 的32%;传输延迟降低为7.1 ns,达到与脉冲极性编码相同的水平,表2 总结了相关性能指标的对比。

参考文献:

[1] PENG L,WU R,FANG X,et al.A fully integrated 3D TSV transformer for high-voltage signal transfer applications[J].ECS Solid State Letters, 2013,2(5):29-31.

[2] LOMBARDO P,FIORE V,RAGONESE E,et al.A fullyintegrated half-duplex data/power transfer system with up to 40Mb/s data rate, 23mW output power and onchip 5kV galvanic isolation[C].2016 IEEE International S o l i d - S t a t e C i r c u i t s C o n f e r e n c e ( I S S C C ) , S a n Francisco,CA,2016:300-301.

[3] KAERIYAMA S,UCHIDA S,FURUMIYA M. A 2.5kV isolation 35kV/us CMR 250Mbps 0.13mA/Mbps digital isolator in standard CMOS with an on-chip small transformer[C].2010 Symposium on VLSI Circuits,2010:197–198.

[4] LUO Y,FANG J,ZHANG E,et al.A novel cross-over CMR transformer technology for magnetic isolation gate driver applications[C].2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD),Shanghai, China,2019:123-126.

[5] MAUERER M,TÜYSÜZ A,KOLAR J W.Low-jitter GaN E-HEMT gate driver with high common-mode voltage transient immunity[J].IEEE Transactions on Industrial Electronics,2017,64(11): 9043-9051.

[6] JAVID M,BURTON R,PTACEK K,et al.CMOS integrated galvanically isolated RF chip-to-chip communication utilizing lateral resonant coupling[C].2017 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Honolulu, HI, 2017:252-255.

(本文来源于必威娱乐平台 杂志2021年8月期)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码