赛灵思器件上的 INT4 优化卷积神经网络(2)

接上期http://www.eepw.com.cn/article/202009/418351.htm

赛灵思 DSP 片上的 INT4 优化

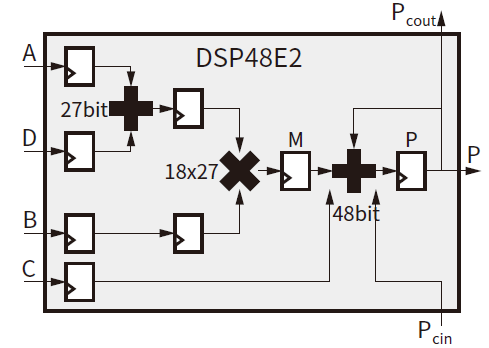

使用 DSP 硬件资源可实现乘法和累加 (MAC) 占用硬件资源较少。经优化后,DSP 能够在 16nm 或 28nm 器件上处理尽可能多的 MAC 运算。以 16nm 为例,赛灵思可编程器件中 UltraScale™ 架构的 DSP48E2 片就属于专用片[参考资料 11]。DSP48E2 片由一个 27x18 二进制补码乘法器和一个 48 位累加器构成。如图 3 所示,MAC 能使用赛灵思 DSP 片完成。

图 3:MAC 模式下的 DSP48E2 片

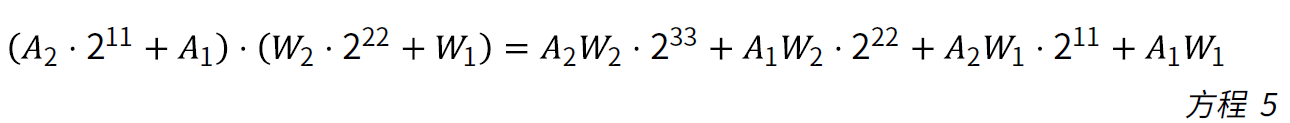

INT4 优化

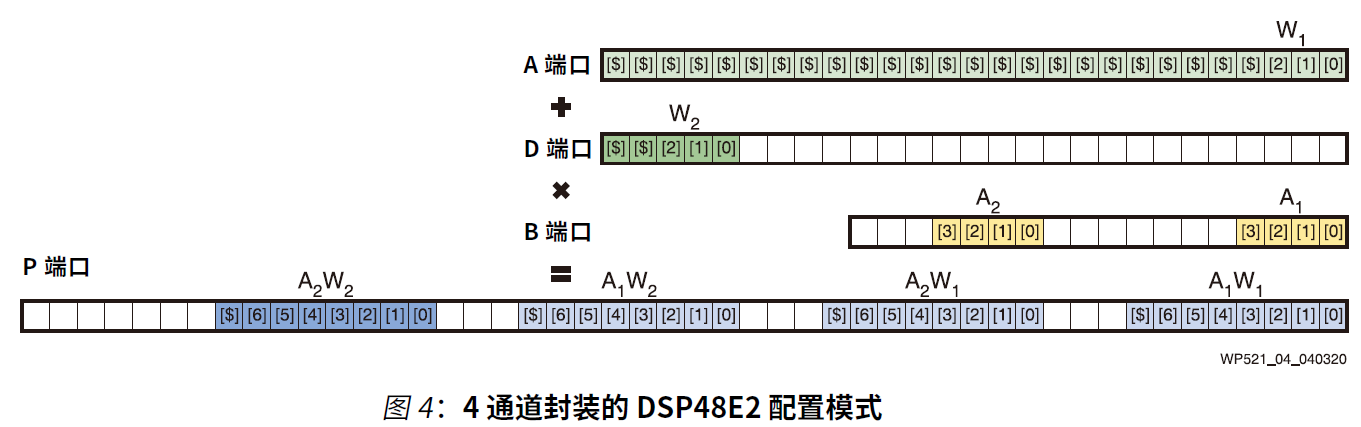

在低精度 MAC 运算中,相乘方式是 a*b。其中 a 是 4 位无符号激活参数数据,b 是 4 位有符号权重参数数据。DSP48E2 片可被配置成 4 通道乘法运算,如图 4 所示。

DSP48E2 片的端口 A 是 27 位宽。端口 B 是 18 位宽。int4 * uint4 相乘产生的结果至少有 8 位宽。充分利用 DSP 资源的前提是在多个相乘被打包在一起时,确保输出结果保持正确。为确保这一点,通道之间添加了保护位。当四个 MAC 通道被打包在一起时,需要在两路输入间布置足够的保护位。根据 DSP48E2 片的设计,保护位被设置为 3 位:

第一个通道 A1*W1 被布置在对应端口的 4LSB 上。下一个通道 A2*W1 需要移位至少 8 位才能正确计算。第二个通道与第一个通道共享权重参数数据 W1。端口 B 中的 A2 移位 11 位。3 位保护位用于最大化 DSP 资源的利用。最后一个计算元 W2 被分配给端口 A。最后两个通道是 A1*W2 和 A2*W2。权重参数是有符号数据。在相乘开始前,使用 27 位预加法器打包两个权重参数数据。因为 W1 需要符号扩展,所以 W2 不能布置在 D 端口的四个 MSB 上[参考资料 12]。如果 W2 在 MSB 中,当 W1 < 0 且 W2 = -8 时,预加法器就会溢出。后 48 位加法器可用作累加器,通过级联对之前层次的 DSP 结果进行相加。单个 DSP48E2 就能在单个时钟周期内实现四通道 MAC。

结果的位宽在累加后增大。硬件友好型量化器是一组移位寄存器,它可以通过指令控制移位的位数。移位运算是硬件友好型的。在低精度 CNN 中,卷积能够使用两种量化方法之一。一种是逐计算元地输出 8 位。另一种是对下一卷积输出 4 位。通过算法优化,两种量化方法都能量化成 2k 步长。差别在于输出数据的位宽以及它们是否是有符号数据。

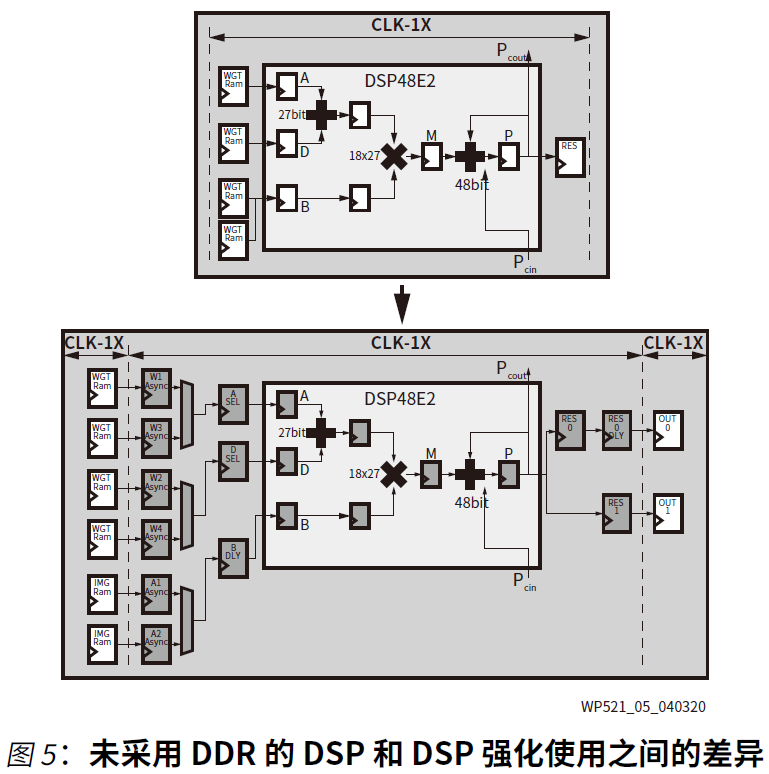

DSP 强化使用

DSP 双数据速率 (DDR) 技术被用于改进由 DSP48 片实现的性能[参考资料 13]。因此需要为 DPU 提供两个输入时钟:一个用于通用逻辑,另一个用于 DSP 片。未采用 DSP DDR 技术的 DPU 和采用强化使用模式的 DPU 之间的差异如图 5 所示。

面向 CNN 要求的计算图

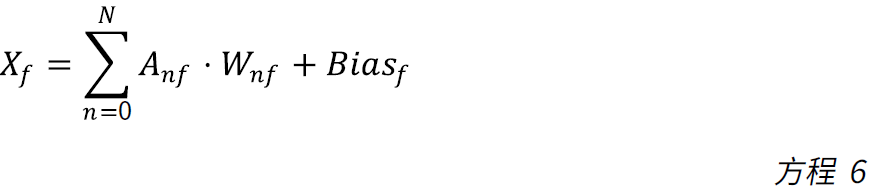

卷积是 CNN 网络的主要计算要求。卷积的实际计算任务如下:

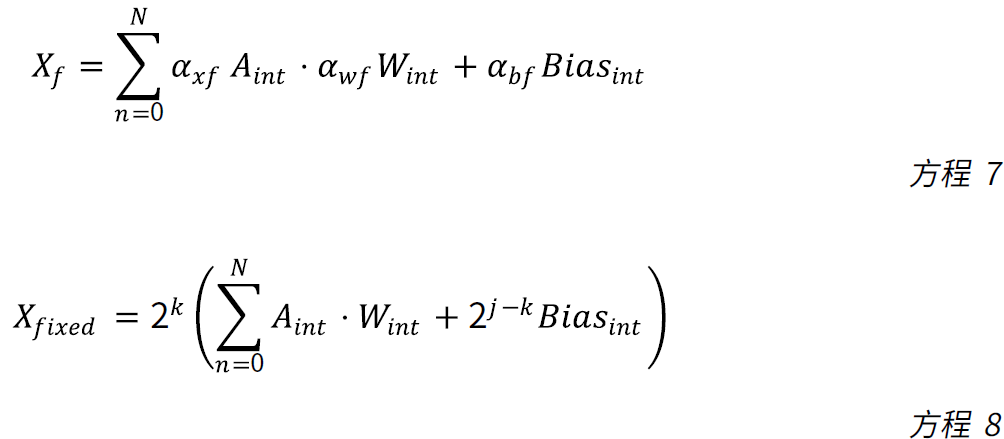

其中Anf 是浮点特征图,Wnf 是浮点权重。其本质是 MAC 运算。根据赛灵思的新颖量化感知训练解决方案,浮点的卷积计算按如下方式进行量化:

其中 axf、awf 和abf 是标度。这些浮点参数被转换成2k*2k。这是一种硬件友好型标度,能够在 FPGA 中使用移位运算轻松实现。

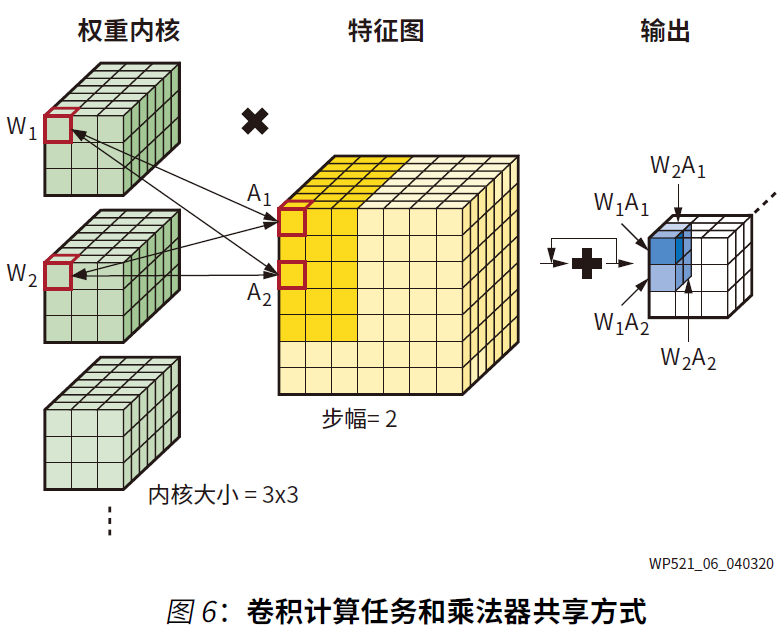

DSP 块在一个时钟周期中需要两个权重和两个特征。其中的每一个都能共享,如图 6 所示。

在 W_1 所在的内核里,内核宽 * 内核高 * 通道的全部像素需要与特征相乘,然后加总成一个输出像素。在同一层,每个权重内核共享同样的特征图。两个被打包的权重需要来自两个不同的权重内核。每一步中当权重内核滑移到特征图上时,对应的特征数据就需要与该权重内核相乘。一个 DSP48 块中的两个特征应来自同一特征图里的不同滑动窗口。

模型量化与性能仿真

下面的章节讲解量化感知训练中使用的 CV 任务。这些任务包括图像分类、姿态估计、2D 检测、3D 检测、语义分割和多任务。

基准分类模型

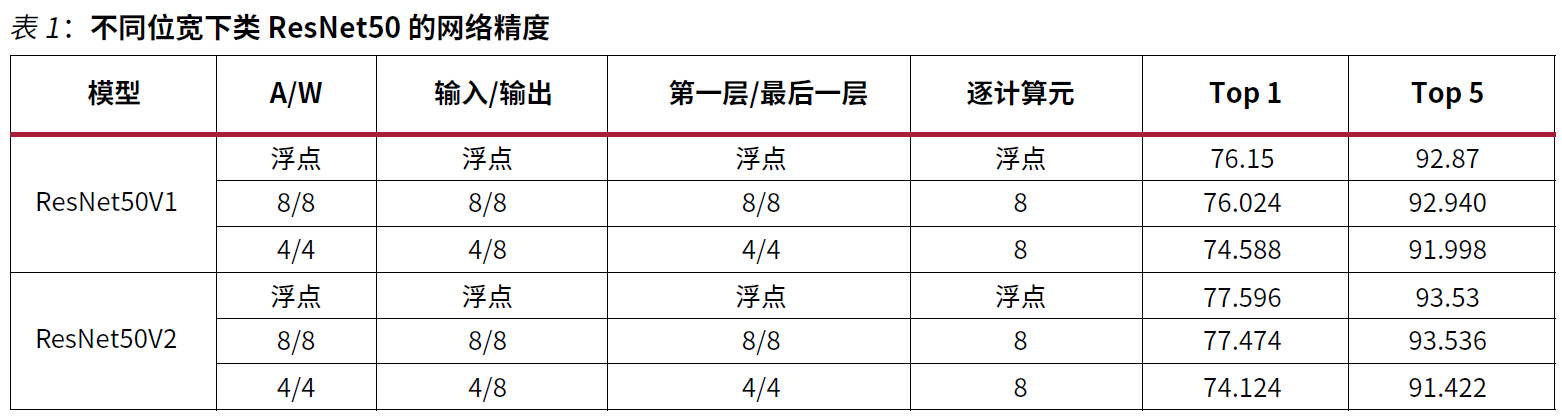

在完成 ImageNet 分类数据集上的实验后得到如下结果。网络包括 ResNet50-V1、ResNet50-V2。在所有实验中,数据集均从浮点模型进行微调。所有偏差参数都量化到 8 位。实验结果如表 1 所列。

基准分类模型的结果参见表 1。它体现了这种方法的有效性。具体对 ResNet50V1 而言,4 位 XDPU 解决方案与 8 位 XDPU 解决方案在前 1 精度上的差距仅有 1.4%,在前 5 精度上的差距仅有 0.9%。

实时 ADAS 模型,包括姿态估计、检测、分割、多任务等。

为进一步验证量化方法的通用性,也在真实场景下开展了其他 CV 任务。

姿态估计

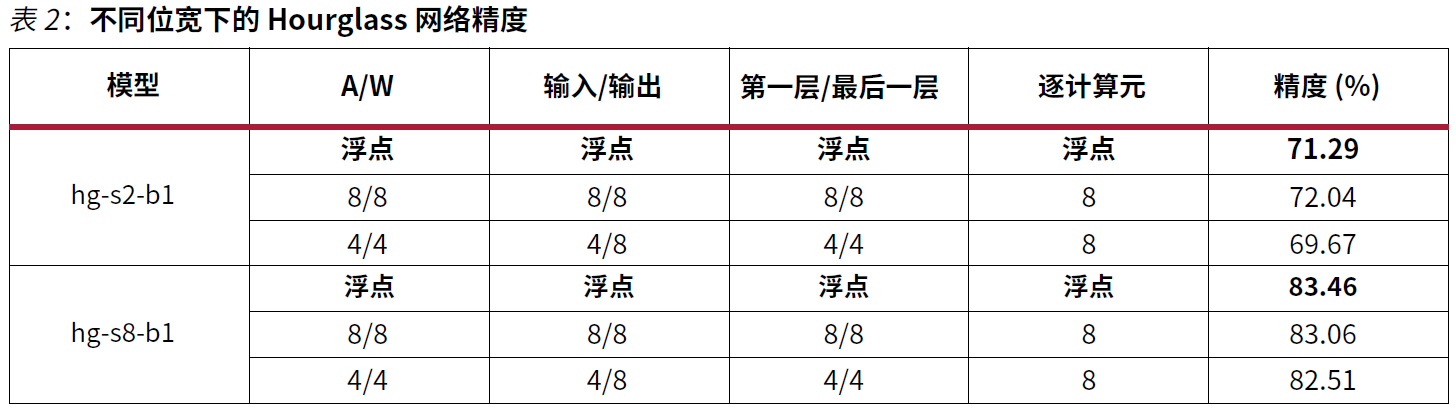

姿态估计任务使用更加复杂的堆叠 Hourglass 网络[参考资料 14]。通过在 MPII[参考资料 15]数据集上开展姿态估计实验,评估了逐层模式下两个网络结构的精度。结果参见表 2。

在表 2 中,hg-s2-b1 意味着堆栈数量是 2,块数量是 1。Hg-s8-b1 意味着堆栈数量是 8,块数量是 1。表 2 证明赛灵思 INT4 量化解决方案实现了可媲美浮点模型的精度。

2D 检测

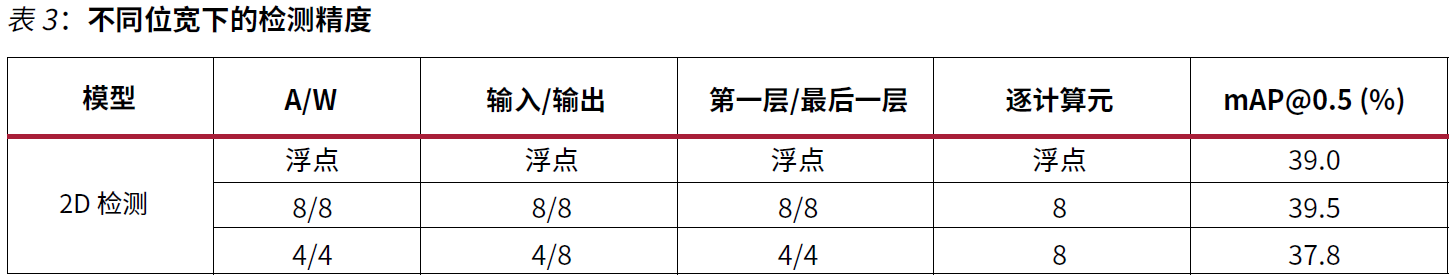

在 ADAS 系统中,BDD100K[参考资料 16]数据集用于 2D 检测。此外,FPN 结构被添加到 ResNet18-SSD 中,用作检测网络。实验结果如表 3 所示。

表 3 所示的是在经过微调后,8 位量化模型实现了高于浮点模型的 mAP。通过逐渐从 8 位微调到 4 位,最终的 4 位量化模型的 mAP 损耗小于 2%。2D 检测的示意图如图 7 所示。

3D 检测

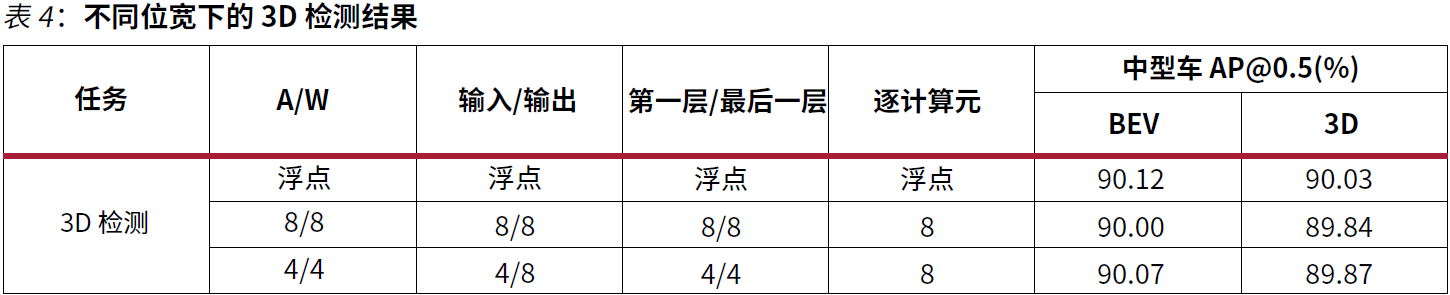

ADAS 系统的 3D 检测任务使用 KITTI 数据集[参考资料 17]。PointPillars[参考资料 18]用于开展 3D 预测任务。实验结果如表 4 所示。

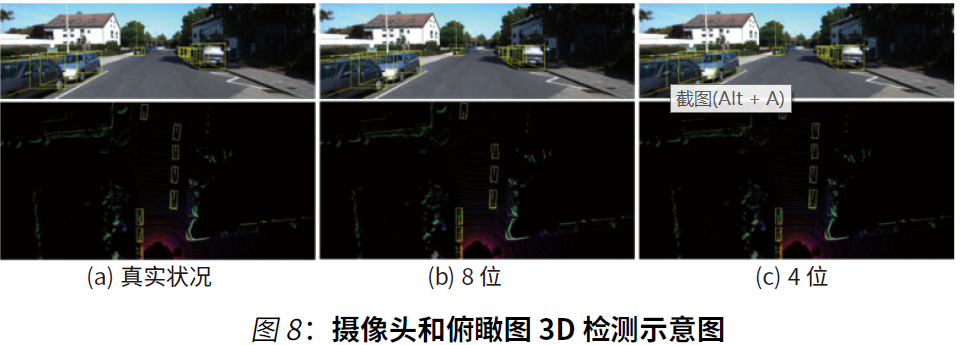

如表 4 所示,采用微调技巧后,4 位量化模型的精度仅比浮点模型低 0.16%。8 位和 4 位的 3D 检测结果如图 8 所示。

语义分割

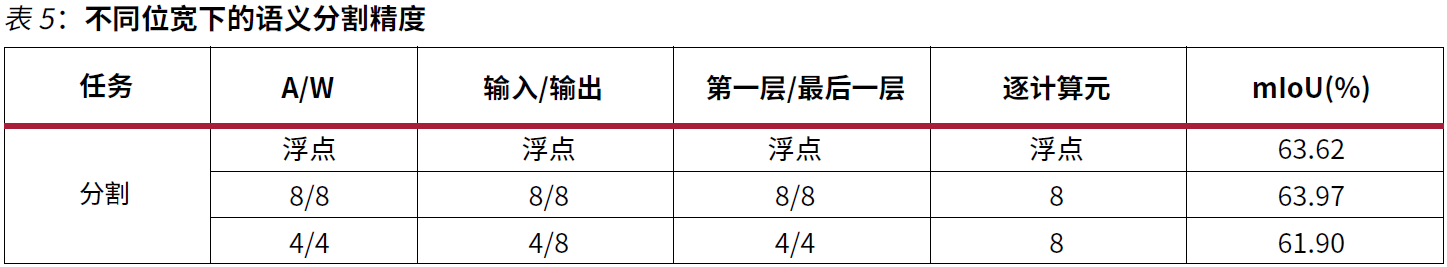

在 ADAS 系统的语义分割任务中,CityScape 的数据集[参考资料 19]以理解城市视觉场景为重点。实验在以 ResNet18 为基干的特征金字塔网络 (FPN) 上开展。结果如表 5 所示。

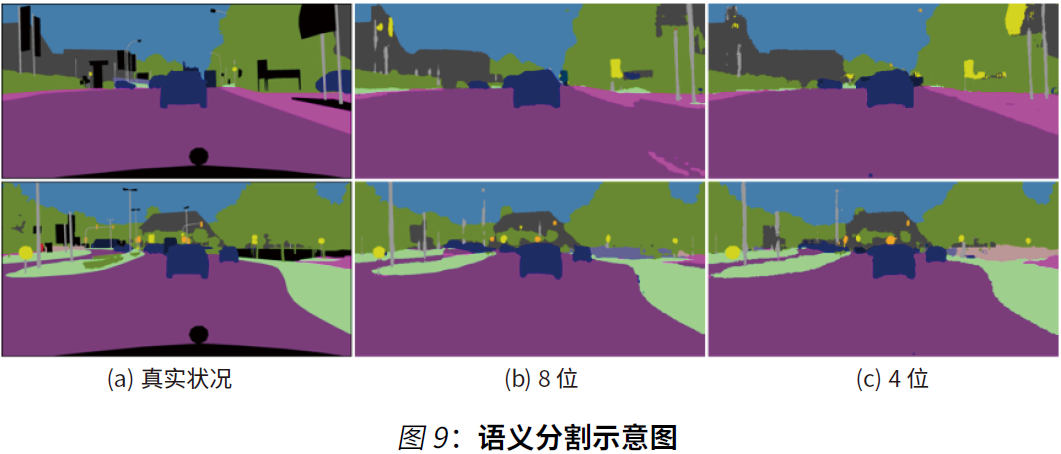

表 5 显示,8 位模型可实现比浮点模型更高的 mIoU,4 位模型的 mIoU 仅比浮点模型低 1.7%。语义分割的示意图参见图 9。

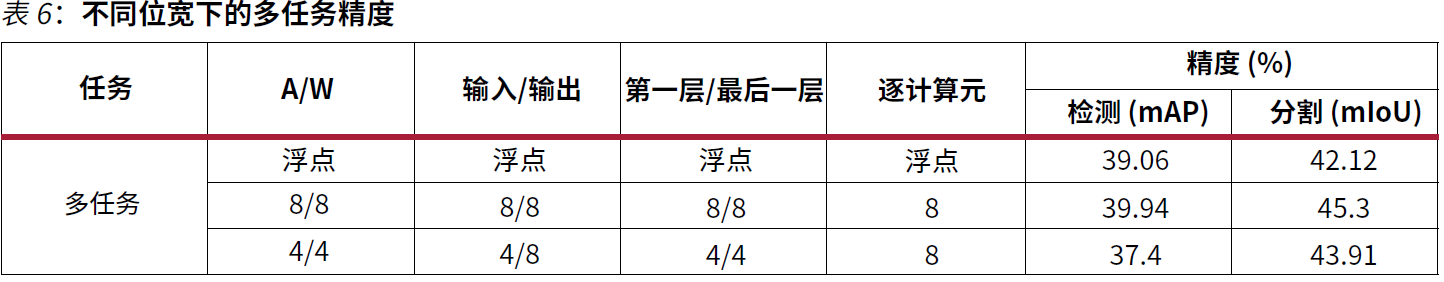

多任务学习

为增强模型的归纳功能和精度,在多任务模型中使用了多个训练数据集,包括用于检测的 Waymo 和 BDD100k,以及用于分割的 BDD100k 和 Cityscapes[参考资料 19]。这些研究在以 ResNet18 为基干的特征金字塔网络 (FPN) 上开展。结果如表 6 所示。

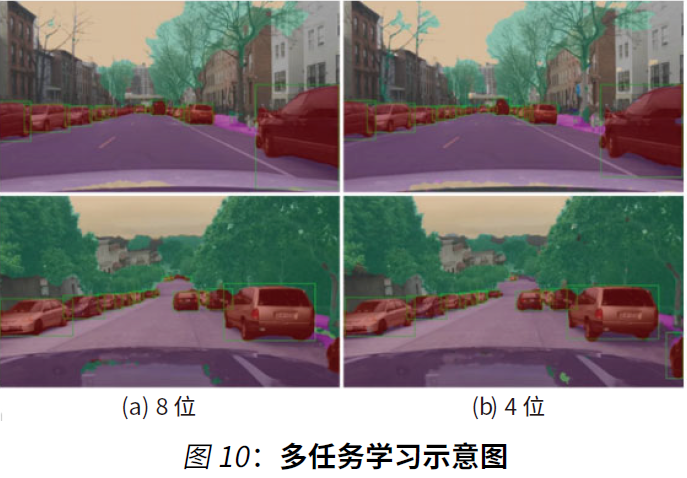

表 6显示,8 位量化模型可实现优于浮点模型的 mAP 和与浮点模型保持同等水平的 mIoU。通过逐步微调,与浮点模型相比,最终的 4 位量化模型的 mAP 降低 1.66%,mIoU 提高 1.79%,仍然劣于 8 位模型的表现。多任务示意图结果如表 10 所示。

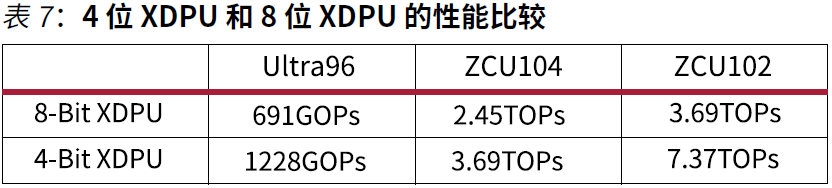

竞争分析:8 位与 4 位对比

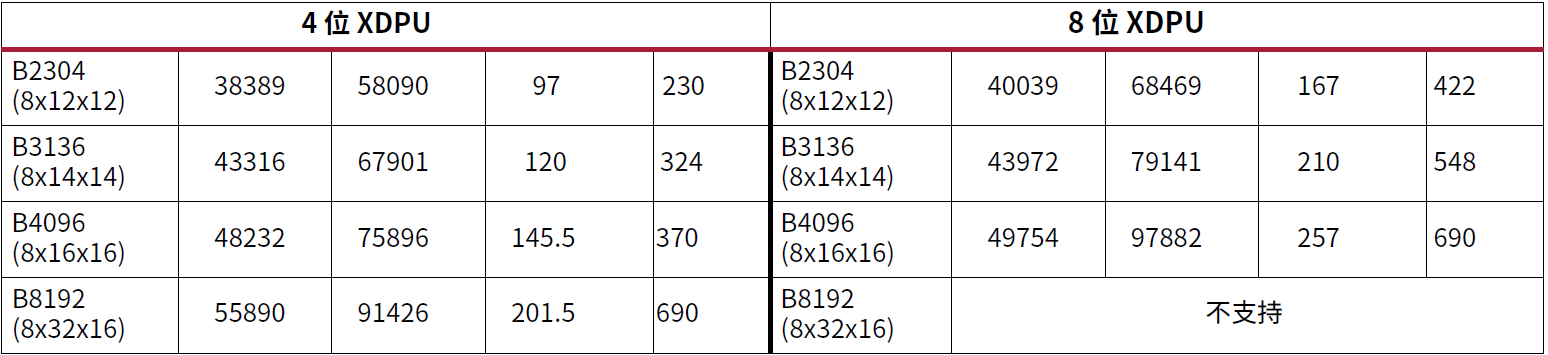

4 位 XDPU 在下列三种评估板上以 300MHz 频率运行:Ultra96 与 Zynq UltraScale+ MPSoC ZCU104 和 ZCU102。表 7 所示的是 4 位 XDPU 和 8 位 XDPU 的比较情况。在不同的 FPGA 上,4位 XDPU 实现的性能提升在 1.5 倍到 2.0 倍之间。例如,ZCU102 板使用的硬件资源没有增加,但性能提高 2 倍。

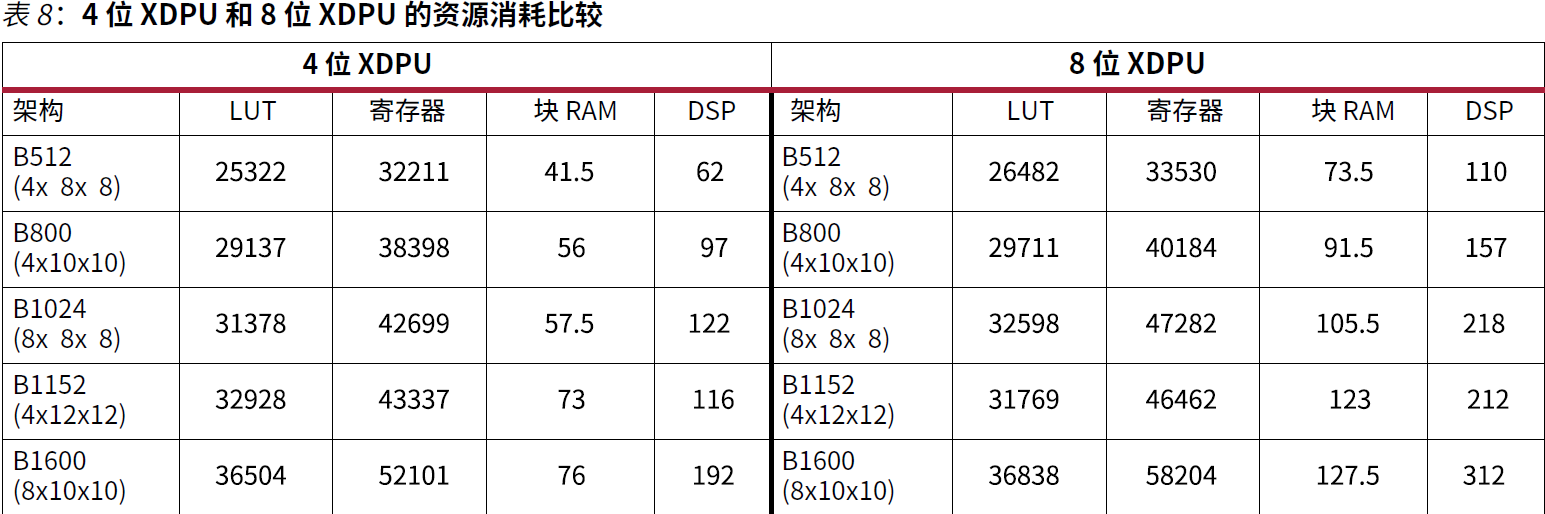

对于两个精度不同的加速器,在启用池化、逐计算元逐深度卷积和平均池化等全部功能后,对资源进行比较。如表 8 中所示,在相同的性能架构下,DSP 和 RAM 的占用显著下降。鉴于资源耗用下降,4 位 XDPU 架构被扩展到 B8192 的最大规模。使用 B8192 架构能以单器件实现更高性能。

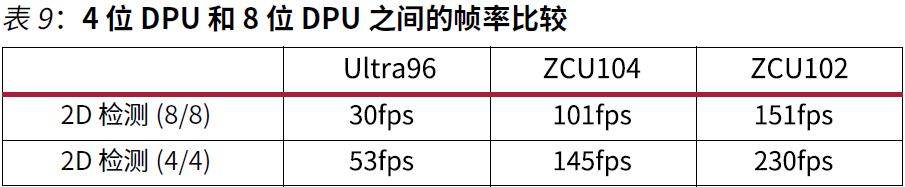

以表 3 中 13.6FLOP 的 2D 检测模型为例,两个高精度模型 4/4 和 8/8 分别使用 4 位 XDPU 和 8 位XDPU 进行测试。该网络的计算要求是 13.6GOP。2D 检测网络的帧率如表 9 所示,测试不包含预处理和后处理。鉴于效率和网络类型的差异,性能和帧率之间不存在线性关系。如表 9 所示,4 位XDPU 的帧率在所有平台上均优于 8 位 XDPU。

结论

本白皮书介绍了一种运行在 Zynq UltraScale+ MPSoC 和 Zynq-7000 SoC 系列(16nm 和 28nm)器件上的全流程、硬件友好型量化解决方案,可用作 CNN 的低精度加速器。此外,本白皮书也介绍了如何在赛灵思 DSP 片上优化 INT4,从而在一个时钟周期内完成 4 通道 INT4 相乘。卷积的计算要求可通过打包 DSP 予以满足。与 INT8 XDPU 解决方案相比,使用 DSP 实现的 INT4 优化在真实硬件上可将处理峰值 GOPS 提升最大 2 倍并将性能最高提升 1.77 倍。这种赛灵思解决方案在各种 CV任务上都获得了媲美浮点模型的结果。对于资源受限和功耗受限的用例,赛灵思继续创新软硬件协同优化方法,为深度学习应用提速。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码