赛灵思器件上的 INT4 优化卷积神经网络(1)

对于 AI 推断,在提供与浮点相媲美的精度的同时,INT8 的性能优于浮点。然而在资源有限的前提下,INT8 却不能满足性能要求,INT4 优化则是解决之道。通过 INT4 优化,与现有的 INT8 解决方案相比,赛灵思在实际硬件上可实现高达 77% 的性能提升。

概要

赛灵思在其硬件平台上提供 INT8 AI 推断加速器 — 深度学习处理器单元 (XDPU)。然而,在某些资源受限,要求高性能、低时延的场景(例如对资源、功耗敏感的边缘侧场景和低时延 ADAS 场景)中,为了实现比 INT8 更低的功耗和更高的性能,需要对神经网络进行低比特量化。然而,极低比特量化(如二进制或三进制)却会导致精度劣化。

因此,4 位激活参数和 4 位权重参数 (4A4W) 全流程硬件友好型量化解决方案可实现更优异的精度/资源权衡取舍。本白皮书介绍了在 Zynq® UltraScale+™ MPSoC 和 Zynq-7000 SoC 系列(16nm 和 28nm)上面向 CNN 4 位 XDPU 实现的低精度加速器。这种加速器通过高效地映射卷积计算,充分发挥其 DSP 功能。这种解决方案可提供优于 XDPU 两倍的解决方案级性能。在 ADAS 系统中执行 2D 检测任务时,这种实现方案能够在 Zynq UltraScale+ MPSoC ZCU102 板上实现 230fps 的推断速度,与 8 位 XDPU 相比性能提高 1.52 倍。此外,在用于 ADAS 系统中的不同任务时,该解决方案可实现媲美全精度模型的结果。

介绍

企业日益重视基于 AI 的系统在数据中心、汽车、工业和医疗等领域中的产品化。这带来了两大挑战:

• AI 推断需要完成的计算量成数量级增加,同时还要保持价格、功耗、时延和尺寸大小不变。

• AI 科学家继续日复一日地在算法和模型上开展创新,需要各种不同的硬件架构提供最佳性能。

对持续创新的强烈需求则需要使用灵活应变的领域专用架构 (DSA)。优化 AI 推断性能和降低功耗的主要趋势之一是使用较低精度和混合精度。为降低硬件设计复杂性,模型量化被当作关键技术应用于各类硬件平台。大量工作被投入用于最大限度地降低 CNN 运算量和存储成本。这项研究充分地证明,对于大多数计算机视觉任务,在不严重牺牲精度的情况下,权重参数和激活参数可以用 INT8 表达。然而对于某些边缘应用而言,硬件资源仍然不足。在对边缘应用使用较低的位宽(如 1 位、2 位)时,一些常见的硬件设计解决方案使用简化的乘法器。尽管这些解决方案时延低、吞吐量大,但它们与全精度模型相比,仍然存在较大的精度差距。因此,在模型精度和硬件性能之间寻求平衡变得至关重要。

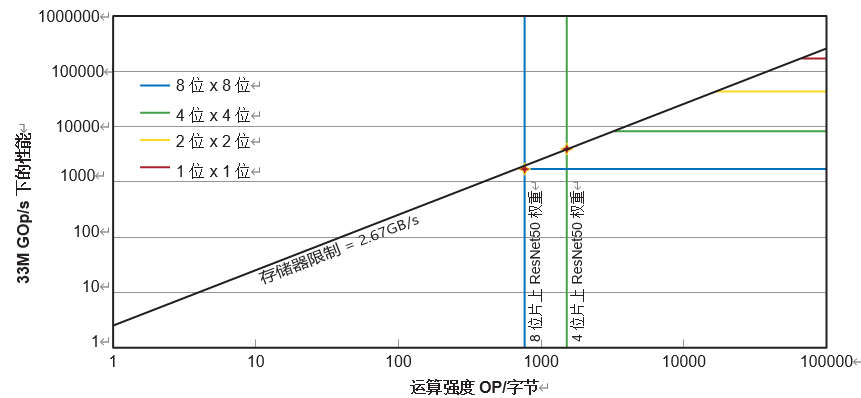

赛灵思运用几种常见的网络结构((ResNet50V1[参考资料 2]、ResNet50V2[参考资料 3] 、MobilenetV1[参考资料 4]和MobilenetV2[参考资料 5]),在 ImageNet 分类[参考资料 1]任务上通过使用几种不同的量化算法进行了实验。结果显示精度随着位宽减少而下降。尤其是在位宽低于 4 时精度下降显著。此外,赛灵思也使用 Williams 等介绍的 Roofline 模型[参考资料 6],分析不同位宽下的硬件性能,如图 1 所示。以赛灵思 ZCU102 评估板为例,随着 MAC 的精度降低,硬件成本降低,性能得到提高。此外,实验结果还显示,低比特量化可通过降低存储器需求提高性能。这在 ResNet-50 神经网络的卷积运算强度上得到证实。该网络分别用 8 位精度和 4 位精度进行了运算。因此,INT4 在模型精度和硬件性能之间实现了最佳权衡。

图 1:在 ZCU102 上以不同位宽运行 Roofline 模型

如何量化全流程硬件友好型 CNN

为实现整个量化过程的硬件友好化,INT4 量化法可分为三个部分:量化机制、硬件友好型量化设计、量化感知训练。

量化机制

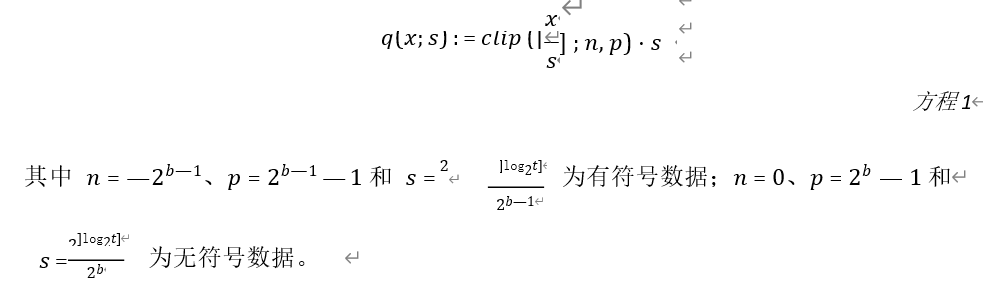

赛灵思使用经训练的量化阈值 (TQT) [参考资料 7]将 DNN 从单精度浮点 (FP32) 转换为 INT4。对于权重和激活参数,量化函数可正式地写作:

方程 1 体现出输入值 x 的量化值取决于阈值 t、位宽 b 和量化比例系数s。阈值 t 一般初始化为

待量化的张量的绝对值的最大值。随后在训练过程中用 log2t 的形式进行优化。量化系数s是 2 的幂,具有硬件友好性。上下截断运算去除部分离群数据,加大权重参数和激活参数的分布紧密度,更有利于量化。

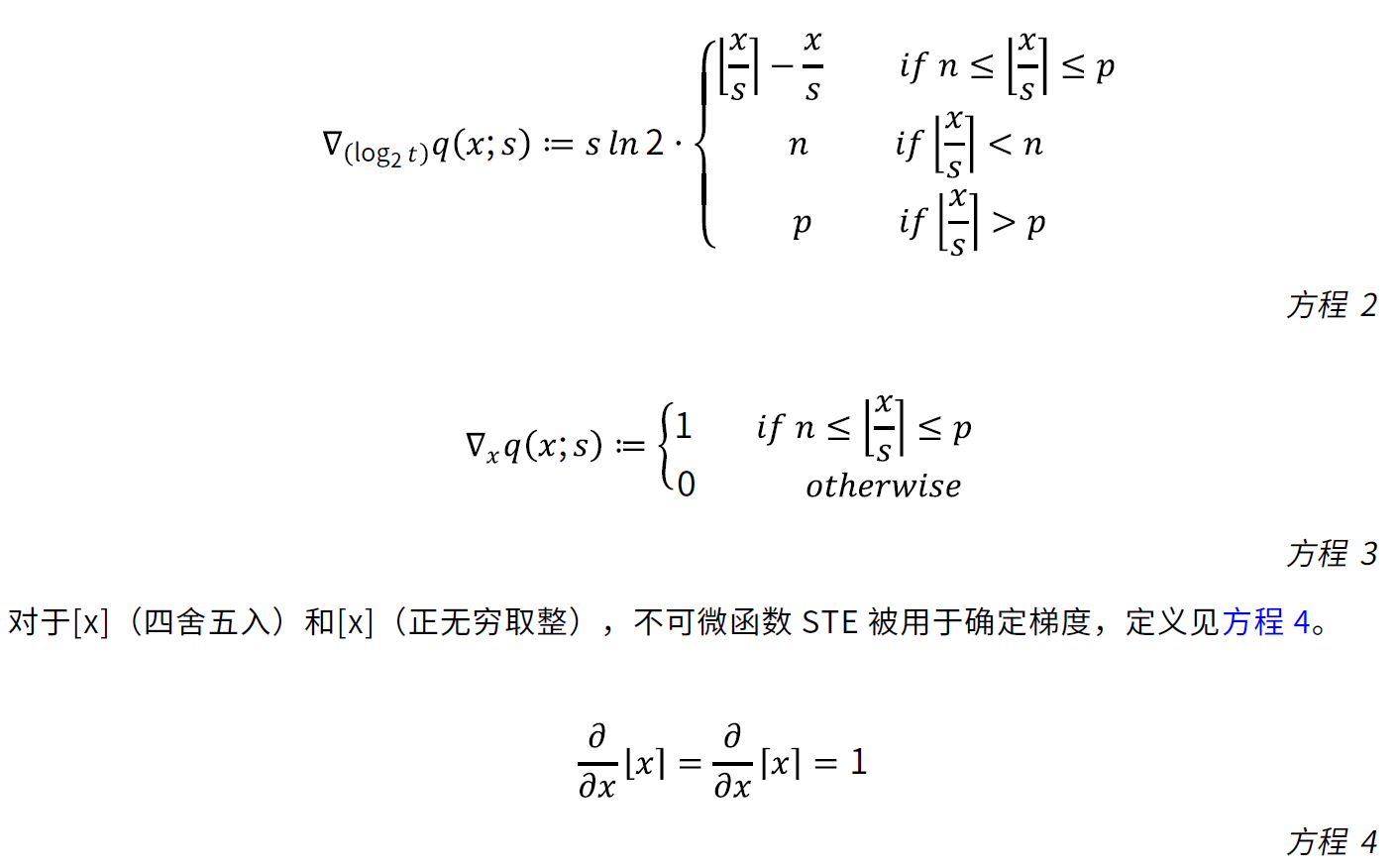

如上文所述,log2t 是一种在训练过程中可学习的参数。优化它就能确定合适的量化范围。与之相反,log2t 的梯度可通过链式法则确定。此外,输入值 x 的梯度也可通过下式计算:

TQT 证明对数表达能确保阈值和输入值的标度不变性。采用对数方式训练阈值更容易管理,并且被证明是非常高效的。

硬件友好型量化设计

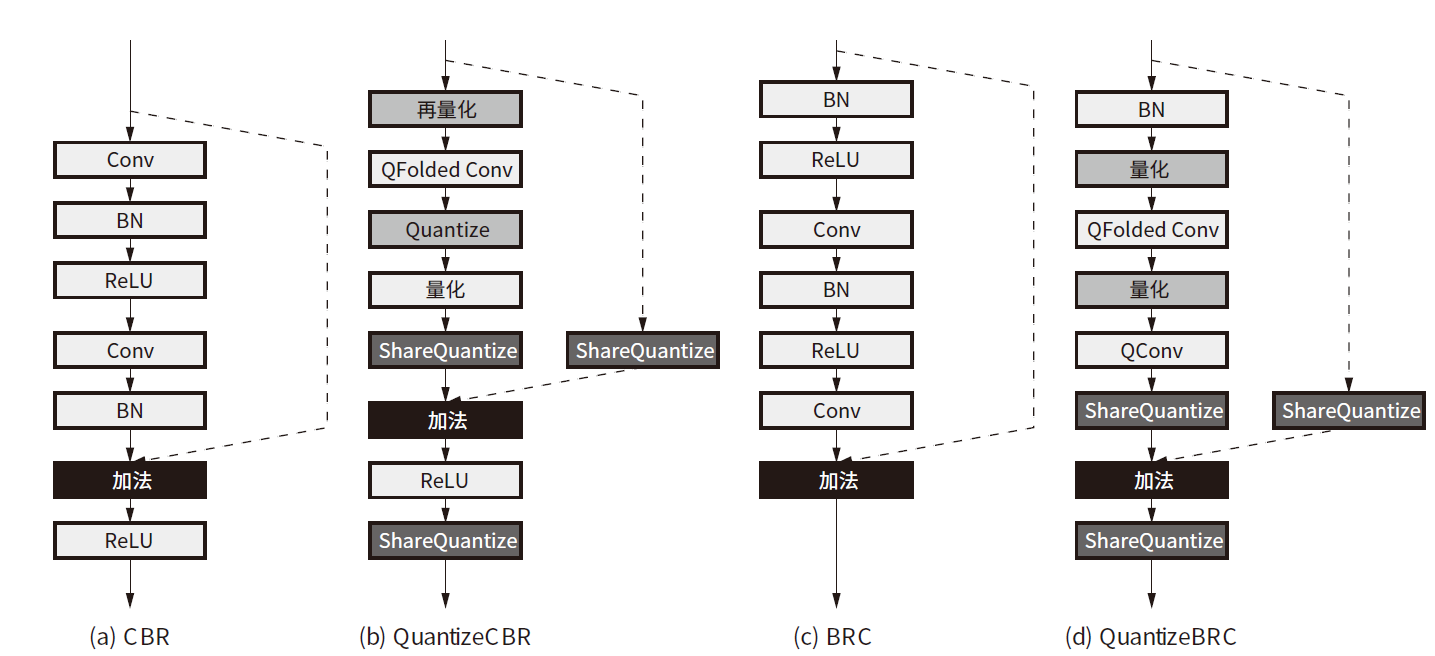

要进行量化训练,必须从全精度网络中构建低比特网络。以全流程硬件友好型量化为基础,下文介绍部分常用网络结构并对几种粗粒度模块的量化解决方案进行总结。对于这些量化模块,INT4 量化方法可用于多种类型的网络结构。部分常用模块的量化解决方案如图 2 所示。图 2中的虚线表明能根据实际网络结构增添或者删除。

模块 1:CBR(Conv+BN+ReLU)

作为 CNN 中的通用结构,BN 层被合并以减少训练和推断过程中的触发器数。然而,BN 层存在不一致性;批量运算在训练过程中使用当前批次的平均值和方差,但在推断过程中移动平均值和方差。如果量化的是从当前批次的平均值和方差获得的合并参数,在推断时就会导致偏差。为消除这种不匹配,应使用下列最佳实践[参考资料 8]、[参考资料 9]来量化这种结构。在将 BN 折叠到 ConV 后,就对折叠到 INT4 的参数进行量化。该模块的量化如图 2 (b) 所示。

模块 2:BRC(BN+ReLU+Conv)

如图 2 (c) 所示,在紧随卷积层的 BN 层被合并后,仍然存在独立的 BN 层。然而,在现有的 INT4 量化方法中,BN 层基本不受重视。为有效地部署这个独立的 BN 层,一种量化神经网络[参考资料 10]的简化方法被用于在训练过程中保持全精度,并在推断过程中吸收浮点标度和阈值偏差。这种方法可延伸用于所有线性运算(包括推断中的卷积),同时有助于保持精度。该模块的量化详见图 2 (d)。

模块 3:加法

对于加法模块,共享的量化层被用于量化所有输入和输出。根据经验,加法运算对精度敏感,但

占用硬件资源较少。因此该层一般量化为 8 位。此外,为了量化所有输入和输出,还将使用标度共享规则。共享规则的作用是让硬件绕过标度计算,消除了浮点乘法的需要。如图 2 (b) 所示,“ShareQuantize”指这些量化层共享相同标度。

其他:

为确保卷积运算的输入是 4 位,加法运算的 8 位输出需要再次被量化为 4 位,如图 2 中的“再量化”所示。对于第一层和最后一层,仍然进行 INT4 量化。整个网络的输出被量化成 8 位。内积层

与卷积层保持一致。

量化感知训练

量化感知训练通常被用作一项关键技术,用来降低低比特模型与全精度模型之间的精度差。在本白皮书描述的 INT4 量化方法中,它仍起着不可或缺的作用。量化感知训练过程都使用算法 1(如下所示)。

算法 1:逐层量化感知训练输入:

全精度输入、权重和偏差:X、W、Bias

针对输入和权重的可学习对数域阈值:ax、aw、abias

位宽:针对输入和权重,b=4;针对偏差,b=8

输出:

输出:Y

1. 初始化 ax = log2 max (|x|),aw = log2 max (|w|),abias = log2 max (|bias|)

2. 根据方程 1 计算 q(x)、q(w)和 q(bias)

3. Y = Forward(q(x), q(w), q(bias))

4. 计算分类损耗:Loss。对所有可学习参数使用正则化方法。

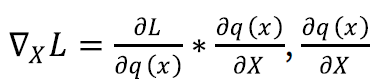

5. 参阅方程 3

6. 使用 Adam 更新全精度参数

(未完待续)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码