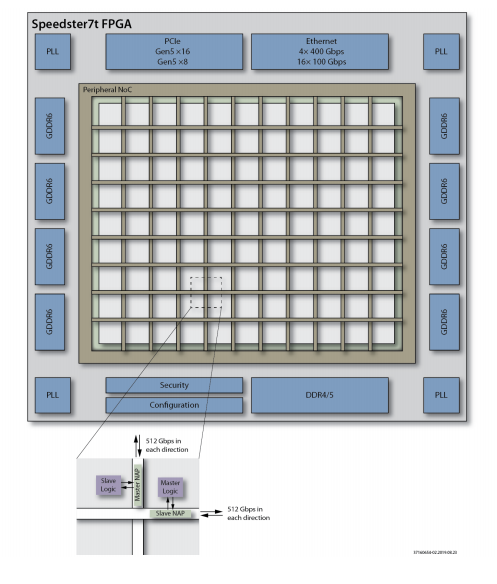

使用带有片上高速网络的FPGA的八大好处

轻松支持硬件虚拟化

Speedster7t NoC通过利用NAP及其AXI接口,为设计人员提供了在单个FPGA中创建虚拟化安全硬件的独特能力。将可编程逻辑设计直接连接到NoC只需要在逻辑设计中实例化一个NAP及其AXI4接口即可。每个NAP还具有一个相关的地址转换表(ATT),该表将NAP上的逻辑地址转换为NoC上的物理地址。NAP的ATT允许可编程逻辑模块使用本地地址,同时将NoC定向事务映射到NoC全局存储映射所分配的地址。此项重新映射功能可以以多种方式使用。例如,它可以用于允许加速引擎的所有相同副本使用基于零的虚拟寻址,同时将数据流量从每个加速引擎发送到不同的物理存储位置。

每个ATT条目还包含一个访问保护位,以防止该节点访问被禁止的地址范围。该功能提供了一种重要的进程间安全机制,可防止同时在一个Speedster7t FPGA上运行的多个应用或多个任务干扰分配给其他应用或任务的存储模块。这种安全机制还有助于防止由于意外、偶然甚至是故意的存储地址冲突而导致系统崩溃。此外,设计人员可以使用此方案阻止逻辑功能访问整个存储设备。

Memory Space:存储空间

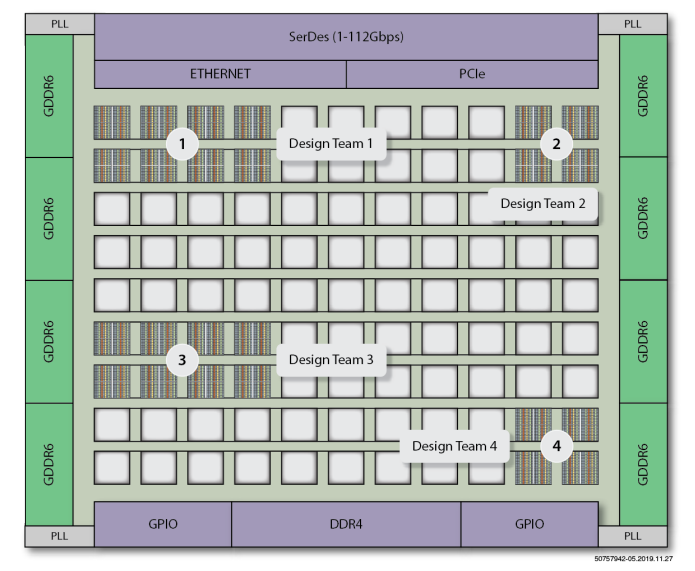

图5:致力于开发同一个FPGA的多个设计团队

简化团队协同设计

基于团队的协同化FPGA设计并不是一个新的概念,但是底层架构和布线依赖于FPGA的其他部分,从而使得实现这个简单概念非常具有挑战性。一旦一个团队完成了设计的一部分,另一个设计其他部分的团队在尝试访问设备另一端的资源时,通常会遇到挑战,因为需要在已经完成的设计部分进行布线。同样,对一部分已进行设计布线的FPGA的区域或大小进行更改,可能会对所有其他FPGA设计模块产生连锁影响。

使用Speedster7t NoC,可以将设计模块映射到FPGA的任何部分,并且可以对资源分配进行更改,而不会影响其他FPGA模块的时序、布局或布线。由于器件中所有的NAP都支持每个设计模块无限制地访问NoC进行通信,因此使得基于团队的设计成为可能。因此,如果一个设计的某个部分在规模上有所增大,只要有足够的FPGA资源可用,数据流就会由NoC自动管理,从而使设计人员不必担心是否满足时序,以及对其他团队成员正在进行的设计的其他部分可能带来的后续影响。

Design Team:设计团队

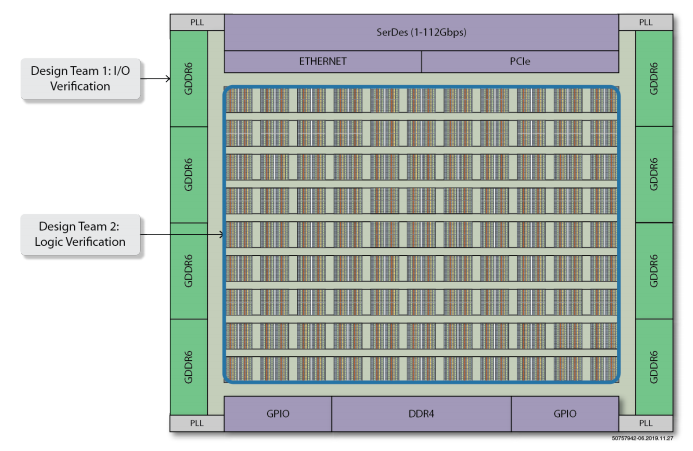

图6:独立的I/O和逻辑验证

通过独立的接口和逻辑验证加快设计速度

Speedster7t NoC的另一个独特功能是支持设计人员独立于用户逻辑去配置和验证I/O连接。例如,一个设计团队可以验证PCIe至GDDR6的接口,而另一个设计团队可以独立地验证内部逻辑功能。这种独立操作之所以能够实现,是因为NoC的外围部分连接了PCIe、GDDR6、DDR4和FCU,而不会消耗任何FPGA资源。这些连接可以在不使用任何HDL代码的情况下进行测试,从而可以同时独立地验证接口和逻辑。该功能消除了验证步骤之间的依赖关系,并实现了比传统FPGA架构更快的总体验证速度。

Design Team 1: I/O Verification:设计团队1:I/O验证

Design Team 2: Logic Verification:设计团队2:逻辑验证

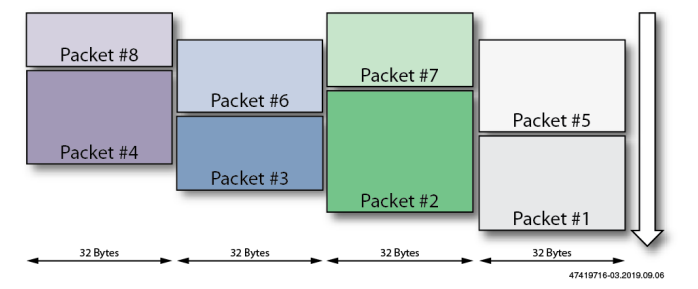

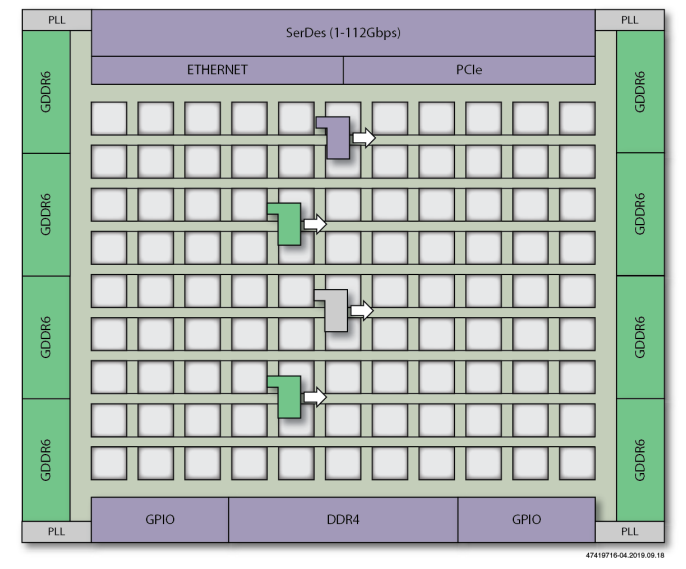

图7:分组模式下的数据总线重排

采用分组模式(Packet Mode)简化400 Gbps以太网应用

在FPGA中实现高速400 Gbps以太网数据通路所面临的挑战是找到一种能够满足FPGA性能要求的总线位宽。对于400G以太网,全带宽运行的唯一可行选择是运行在724 MHz的1,024位总线,或运行在642 MHz的2,048位总线。如此宽的总线难以布线,因为它们在FPGA架构内消耗了大量的逻辑资源,即使在最先进的FPGA中也会在这样的速率要求下产生时序收敛挑战。

但是,在Speedster7t架构中,设计人员可以使用一种称为分组模式(packet mode)的新型处理模式,其中传入的以太网流被重新排列为四个较窄的32字节数据包,或者四条独立的以506 MHz频率运行的256位总线。这种模式的优点包括:当数据包结束时减少了字节的浪费,并且可以并行传输数据,而不必等到第一个数据包完成后才开始第二个数据包的传输。Speedster7t FPGA架构的设计旨在通过将以太网MAC直接连接到特定的NoC列,然后使用用户实例化的NAP从NoC列连接到逻辑阵列中,从而启用分组模式。使用NoC列,数据可以沿着该列被发送到FPGA架构中的任何位置,以便进一步处理。使用ACE设计工具配置分组模式,可大大简化用户设计,并在处理400 Gbps以太网数据流时提高了效率。

Packet:数据包

Byte:字节

图8:使用分组模式的400 Gbps以太网

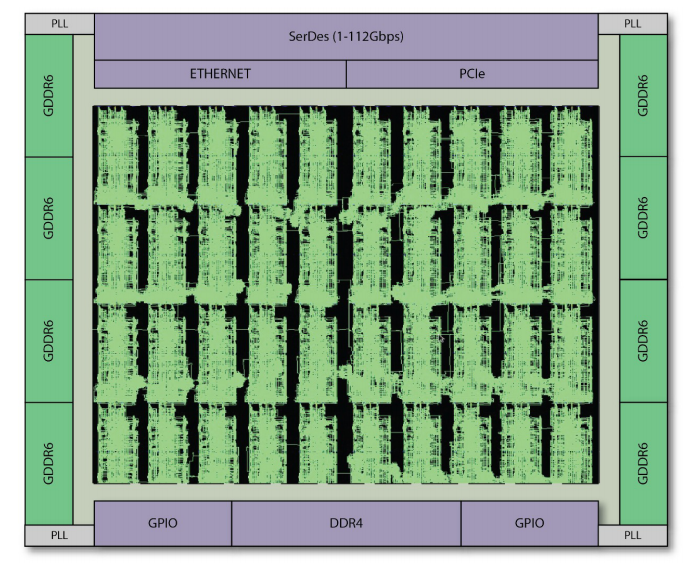

降低逻辑占用并提高整体FPGA性能

与以前的传统FPGA相比,Speedster7t NoC具有更大的灵活性和更简单的设计方法。一个潜在的好处是NoC会自动减少给定设计所需的逻辑量,设计可以使用NoC代替FPGA逻辑阵列来进行模块间布线。ACE设计工具自动管理将设计单元连接到Speedster7t NoC的复杂性,因此设计人员无需编写HDL代码即可实现生产率。这种方法简化了实现时序收敛的耗时挑战,同时又不会由于FPGA逻辑阵列内的布线拥塞而降低整体应用性能。NoC还可以在不牺牲FPGA性能的情况下提高器件利用率,并且可以显着增加可用于计算的查找表(LUT)数量。

为了强调这一优势,我们创建了一个支持二维输入图像卷积的示例设计。每个模块都使用Speedster7t机器学习处理器(MLP)和BRAM模块,每个MLP在一个周期内执行12次int8乘法。将40个二维卷积模块链接在一起,以利用器件中几乎所有可用的BRAM和MLP资源。总共有40个二维卷积示例设计实例并行运行,使用了94%的MLP、97%的BRAM、但仅使用了8%的LUT。在总的可用LUT中,其余92%的LUT仍可被用于其他功能。

随着更多的实例被内置于器件中,单个单元模块的最高频率(FMAX)不会降低。该设计能够保持性能,因为进出每个二维卷积模块的数据可以直接从连接到NoC的NAP访问GDDR6内存,而无需通过FPGA逻辑阵列进行布线。

图9:一个带有40个二维卷积模块实例的Speedster7t器件

结论

Speedster7t NoC实现了FPGA设计过程的根本转变。Achronix是第一家实现二维片上网络(2D NoC)的FPGA公司,该2D NoC可以连接所有的系统接口和FPGA逻辑阵列。这种新型架构使Achronix公司的FPGA特别适用于高带宽应用,同时显著提高了设计人员的生产率。由于NoC管理了FPGA中设计的数据加速器和高速数据接口之间的所有网络功能,因此设计人员只需要设计其数据加速器并将其连接到NAP原语即可。ACE和NoC负责其他所有事务。通过使用NoC,FPGA设计人员将受益于:

● 在整个FPGA逻辑阵列中简化高速数据分发

● 自动将PCIe接口连接到存储器

● 在独立的FPGA逻辑阵列模块上实现安全的局部重新配置

● 轻松支持硬件虚拟化

● 简化团队化设计

● 通过独立的接口和逻辑验证加快设计速度

● 采用分组模式简化400 Gbps以太网应用

● 降低逻辑占用并提高整体FPGA性能

Achronix半导体公司

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码