基于SDR的FM调制与解调器的实现

张博,李少阳, 刘宇

(西安邮电大学电子工程学院,陕西省 西安市 710121)

摘要:提出了一种基于SDR的FM调制解调器的实现方案,此方案采用ZYNQ平台和AD9361射频收发芯片搭建。首先介绍ZYNQ+AD9361的SDR硬件平台的设计,其次对FM调制解调的原理分析并结合MATLAB进行算法仿真,最终在ZYNQ平台上完成SDR工程设计。

关键词:FM;AD9361;软件无线电;CORDIC;调制解调

基金项目:西安市集成电路重大专项(201809174CY3JC16);陕西省教育厅服务地方产业化专项(15JF029)

0 引言

FM(Frequcncy Modulation) 调制是目前国内外采用的较为普遍的一种调制方式。主要应用于高保真音乐广播,对讲机,卫星通信等领域,传统的方法使用模拟器件搭建的方式,应用最广泛的为收音机。此方式电路结构复杂,灵活性差,抗干扰能力弱;后来逐渐出现DSP或者FPGA与A/D结合的结构,此方案中对ADC和DAC的要求比较高 [1-2] 。射频链路比较复杂,不可灵活配置。对于战场上单兵作战通信,飞机通信,人们对SDR要求越来越高,本文提出了在ZYNQ+AD9361的架构上实现的FM调制与解调方案。本方案电路结构简单,功耗低,接收和发射频点灵活可调,高动态范围等优点,FM解调也相对于传统的锁相环相干解调具有结构简单,抗载频失配,同时满足解调宽带和窄带的信号 [3] 。

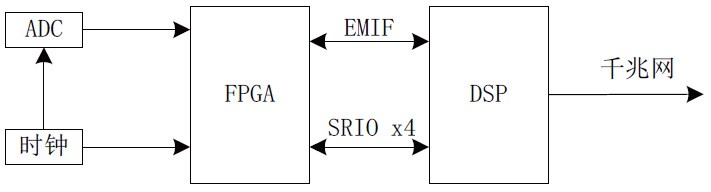

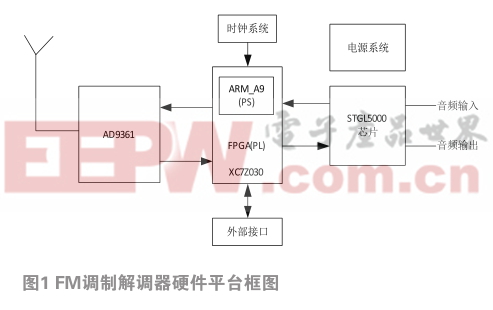

1 硬件平台

基于SDR的FM调制解调器的硬件平台框图如图1所示,AD9361作为射频收发的核心芯片,接收时将射频数据与本振混频后转换为基带数据,通过内部ADC将模拟信号转换为数字信号,FPGA作为算法处理、系统控制的核心芯片,内部含有ARM-A9双核,主要用于对AD9361内部寄存器的配置,以及系统参数的控制,FM调制解调算法在FPGA中的PL部分实现,该ZYNQ+AD9361平台能够适应各种数字通信,语音通信,本文论述主要应用军用飞机语音通信。

1.1 主要芯片选型

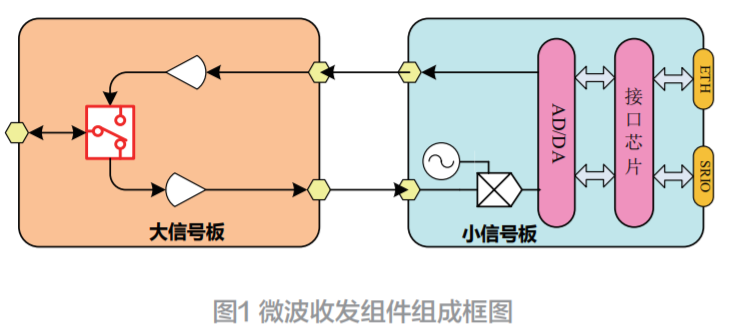

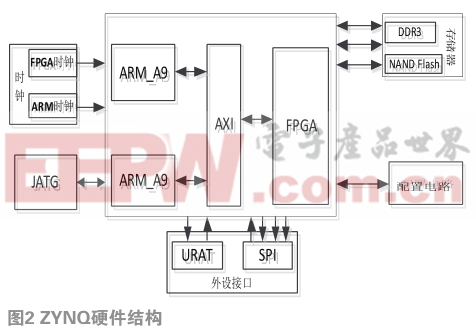

Xilinx 公司推出了新一代28 nm工艺,集成 FPGA 与双 ARM 核,小封装、低功耗全可编程片上系统(AllProgrammable SoC)Zynq-7000 系列。如图2所示ZYNQ硬件结构,在芯片内部FPGA通过AXI总线完成与ARM的数据交互。完美的将FPGA的优势与ARM的优势结合起来 [4] 。

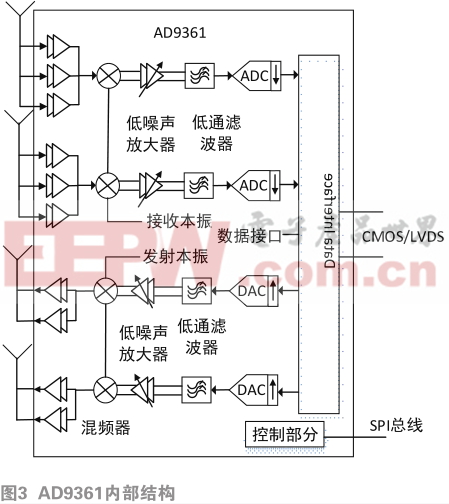

采用ADI公司的AD9361射频捷变收发器,作为射频收发器,AD9361支持的频率范围在70 MMHz~6.0 GHz,涵盖了大部分特许执照和免执照频段,支持200 kHz~56MHz的通道带宽,AD9361集成了SDR收发器所必须的RF、数模转换、混合信号 [5] 。AD9361芯片内部结构如图3所示。AD9361内部具有两个接收和发射通路:每个接收通路各自含有一个低噪声放大器(LNA),相内(I)和(Q)正交放大器、混频器、12位ADC和三级半带滤波器以及阶数可调的FIR滤波器,三级半带可通过修改抽取系数来达到降低速率。其中FIR滤波器可以使用MATLAB中的FDATOOL滤波器工具产生滤波器系数,通过软件编程写入AD9361中,应用于更多的通信带宽中。

发射通路与接收通路基本相同,基带数据被AD9361接收到,直接进入FIR滤波器,在经过三级半带滤波器插速之后,被DAC采样,其中DAC的采样速率可调,通过三级半带滤波器的插速处理来满足DAC的采样速率。最后信号分为I、Q两路进入射频模块部分与载波混频,在经过放大器通过天线发送。

2 FM调制解调软件算法设计

2.1 FM调制算法

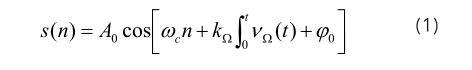

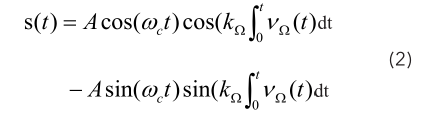

调频(FM)是载波的瞬时频率随调制信号成线性变化的一种调制方式,音频调频信号的数学表达可以写为:

其中,A0 为调频信号的幅度;Wc 为载波角频率;νΩ(t)为音频调制信号;kΩ为调制角频偏;ϕ0 为调制信号的初始相位。把式(1)展开得:

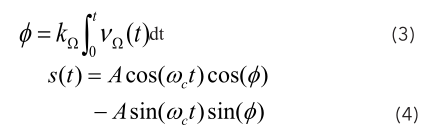

令 φ 等于式(3)并代入式(2)得式(4)

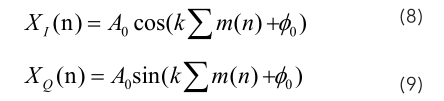

从式(3)看到,在实现FM时要对调制信号进行积分,然后对这积分后的信号分别取正弦和余弦即可。因此用正交调制法实现时只须令:

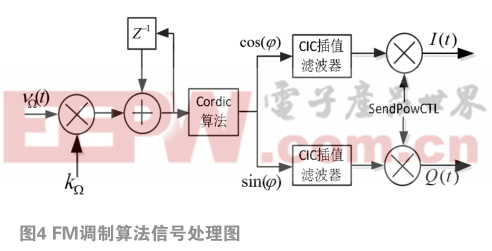

因此,调制算法信号处理如图4所示,语音信号通过STGL5000芯片的ADC以96 kHz的速度进行采样得到采样的信号νΩ(t),将到信号乘以调制角频偏kΩ 并进行累加求和,然后进行Cordic运算分别进行sin和cos运算得到正交调制,再经过5级级联的CIC滤波器内插20倍,经过内插后的得到1.92 MHz的信号在分别乘以发射功率,就可以得到 I(t) 和Q(t) 的零中频的调制信号,AD9361以1.92 MHz的速度采集I(t) 和Q(t) 的零中频的调制信号,经过FIR滤波器、多级半带滤波器最终DAC以30.72 MHz的速度转化为模拟信号,在与载波信号混频后通过天线发送 [6] 。

2.2 FM解调算法

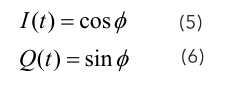

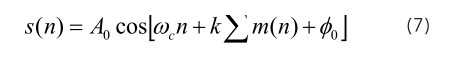

调制信号表达式:

对信号进行正交分解得:

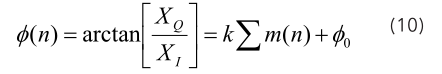

对正交与同相分量比值反正切运算:

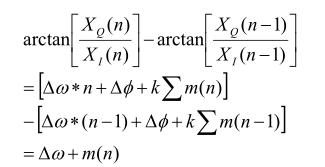

然后,对相位差分,即可求得调制信号:

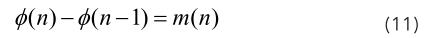

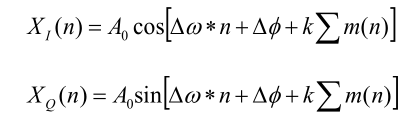

FM信号用正交解调方法进行解调时,也具有较强的抗载频失配(指失配差频和差相是常量,非随机变量)能力,本地载波与信号的载波存在频差和相差时,同相分量和正交分量可表示为:

同样,对正交与同相分量之比值反正切及差分运算,就可得到调制信号:

当载波失配差频和差相是常量时,解调输出只不过增加了一个直流分量Δw 就可得到调制信号m(n)[7-8] 。

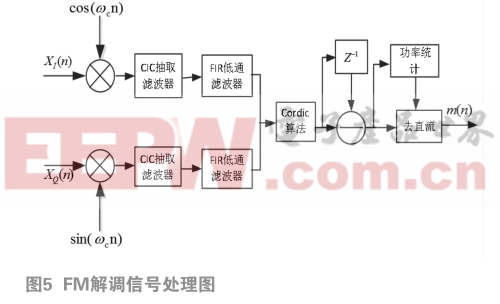

因此,调制算法信号处理如下图5所示,AD9361通过天线接收到射频信号后,经过混频、ADC、多级半带滤波器,FIR滤波器,最终FPGA以1.92MHz的速度采集到XI(t) 和XQ(t)两路中频信号,经过下变频、CIC抽取滤波器、FIR低通滤波器变为零中频信号,在进过cordic算法的极坐标转换得到瞬时相位,然后用前一时刻的瞬时相位减去后一时刻的瞬时相位,就可以得到相位差,即得到解调的有用信息 [9] 。但是由于本地载波和信号载波的频差和相差,因此在将解调到的信号进行平均得到信号的功率,并在解调的信号中减去平均功率,就可以得到调制信号 [10] 。

3 性能仿真与实现

3.1 Matlab仿真

在Matlab环境下对提出的FM调制解调算法进行了仿真,主要仿真参数如下:

(1)调制信号幅度为5的1 KHz正弦波;

(2)载波信号幅度为1的64 KHz正弦波;

(3)采样率为1 MHz;

(4)FM的最大频偏为6 KHz;

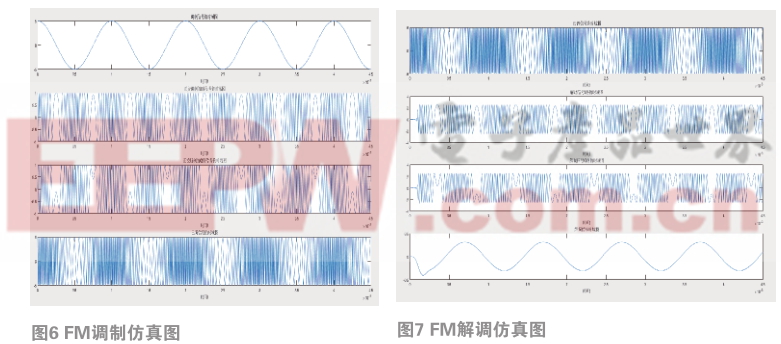

(5)仿真数据长度为4500;FM调制结果仿真波形如图6所示,由1 KHz的单音调制信号,经过正交调制产生I、Q两路调制信号,最终由I、Q两路正交信号得到最终的调制信号。

FM解调结果仿真波形如图7所示,由调制信号经过64 KHz下变频,在经过滤波器到零中频的I、Q两路基带信号,在最终解调出原始信号 [10] 。

3.2 设计实现

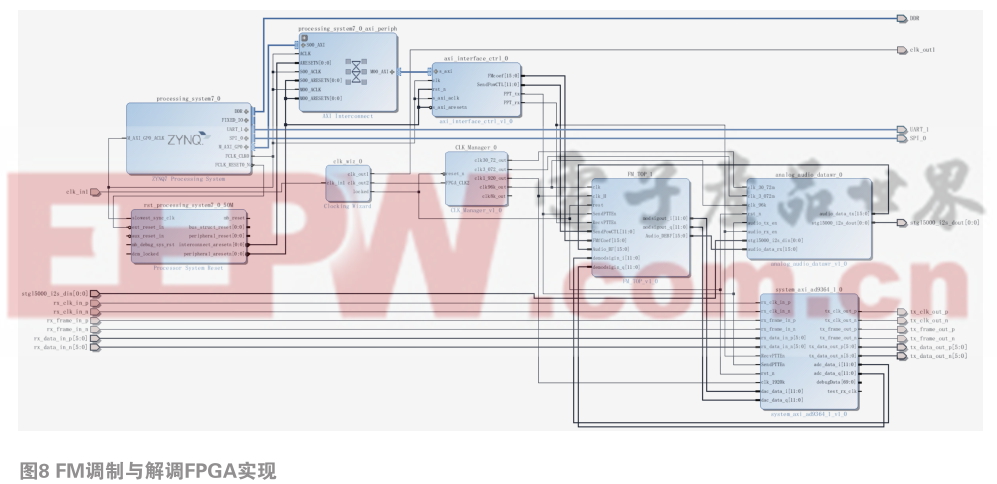

在vivado中最终建立如图8所示的工程,在工程中调用了ARM硬核(processing system7_0)通过SPI对AD9361的配置,用户可以通过ARM核上的串口对AD9361的频点改变,以及配合自定义IP (axi_interface_ctrl_0)通过AXI总线实时对FM调制系数、FM发射功率、以及收发切换设置,使得该系统适应更多场景使用,自定义IP(FM_TOP_0) 实现对信号的调制与解调;自定义语音收发IP(analog_aduio_datawr_0)实现对STGL5000芯片的数据的收发。自定义AD9361数据收发IP(system_axi_ad9364_1_0)实现对AD9361的数据收发。

天线接收到信号后经过AD9361一次下变频后,通过内部12位ADC转化为数字信号,由FPGA内部的AD9361 IP接收到分成I、Q两路传送到FM调制解调模块,解调出射频信号中的音频信号,然后通过语音收发IP将语音信号发送到STGL5000芯片经过DAC转化后驱动耳机发声,该过程实现了SDR接收过程。

STGL5000芯片将麦克风的语音信号经过内部的ADC转化为音频数字信号,有FPGA内部的语音收发IP接收到,传送到FM调制解调IP中进行调制,将调制后的信号分为I、Q两路信号,通过AD9361数据收发IP将数据发送到AD9361芯片和本振混频后通过天线辐射到空间中,如果用户需要更大的功率可以外接功放。该过程实现了SDR的发射过程 [11] 。

3.3 设计验证

将如图8所示的工程综合,布局布线,生成比特流,导入到Xilinx SDK软件中建立C工程 [12] ,最终编译下载到SDR收发机的FPGA中,使用RS公司生产的SMA180电台综合测试仪。完成接收机和发射机的测试。

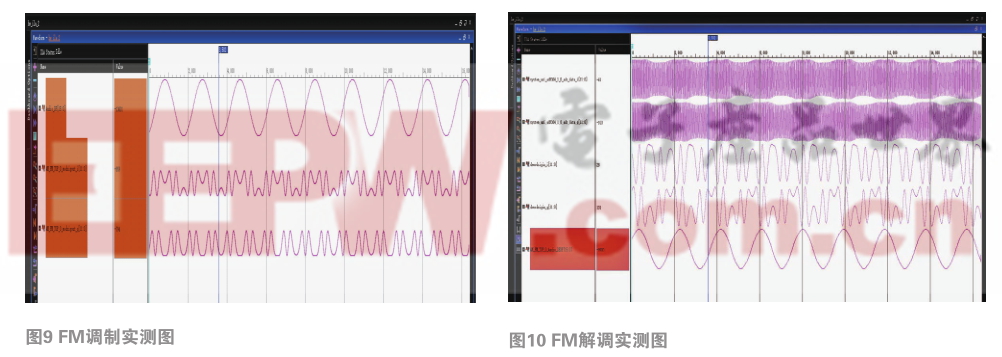

测试FM调制时,由RS综测仪输出1KHz的正弦波作为调制信号,将AD9361的载波信号设置为108MHz,同时使用vivado软件下的ILA调试方法,在线测试捕获到某一时刻的调制信号以及调制后零中频的I、Q两路信号,如图9所示。

测试FM解调时,由RS综合测试仪,输出载波幅度108 MHz,功率为-53 dBm,调制信号为1 KHz的正弦波,最大频偏为6KHz的射频信号,发送到接收机中,同时使用vivado软件下的ILA调试方法,在线测试捕获到某一时刻的低中频调制信号I、Q两路,经过下变频后变为零中频I、Q两路信号,再通过解调算法解调出原始信号,如图10所示。

4 结论

本文实现了基于ZYNQ+AD9361平台的FM调制解调器,此系统具有发射频点、接收频点以及FM发射调制角频偏可灵活配置,收发切换时间小于10ms。采用ZYNQ系列的XC7Z020CLG484-1芯片,搭建工程,综合后LUT资源占用616,触发器资源占用107。此平台适用于各种ZYNQ平台具有很好的移植性,能够应用于各种无线通信设计。

参考文献:

[1]杨明极,马琳.基于软件无线电的FM解调算法[J].电子设计工程,2012,20(16):116-125.

[2]曹沅.基于FPGA的FM调制解调器的实现[J].舰船电子工程,2013,3 (9):68-70.

[3]刘立,向新,孙眸,王锋.FM信号数字化解调算法的改进与实现[J].光通信研究,2012,4:26-28.

[4]Zynq-7000 All Programmable SoC(XC7Z010 and XC7Z020):DC and AC SwitchingCharacteristics [EB/OL].(2012-11).

[5]AD9361 RF and BB PLL Synthesizer User Guide[EB/OL][2014-11-06](2015-09-01).http://www.analog.com/media/en/technical-documentation/user-guides/AD9361_Reference_Manual_UG 570.pdf.

[6]余莲.AD9361:基于突破性技术促进软件定义无线电应用田电子技术应用[J],2013,39(11):1.

[7]杨小牛,楼才义,徐建良.软件无线电原理与应用.北京:电子工业出版社,2001.

[8]Jeffrey H. Reed.软件无线电—无线电工程的现代方法[M].陈强译.北京人民邮电出版社,2004:366-372.

[9]张欣.扩频通信数字基带信号处理算法及其VLS工实现[M]. 北京:科学出版社,2004:57-63.

[10]姚东,王爱民,冯峰.MTALAB命令大全[M].北京:人民邮电出版社,2000,6.

[11]宋飞.基于FPGA的数字中频处理技术研究田」西安:西安电子科技大学,200.

[12]陆佳华,潘祖龙,鹏竞宇.嵌入式系统硬件协同设计实战指南:基于Xilinx ZYNQ [M]北京:机械工业出版社,2014.7.

作者简介:

张博(1983—),男,博士,教授,从事射频模拟集成电路研究。

李少阳(1991-),男,硕士研究生,研究方向为集成电路。

刘宇 (1973-),男,硕士,高级工程师,研究方向为集成电路。

本文来源于科技期刊必威娱乐平台 2019年第7期第31页,欢迎您写论文时引用,并注明出处

关键词: FM AD9361 软件无线电 CORDIC 调制解调 201907

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码

相关文章

-

-

-

-

-

-

-

-

2019-07-01