基于ASIC的功耗评估与优化设计

Power estimation and optimization based on ASIC design

尹远,黄嵩人

(湘潭大学物理与光电工程学院,湖南 湘潭 411105)

摘要:随着芯片设计的复杂度和规模越来越大,现如今ASIC芯片的功耗要求也越来越高。低功耗设计作为一个重要目标,需要设计者格外重视[1] 。在本文中,首先讨论了功耗的组成及来源,阐述了在设计初期的功耗评估,以及功耗优化的思路[1] 。接着描述了功耗优化的具体操作技巧,其中详细描述了时钟门控的原理、实现流程等,最后对功耗优化的效果进行分析和比较。

关键词:低功耗设计;功耗评估;功耗优化;时钟门控

0 引言

随着便携式导向的消费类电子产品的需求不断增大,便携式电子设备的低功耗需求、基于可靠性与性能影响的考虑、芯片设计及制造的成本影响等,都体现了低功耗设计的需求和必要性。因而对功耗要求也越来越高,低功耗设计已逐渐成为衡量电子产品是否成功的重要指标,使得芯片设计者也越来越重视对功耗的优化设计。近来工艺技术的快速提高,面积、速率、温度等性能要求不断提升,这些改变对芯片的功耗优化设计有着很重要的影响。尤其对于追求低功耗、微型化、高可靠性等目标的ASIC芯片来说,更是面临着不小的挑战。

本文将介绍芯片功耗的来源和构成,及其基本概念。然后介绍芯片的功耗的评估计算方法和途径,提出在ASIC芯片设计中进行功耗优化的思路,同时结合EDA工具辅助实现,介绍对芯片设计初期阶段的核心功耗进行优化的具体操作流程,最后进行功耗优化后的分析。

1 功耗的构成

功耗的构成按照类型分类,主要由动态功耗和静态功耗两部分构成,通常动态功耗占芯片整体功耗的绝大部分 [2] 。

(1)动态功耗,是电路在工作时所消耗的能量。

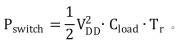

对于CMOS电路,动态功耗又分为开关功耗和短路功耗,即PDynamic =Pswitch +Pinternal[3] 。开关功耗也称为翻转

功耗(Switching Power),由电路翻转时对负载电容充放电引起,即

短路功耗也叫内部功耗(Internal Power),在输入翻转时PMOS和NMOS同时导通的瞬间电流形成,即Pinternal =VDD ·Tr·Qx[4]。

(2)静态功耗,是在电路没有翻转只供电的情形下,晶体管中漏电流造成的功耗,所以也叫漏电功耗(Leakage Power),公式为Pleakage=VDD·Ileakage。静态功耗的来源有几种方式,很大比例是由源极和漏极之间的亚阈值漏电流造成,另外还有栅极漏电流、栅极和衬底之间的隧道漏电流等引起的漏电功耗。

上述公式中,VDD为电路供电电压,C为门电路的等效电容负载,Tr为信号的翻转率,为一次翻转过程中电源到地的电荷量,Ileakage为泄漏电流。

2 功耗的评估

功耗评估是低功耗设计中的重要内容,在芯片设计的各个阶段,都有相应的方法去评估功耗,提前帮助设计者更科学有效的做好功耗优化。

2.1 功耗评估方法

在设计前期阶段,对功耗的估算主要可以通过手动计算和工具自动评估。

(1)手动计算:通过对功耗来源的分析,根据功耗总公式P=Pswitch+Pinternal+Pleakage,再结合工艺库中有关功耗的信息,进行理论估计。根据上文中提到的公式,可以由重要的参数进行功耗的具体估算,再根据不同的条件在工艺库中查找对应的信息。工艺库中包含了标准单元的功耗信息,在使用软件或手动对RTL级代码和门级网表做功耗分析时,都需要用到。

(2)工具自动评估:在RTL级代码完成后,可以通过Spyglass等软件进行低功耗的代码风格检查,找出可进行优化的逻辑模块。一般常用Synopsys公司的工具(从属于Design Compiler),对RTL级和门级网表进行分析并优化。

由于电路级的功耗评估的延时过多,需要大量的时间和资源,所以在工业实践中很少采用。实际的功耗分析常对设计初期的RTL级和门级网表进行,通过工具自动计算出功耗的数值,因是在理想情况且忽略了包括物理设计等因素,所以获得的结果不够精确,但对低功耗设计具有重要的指导作用。物理设计完成后可通过Prime Time PX工具精确计算功耗,不过届时再降低功耗收益就小了。

2.2 功耗评估流程

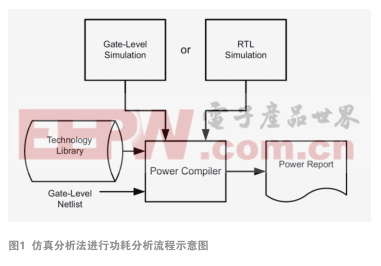

在实际大规模的集成电路项目中,通过手工计算功耗是不现实的,一般需要借助EDA工具。以Power Compiler来说,功耗的分析主要两种方法,分别是设置翻转率(无向量分析法)和仿真分析法,都需要获取每个节点的开关行为情况。

仿真分析法更方便精确,其关键是获得文件,本质是一种记录开关动态行为的内部交换格式的文件,后用软件读取进行功耗分析。SAIF文件可由VCS等仿真工具对RTL级电路仿真或者门级网表电路仿真后得到,之后便可进行功耗分析[5] 。

3 功耗的优化

3.1 功耗的优化思路

一般而言,可利用自顶向下的方法进行低功耗设计的思考,而且优化的抽象层级越高,越能获得显著的功耗降低效果。首先应从系统与架构级层面思考功耗优化,然后思考在RTL级与门级进行低功耗设计的方法。

(1)系统与架构级功耗优化:在设计初期的系统结构层级,可以通过优化算法使得如加法器、乘法器、存储等资源和操作的使用最小化,实现对硬件资源的合理配置与使用。也可以增加休眠待机模式,减少芯片不必要的工作时间。

(2)合理选择并行或者流水线技术,可以适当降低功耗。采用并行处理可以降低系统工作频率,从而可降低功耗[6]。流水线技术(Pipeline)是将组合逻辑系统地拆分,并在各级之间插入寄存器,这样每一步小操作的时间减小,可提高工作频率,又能并行执行提高处理速度,还能以较低的电压来驱动系统。

(3)逻辑优化与资源共享:RTL级代码设计时可进行逻辑优化,减少硬件资源消耗。使用良好的编码风格,利用数据编码来降低开关活动,例如用格雷码比用二进制码翻转更少,功耗更低[6]。简化状态机,降低每次工作的状态机的寄存器数量,为功耗降低提供了可能性。进行逻辑共享,提高如FIFO、查找表、RAM存储资源的利用率。

此外在RTL级与门级中,常采用的低功耗设计技术是时钟门控[7]。

3.2 时钟门控

3.2.1 时钟门控原理

动态功耗是芯片功耗主要部分,是由电路翻转引起负载电容的充放电,所以降低电路中冗余的翻转动作,关闭未工作时的电路的时钟网络使其处于静态,是一种降低功耗的重要思路。时钟门控技术通过控制时钟的翻转,降低电路的翻转率,从而达到降低动态功耗的目的,使用门控时钟技术能有效降低芯片的系统动态功耗,所以在低功耗设计中使用较多,广泛应用于大规模集成电路设计中[2]。

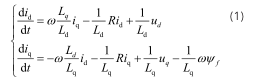

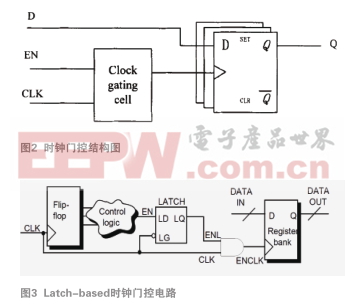

如图2所示,通过门控单元控制时钟信号的翻转,从而实现对寄存器或模块的工作时钟的开关控制,决定数据是否向下一级逻辑传播。避免了冗余信号的翻转,从而降低了电路的动态功耗[8]。

随着设计规模的增大,通过手动方式添加时钟门控逻辑效率很低,因而目前业界主流是通过EDA工具在综合阶段根据RTL级代码的特点自动插入时钟门控逻辑[2]。

3.2.2 时钟门控单元的选择

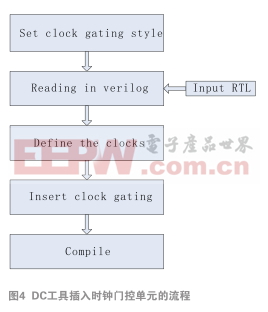

时钟门控的实现方式有多种,最常用的是free和Latch-based。Latch-free类型时钟门控一般是由结构简单的与门或者或门电路组成,但对时序要求较高。比如由与门组成的电路波形图中时钟信号CLK和使能信号EN相与,得到的门控时钟GCLK出现了毛刺,影响了电路的稳定性[2]。因此大部分设计使用Latch-based时钟门控电路,其电路图如下:

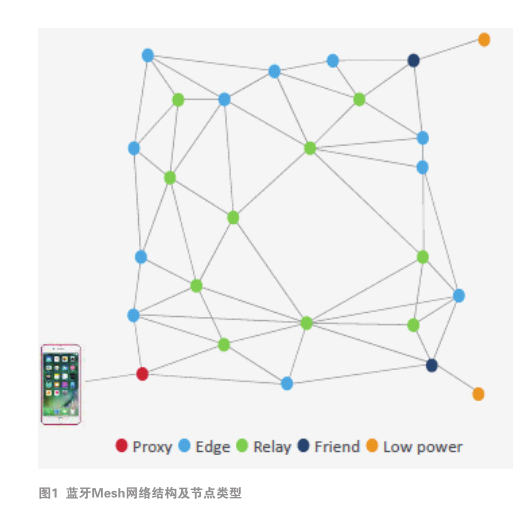

3.2.3实现流程

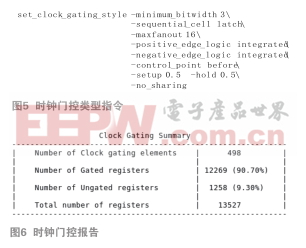

上图描述了利用DC工具插入时钟门控单元的流程,首先是选定时钟门控类型,然后读取RTL设计文件、定义时钟策略,再插入指定类型的时钟门控单元,最后逻辑综合的过程[2] 。其中选取时钟门控类型是最关键的环节,具体命令如下:指定使用基于latch的门控电路类型,-minimum_bitwidth意味着一个门控时钟至少需要3个寄存器,指定时钟上升沿/下降沿触发的寄存器所用的门控单元,-setup/hold指定的是setup/hold time的约束,-maxfanout指定的是最大扇出数[5]。另外可以查看工具手册,进行更多自定义选择。

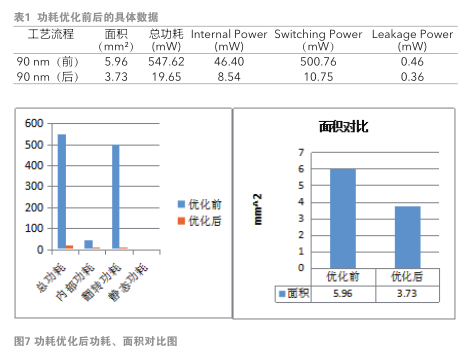

3.2.4 结果分析

基于某ASIC工程在台积电90 nm工艺下进行实践,获得的结果如下:被时钟门控的寄存器占比达90%,因而能控制寄存器翻转,可有效降低动态功耗。统计功耗优化前后的具体数据,如表1所示。在90 nm工艺下,从DC综合后获得的信息来看,可以直观看出功耗降低效果显著,面积也节省了约37%,实践证明时钟门控技术是一种行之有效的降低功耗的方法。

4 结论

本文来源于科技期刊必威娱乐平台

2019年第3期第1页,欢迎您写论文时引用,并注明出处在目前日趋复杂的芯片设计中 , 更 加 追 求 性能、面积、功耗等设计目标,低功耗优化设计已是重要指标之一。本文从设计需求实际出发,首先分析了功耗的构成及来源,然后阐述了功耗评估的方法,最后基于ASIC设计重点讲述了功耗优化的若干方法,并对时钟门控技术做主要说明,并实践证明获得了显著的功耗降低效果[1]。

影响功耗的因素众多,优化的方法也很多,需要结合项目实际,在不同的设计阶段综合运用不同的优化方法来降低功耗,全局综合考虑,以达到功耗、性能、面积等多方面的优化提升[9]。

参考文献

[1] 于立波.芯片设计中的功耗估计与优化技术[J].中国集成电路,2010,19(06):37-43.

[2] 茅锦亮.动态时钟门控管理策略的设计与实现[D].东南大学,2014.

[3] Synopsys. Low Power Methodology Manual[EB/OL].www.synopsys.com/lpmm.

[4] 杨玲.基于电路级的低功耗关键技术研究[D].上海交通大学,2010.

[5] Synopsys. Power Compiler User Guide[EB/OL].www.synopsys.com.

[6] 王彬, 任艳颖.数字IC系统设计[M].西安电子科技大学出版社,2005

[7]喻贤坤,姜爽,王磊,王莉,彭斌.数字集成电路门控时钟可靠性研究[J].电子技术应用,2017,43(01):60-63+67.

[8] 严石.面向DSP的时钟门控技术的优化与设计[D].东南大学,2016.

[9] 袁博.集成电路设计中乘法器的低功耗算法与实现技术研究[D].西安电子科技大学,2013.

作者简介:

尹远(1993-),男,湖南张家界人,硕士研究生,主要研究方向:数字集成电路设计。

黄嵩人(1972-),男,江苏无锡人,硕士研究生导师,主要研究方向:SOC设计,射频识别技术。

本文来源于科技期刊必威娱乐平台

2019年第4期第54页,欢迎您写论文时引用,并注明出处

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码