新型数字反激控制芯片轻松实现高效高功率密度USB PD快充设计

作者 / 英飞凌公司

摘要:主要介绍USB PD应用中的ZVS反激控制器 ,例如手机电脑快充等。主要对控制器的特征、保护、工作和控制原理进行说明和讨论。适合充电器适配器设计人员以及对数字型ZVS反激控制器感兴趣的电源工程师阅读。

关键词:反激;控制;USB PD;快充;零电压开关

0 引言

消费者体会到快充给手机电脑的应用带来了很多的便利,但玲琅满目的快充协议也给用户带来一定的困惑,例如市场上有MTK 的 PE+ 、高通的 QC 4+、 OPPO 的 VOOC、华为的 FCP/SCP,等等,它们往往需要专门的充电器。USB-PD 这个时候得到大范围设备支持,得益于它兼容了其他的快充标准,使得在为数码电子设备充电时不需要必须使用厂家专用充电器材才能为设备实现快速充电,给大家带来更多的便捷。

大家习惯了小型轻便的充电器,如何在不增加充电器体积的情况下提升更大的功率输出,并且支持短时间的峰值输出?这意味着需要更高的频率设计,从而缩小磁性元件和其它被动器件的尺寸,以及采用支持高效率设计的功率器件。在高频的操作过程中,零电压开关由于可以减小主动开关器件的开通损耗而备受欢迎。各种不同的零电压开关拓扑以及相应的控制器都在开发研究当中。取决于输出电流大小,CCM/DCM通常被选用于不同的应用场景。对于USB PD应用,由于输出可变使得定频控制模式下CCM 不可避免。因为定频控制可以使EMI和系统设计相对容易。

英飞凌XDPS21061数字电源方案可以为工程师解决这方便的困扰,数字化电源方案可以提升效率,减少开发周期和系统成本,并且可以加强产品的灵活性,实现更多的差异化。XDPS21061是一款多模式数字式控制器,它同时适用于DCM和CCM 两种工作模式,内部嵌入高压启动单元。该启动单元使得该IC的供电电压在零负载时更加高效和灵活。控制器中的微DSP就像芯片的大脑,它使该控制器比传统的硬件混合信号更加聪明和智能化。XPDS21061的数字和模拟外围设备支持各种信号采样和调控,使其成为反激操作的理想选择。同时它集合了不同的工作模式,如连续模式(CCM)、零电压开关(ZVS)模式、降频模式和突发模式,使得它在不同负载和输入电压下获得最佳的效率。此外,还集成了一次性可编程(OTP)内存,可以提供宽泛的可编写参数,从而简化设计。数字可配置的引脚简化了系统的BOM/PCB布局,不像混合信号IC那样需要大量的外置电阻/电容网络来调节参数。

在本文的最后还介绍了如何更好地利用高效率功率器件(如CoolMOS™和OptiMOS™)以及封装,让设计更加具有竞争性。

1 准谐振反激拓扑面临的困难

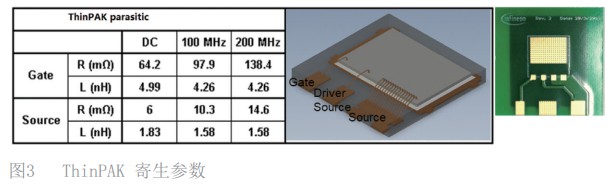

公式1是准谐振反激电路在第一个谷底的开关损耗。Cpara包括MOSFET输出电容和变压器耦合电容。因此在低压输入下,反激准谐振几乎是零电压开关,但是在高压输入条件下,仍然有非常高的开关损耗。

(公式1)

(公式1)

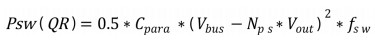

另一个与拓扑相关的损耗是主MOSFET的吸收网络,而且很难算出损耗的准确数值。

在主MOSFET关闭后,在能量注入到吸收网络之前,原边峰值电流首先给主MOSFET的寄生电容进行充电。因此电容越大,寄生电容中储存的能量就越多,吸收网络的损耗就越少。对于硬开关拓扑,寄生电容中的损耗完全丧失掉的。但是对于准谐振反激,这些能量的部分可以被回收。对于完全的ZVS,即使是高压输入,大部分能量也是可以被回收利用的。

注入吸收网络的能量为(0.5*Llk*ipk2-0.5*Cpara*Vsw2)。然而,这并不是全部损失掉,这取决于使用的吸收二极管。使用慢反向恢复二极管可以将部分能量回收至电容或输出,如图1所示。吸收网络仅在Vsw-Vclamp-Vbus>0时工作。这意味着吸收电路的损耗会在高压输入时较高而低压输入时较低。较大的Coss能吸收更多的能量,利用ZVS控制器,意味着更多的吸收能量能够被回收。此外,采用低阻抗的MOSFET可以用来减少导通损耗,同时对吸收部分的耗损也有帮助。

另一个问题是,QR flyback在重载条件下工作频率最低,由于变压器的利用问题这对峰值功率的应用来说是不利的。

QR控制频率变化的问题很容易导致触摸屏的共模式噪声干扰。

为了简化变压器的生产,提出了基于PCB(印制板)的绕组设计。为了减少铜损,频率要求高于100 kHz。此外由于PCB 绕组耦合电容变大,开关损耗也会随之增加。因此一个定频的ZVS 反激控制器必不可少。

2 强制频率谐振零电压开关(FFRZVS)工作原理描述

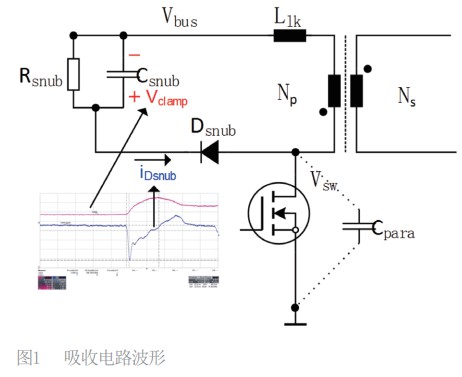

图2显示了ZVS反激电路典型的PWM 时序和相关的关键波形。在主MOSFET关闭之后的时间t4,同步整流(SR)MOSFET将会在一段消隐时间延时之后导通。在时间t5,当消磁电流趋于零时,SR MOSFET关闭,然后激磁电感Lp和Ceqv将会谐振。主MOSFET的电压将从Vbulk+Vrefl谐振到Vbulk-Vrefl,Vrefl=Nps*Vo。如果辅助MOSFET在t1开通,那么主MOSFET谐振在峰值就意味着激磁电流为零,那么imag就会负向增加。在此受控的ZVS开通时间段,主MOSFET的Vds被钳位在电压Vbulk+Vrefl上。一旦峰值电流达到i_zvs_pk,就会关闭辅助 MOSFET,由于电流存储在磁化电感中并且反相,它将继续向这个方向流动,并释放储存在Ceqv中的能量。这个死区时间是由IC的 tZVSdead参数控制的并且是可配置的。在t3时刻,主MOSFET的漏极电压达到最小值,打开主MOSFET,此时达到最低开通损耗。从图中可以看出,ZVS所需能量与Vbulk成正比,ZVS MOS的开通时间也是如此。

MFIO电压是在主MOSFET开通经过一段前沿消隐(LEB)时间后进行采样的。基于这个电压,IC会知道下一个周期的开关频率,例如开关时间Tsw。由于ZVS 开通时间和ZVS的死区时间也是已知的,Tsw-Tzvson-Tzvsdead 决定了ZVS MOSFET开通时间点。

磁化电感用于实现ZVS,所以ZVS只在DCM中有效。用于实现ZVS控制脉冲GD1,只需要其中部分能量的实现ZVS功能,剩余部分将回馈系统。

3 适配器中功率MOSFET 的选型

针对手机快充中原边MOSFET的选择. 我们主要从散热、效率、成本、装配……等几个方面考虑。目前大多数用于手机充电器的功率MOSFET 没有加额外的散热器。这其中考虑到布局的便利,以及成本的问题。因此选择MOSFET的封装时,需要考虑到最大负载情况下温度是否满足要求,一般我们可以测量器件的表面温度,然后通过公式Tj=Tc+P*Rthjc (Tc 为器件壳温,P 为器件的耗散功率,Rthjc为该封装热阻) 来计算结温是否满足设计要求。

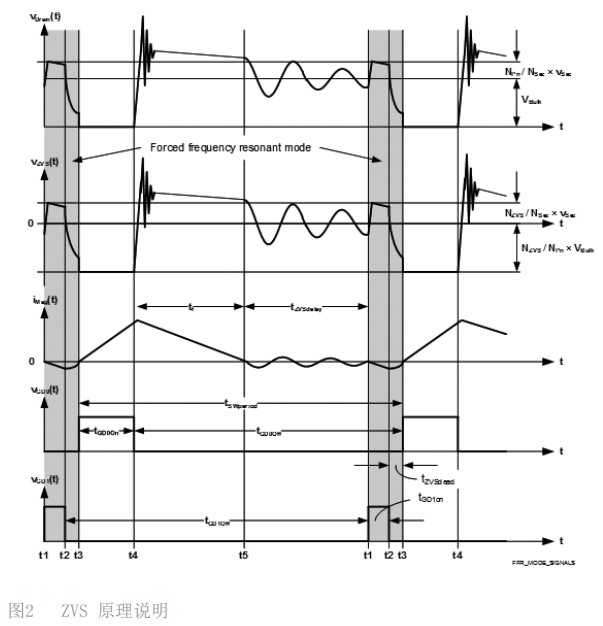

由于成本和空间的要求,其中对器件本身需要具有一定的功率耗散能力,同时也需要满足小尺寸的要求以提升整机的功率密度。通常这两者之间是相互背离的。所以我们会折中考虑。TO247 和D2PAK 此类封装虽然散热性能良好,但是由于封装本身尺寸偏大,并不太适用小型化设计。而一些更小的封装由于本身散热能力问题需要增加额外的散热器,从而增加散热成本。因此,我们通常考虑ThinPAK 封装,如图3所示,该封装兼顾散热和小尺寸的需求,寄生参数也远远比TO 封装小得多,有利于减少尖峰电压。另外它的特点是功率地和驱动信号地隔开,这样大大减少由于MOSFET 源极寄生电感带来的干扰。对系统驱动的稳定性和EMC 设计有较大帮助。

另外TO220 FP 窄脚封装可以支撑直立生产,降低PCB表面连锡风险,同时满足安规绝缘封装、易于安规设计等优点也被广泛地应用于各种充电器设计当中。我们在65 W 单输出设计中选用了英飞凌ThinPAK IPL60R125C7,40 W 设计中采用了TO220 FP IPAN70R600P7S。

副边同步整流MOSFET,较为常见的是SSO8(PQFN 5x6)的封装。根据不同变压器设计和输出电压,可以选择不同电压等级的MOSFET。但对于手机快充来说,通常同步整流控制器由输出直接供电,由于兼容低压输出如5 V 或3.3 V。因此对应MOSFET驱动电压也是5 V、3.3 V。在此驱动电压下普通驱动的MOSFET 并不能工作在饱和区域,因为普通驱动等级的MOSFET 的饱和驱动电压在7.5 V左右。因此我们对于此类应用应选择逻辑电平 MOSFET。我们在40 W设计中采用逻辑电平驱动MOSFET BSC0802LS可以在4.5 V 逻辑电平下饱和导通,可以有效降低同步整流MOSFET 的导通损耗。同时低驱动电压可以进一步降低MOSFET 的驱动损耗,提升效率。

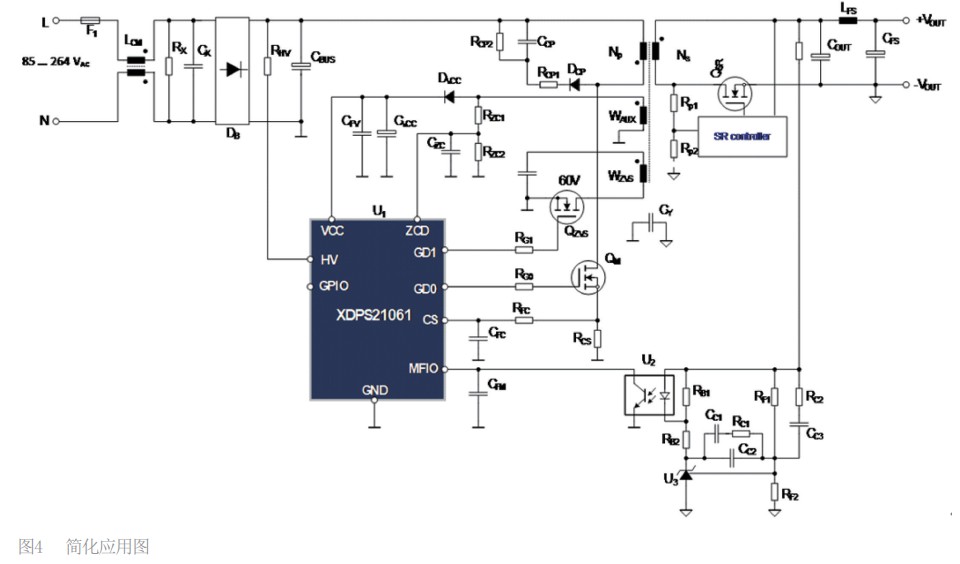

4 简化应用图

图4显示了一款40 W快速充电器设计中采用XDPS21061的简化应用图。与传统的反激和有源嵌位(ACF)相比,它在原边有一个额外的ZVS绕组,以及一个电容、开关器件和一个低端的门极驱动。无需高端驱动和高电压MOSFET并实现零电压开通,因此系统成本很低。

5 轻载工作的设定

突发模式对于初级AC/DC控制IC满足空载要求是很重要的。通常,当反馈低于某个值时,控制IC会进入突发模式。为了减少输出电压纹波,突发模式的迟滞需要尽可能小。这对变输出电压设计具有很强的挑战性。然而,由于是数字控制,XDPS21061基于查表方式进入突发模式,它根据不同的输出电压从而选择不同的突发模式进入条件。

6 65 W 单输出适配器设计实例

我们利用FFRZVS控制器设计了一款65 W全电压输入的适配器。输入90~264 Vac,输出20 V/3.25 A,开关频率Fsw =120 kHz,变压器磁芯采用RM8,匝比Np:Ns=5,Lp=12 µH,输入电容120 µF,原边MOSFET 采用IPL60R125C7,ZVS MOSFET 采用BSL606SN,同步整流SR MOSFET 采用BSC093N15NS5G,SR控制器采用UCC24630。由于散热限制,功率密度可达 15 W/inch3,其中输入部分包含一个共模电感和一个差模电感。

7 基于dpVision® 的可配置人机操作界面

通过一个UART 引脚可以配置各种参数,系统BOM(物料清单)是相当简化的。由于许多应用相关的参数都是可调整的,所以控制器可以根据不同的系统设计而量身定制。例如,可配置频率法则可用于调整最大频率,以适应不同的磁芯形状,并调整半载效率,以平衡导通损耗和开关损耗。也可对突发模式参数进行配置以用于调整突发模式进出功率。

8 总结

XDPS21061是一个基于微DSP的多模式数字控制器,能够工作在不同的电流模式,内部嵌入高压启动单元,可调驱动电流,兼顾数字和模拟芯片优点。人性化人机操作界面,轻松配置系统参数。可以使电源工程师实现高自由度的差异化化设计。基于XDPS21061的快充65 W/40 W设计,采用强制频率谐振,在应对USB PD 可变输出电压下自适应限流,同时整合英飞凌CoolMOS™,OptiMOS™ 等高效功率器件在实现高效设计时游刃有余。可选的抖频功能进一步优化EMI 效果从而取得更高的性价比。

本文来源于科技期刊必威娱乐平台 2019年第2期第23页,欢迎您写论文时引用,并注明出处

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码