宽带数字信道化EDA设计

引言

随着抗干扰通信体制的广泛应用,实现全概率信号截获的接收机是非常需要的,而其关键是实时处理。由于宽带信号接收系统的采样速率很高,很难直接进行实时处理,采用多相滤波结构后,信道化滤波器被分解成多个支路,每个支路的数据经过抽取后可以降低数据率,便于实现并行处理。

对于这种复杂的系统设计,传统的设计方法贯彻自顶向下的设计理念不够彻底,不同设计阶段彼此独立,顶层系统设计缺陷、算法劣区不能在前期体现、不具备设计工具协同多层次开发的能力,给后期设计带来很大的阻力。Matlab、simulink及System Generator为今后的设备开发提供了一条自顶向下多层次紧密结合的新思路。

1、数字信道化原理

实现数字信道化的直接方法是设计多个单独的滤波器,每个滤波器具有特定的中心频率和带宽。从理论上来说,每个滤波器都可以独立设计,它们可具有不同的带宽或滤波器特性。这种方法的一个缺点是滤波器组工作时运算是很复杂的。

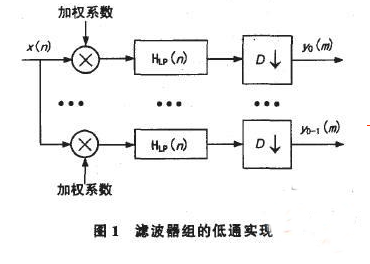

对滤波器组的另一种实现形式就是所谓的低通型实现,如图1所示,其结构与模拟信道化相似。图1中,Hlp(n)为原型低通滤波器,加权系数的作用是把第k个子频带(信道)移至基带(零中频)。整个工作过程如下:采样器将宽带信号采集后形成高速的数字信号,经过不同的复本振下变频到零中频,然后经过一个带宽为信道宽度的低通滤波器。

由于数字信道化接收机的抽取器位于滤波器之后,故当抽取率D很大或滤波器的阶数比较高时,图1所示的信道化结构效率将非常低,利用多相滤波的概念将可以得到上述结构的高效实现。

2、数字信道化设计

数字信道化的实现方式有2种方式:基于离散傅里叶(DFT)结构和基于数字下变频(DDC)结构。

不论是基于DDC的还是DFT,都需要采用多相滤波加DFT的结构实现,与基于DFT的数字信道化不同,基于DDC的信道化结构中保留了原型中的数字下变频结构,各子信道为零中频,便于信号的参数提取。

2.1复信号数字信道化实现

基于多相滤波器结构的数字信道化方法由图1所示的结构推导而来,所有运算在抽取以后进行,因此大大降低了后面数字信号处理的实现难度。

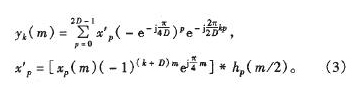

对于复信号,均匀信道常见的划分方式有2种:偶型划分和奇型划分。在偶型划分中第k个带通滤波器中心频率为

在奇型划分中第k个带通滤波器中心频率为: 假设HLP(n)为N阶低通FIR滤波器的冲激响应,经过推导,其第k个信道的输出为:

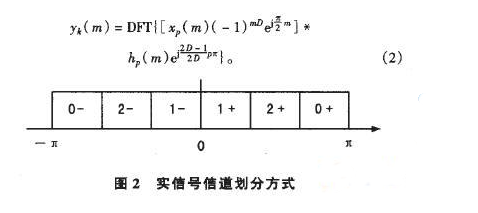

2.2实信号数字信道化实现

上面的数字模型是针对输人信号(x)n为复信号时的结果,但工程中接收到的实际信号大多是实信号,针对实信号的特点,可采取图2所示的信道划分方法。这种划分方法只取信道的正边带或负边带,不损失信息。在这种划分方式下,第无个信道的频移因子可表示为:

根据实信号的信道划分方法,可得到第k个信道的输出为:

2.3非严格抽样数字信道化设计

前面的仿真模型都是假设数字滤波器是理想的,即滤波器不存在过渡带。然而,由于实际滤波器过渡带的存在,不同信道划分方法,或产生盲区,或产生虚假信号。为了解决这个问题,设计滤波器时令其过渡带宽度不大于通带宽度,并且相邻信道的频谱按50%重叠,使各信道的通带拼接后覆盖整个监视频带,同时降低接收机的抽取倍数。采用这种划分方式,接收机不存在接收盲区,但相邻信道50%重叠会使一个输人信号同时落在2个相邻信道上,而产生虚假信号。解决方法是采用非严格抽样数字信号化设计。

采用非严格抽样数字化设计,第k个信道输出为:

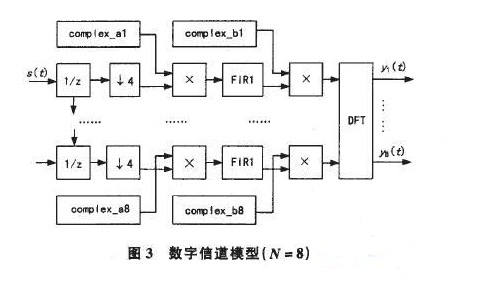

以实信号为例,根据上述表达式,在Matlab软件的Simulink工具箱下,搭建如图3所示的8个子信道的全数字信道化模型。

2.4信号判决

单信道窄带接收机的设计和有多个窄带信道宽带接收机的设计,二者有明显的区别。在窄带接收机中,通过改变本地振荡器的频率可以把信道调谐到滤波器的中心,一旦信号移到滤波器中心,瞬态响应的影响将会最小化。在宽带信道化接收机中,本振的频率和滤波器的频率都是固定的,信号可能落到滤波器的中央,也可能位于2个信道之间。此时,需进行信号判决,这也是数字信道化设计的一个关键问题。

当信道中存在信号时,可根据信号的幅度及相位信息进行综合判断。当信号同时处于2个信道时,相位值会存在2:模糊间题,这时可增大输出数据速率以消除相位模糊问题。

根据信号的幅度信息,同时结合相位信息特征,对于单/多信号的数字信道化结构,可在Matlab软件的simuhnk工具箱下,搭建全数字信道判决模型,消除2∏模糊问题。

利用ismuhkn工具搭建的信号判决模块,其流程简单易懂,便于对该方法的理解。

2.5频率测量

经过信号判决模块后,可知该信道内有无信号存在,如果子信道内存在信号,可通过相位差法获得信号的频率。

考虑到一阶相位差法测频精度低和不利用平均处理的缺点,采用高阶差分法估计频率。高阶差分之前,应对相位做解卷绕运算首先进行粗测频,粗测结果大于四分之一采样频率时,对相位做“折叠”处理,即将负频率部分翻转成正频率。之所以选择四分之一采样频率是因为,较低频率不会发生相位的正负翻转,同时选择四分之一采样频率作为分界线能够适应较低的信噪比。

仿真发现,差分阶次越高,测量精度越高。一阶差分会引起中间测量结果的抵消,为了尽可能地利用有限的相位数据,并尽可能提高差分阶次,如果测量得到N个相位数据,则做N/2阶的差分运算。仿真发现,绝大多数频率测量精度达到10-4数量级。

3、硬件实现

通过上述的设计仿真,很好地解决了系统设计中的多层次开发问题,能够在统筹总体设计的同时兼顾算法和真实复杂信号状态的系统性能分析,大大加深了设计的深度和广度,充分地进行了全数字仿真。但需求不仅于此,由于系统为数字系统,其实现平台为超大规模数字集成电路处理阵列。目前,如Motorola、TI、xilinx、Altera等大的硬件生产商均提供面向Mailab的硬件开发平台,在高速数字信道化接收机中,应用Xihnx的FPGA,故而使用simulink设计工具System Generator进行针对以上仿真的后续设计,使得simuhnk的仿真平台可以进行面向底层硬件开发的设计分析,进行半实物仿真,将EDA开发的水平和分析推人一个新的层次。设计流程主要有3步:

①原理模型设定:主要完成系统中硬件实现DSP功能模块的建立,在本设计中已经通过前面Simulink的设计仿真模型,得到了数字信道化接收机的原理模型;

②搭建设计模型:主要完成原理模型的迁移,使用xilinx的设计1具System Generator在simulink下搭建硬件可实现的模型设计。通过使用该设计工具可以实现理论模型向硬件设计的转移,继而进行硬件设计仿真和半实物仿真。以32信道为例,设计中需要32点的全并行蝶形运算FFT结构,通常使用的F打IP核不能满足实时N点更新的需求,设计了多模块并联结构FFT算法;

③仿真验证:利用Mattab中的Link for Modelsim模块可以实现硬件设计的RTL级仿真,轻松验证硬件设计的正确性,考量算法转化中的指标、量化误差性能等,而且Simulink还支持硬件设计的半实物仿真功能,可以将硬件设计加载到最终的硬件平台上。在本文设计中,最终通过JTAG电缆将simulink中的仿真模块用实物替代,实现半实物仿真。

4、结束语

本文利用Matlab、System Generator等工具实现了数字信道化仿真,解决了信号判决及频率测量模糊问题,并用通用硬件平台验证了仿真的正确性,对于工程系统设计具有一定的指导意义。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码