基于FPGA的Petri网的硬件实现

1、引言

Petri网是一种系统的、数学的和图形的描述和分析工具,它具有强大的描述并发、异步、分布、并行、不确定/随机性的信息处理系统的能力,目前已被广泛应用于计算机通讯系统、实时多媒体系统及离散事件系统的研究中。而Petri网的硬件实现将为并行控制器的设计提供一条有效的途径。因此,其硬件实现成为许多专家、学者研究的热点。

现场可编程门阵列FPGA是美国Minx公司于1984年首先开发的一种通用型用户可编程逻辑器件。它具有容量大、速度高、价格低的优点,同时,硬件描述语言VHDL具有的强大的行为描述能力及与硬件行为无关的特性,实现了硬件电路设计的软件化,这为Petri网的硬件实现提供了有力的工具。

本文探讨了Petri网基于VHDL语言的FPGA实现。

2、Petri网基本类型的实现

2.1基本Petri网的实现

2.1.1基本Petri网简介

定义1 六元组Z=(P,T,F,K,W,M0)称为一个网系统,其中N=(P,T,F)是一个有向网,满足:

1)P∪T≠φ

2)P∪T=φ

3)F∈PxT∪TxP,只能从P->7或T->P,不准P->P或T->T.

4)Dom(F)∪cod(F)=P∪T

K,W,M0依次是N上的容量函数,权函数和标识,M0称为∑的初始标识。基本Petri网就是K=1,W=1,这时库所内的标识数要么是0,要么是1,而且所有的弧权都是1。对于基本的Petri网,变迁的激发就是一个瞬时事件。

2.1.2基本Petri网的元件实现

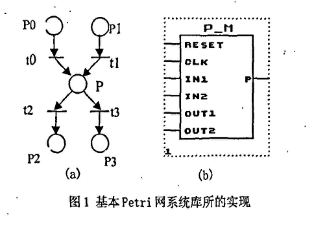

图1(a)是一个简单的基本Petri网系统,库所P具有两个输入变迁和两个输出变迁,当库所P中没有托肯且库所PO或P1中有托肯时,变迁t0或11激发,则托肯从库所PO或P1移动到库所P;当P中有托肯且库所P2或P3中没有托肯时,变迁t2或0激发,则托肯从库所P移动到库所P2或P3。

实现库所P的模块如图1(b),元件几M有两个输入变迁inl,in2和两个输出变迁。outl,out2,当变迁使能时,其值为逻辑1,否则为逻辑0;reset为复位信号,用来置库所的初始状态。clk为全局时钟。P的值表示库所中是否含义托肯,若含有托肯,取值为逻辑1,否则为逻辑。。元件PM是在EDA软件Max+PlusII中采用VHDL语言描述,经过编译、仿真后形成模块。

用VHDL语言描述源程序如下:

entity p_mis

port(reset,clk:instdlogic;

inl,in2,outl,out2:instdlogic;

p:outstdlogic);

end p_m;

architecture beh ofp_m is()P

signal p0,np0:stdlogic;

begin

np0-not p0;

process(clk,reset)

variablefstdlogic;

begin

f:=((inlorin2)and

ifclk'eventandclk='1

ifreset='1'then

p0='1';

elsiff='1'then

(a).(b)

np0)or((outlorout2)andp0);

.then

PO=npO;

endif;

endif;

endprocess;p=p0;

end beh;

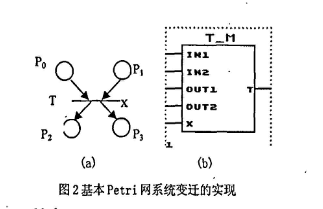

图2(a)是一个简单的基本Petri网系统,其激发规则是当库所PO和P1中有托肯,变迁T具有两个输入库所PO和P1,P3,而库所P2和P3中没有托肯,且事件x两个输出库所P2和发生时,变迁激发。图2(b)是建立的变迁元件T_M,inl,in2,outl,out2分别表示输入库所和输出库所中含有托肯的状态,若含有托肯,则取值为逻辑1,否则为逻辑0,x是外部事件。T表示变迁的激发状态,若可激发则取值为逻辑1。

用VHDL语言描述源程序如下:

entityt_mis

port(inl,in2,outl,out2,x:in std_logic;

t:out stdlogic);,

end t_m;

architecture beh of t_m is

signal t0:stdlogic;

begin

t-x and in land in2 and (notoutl) and (notout2)end beh;

库所元件P_M和变迁元件T_M均存放在Max+Plusll中建立的元件库中,可以调用使用的。

2.2时EEPetriR的实IT

2.2.1时延Petri网的定义

定义2变迁时化Petri网(timed petri net)TN={P,T,F,I'],其中I':T->0∪R+,规定TPetri网中的每一个变迁的持续时间。{T,P,F}的定义与PN一致。

在变迁时化Petri网中,每个变迁均有一为零或任一正实数的持续时间。而库所中没有持续时间,只要和它相连的变迁发生,库所就可失去或获得托肯。当变迁的输入库所中含有托肯时,变迁是可激发的,但要真正激发需要经过一段持续时间。

2.2.2变迁时化Petri网元件的实现

变迁时化Petri网中库所元件与基本Petri网一致。

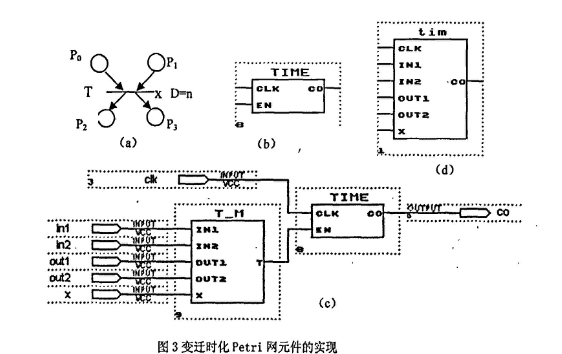

变迁时化Petri网中变迁元件的实现是在基本Petri网中变迁元件的基础上设计了一个计时器TIME,如图3(b),clk为计时频率,决定了计时的精度;en为其使能端,当变迁可激发时,en为1,计时器开始计时,计时结束时co输出为t。图3(a)是一个简单的变迁时化Petri网,变迁T与时延D=n相连,当库所PO和P1中各有一个托肯时,变迁T获得发生权,但到T发生,需有n个单位的延时.调用元件几M和计时元件TIME,建立逻辑电路如图3(c)示,并经过编译形成图3(d)所示逻辑模块时化变迁元件。

用VHDL语言实现计时器模块源程序如下

if clk'event and clk='1'then

if en='l'then

if q=nthenq=0;co='1';

elseq=q+lco='0':

end if;

else q=0;co='0'

end if;

end process;

endbeh;

3、应用举例

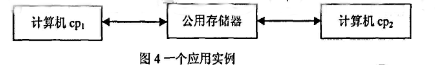

两台计算机使用一个公共存储器,(a)不需要该存储器,(b)需要存储器但还没有使用它;(c)正在使用存储器。

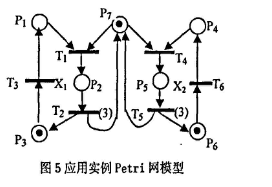

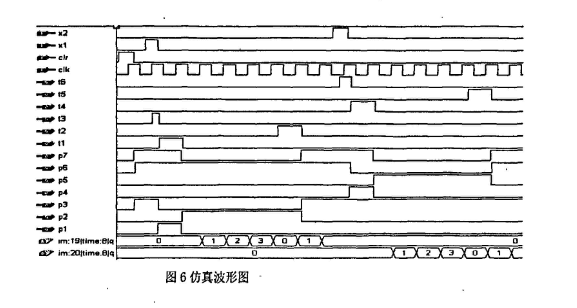

则对其建立Petri网模型如图5示。各库所和变迁的含义解释为:P1,P4分别表示CPI,CP2发出需要该存储器请求;P2,P5分别表示CPI,CP2占用该存储;P3,P6分别表示CPI,CP2不需要该存储器;P7表示存储器;变迁中与时间相关的是T2.T5,分别表示cp占用存储器的时间。这是一个时延Petri网系统。分别调用元件库中所形成的库所元件、变迁元件和时延变迁元件,作出该系统的逻辑电路图,并在EDA软件Max+PlusI中对其编译、仿真下载,仿真波形如图示。

4、结论

Petri网是异步并发现象建模的重要工具,Petri网的硬件实现将为并行控制器的设计提供一种有效的途径.这使Petri网的硬件实现显得尤为重要。本文给出了基本Petri网系统的硬件实现方案,采用VHDL语言分模块实现,描述元件的功能并将元件存入WORK库中,使设计具有很强的可读性、可重复性、及可修改性,大大提高了系统的开发效率。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码