基于CPLD的测试系统接口设计

引言

CLPD(复杂可编程逻辑器件)兼容了LPD(可编程逻辑器件)和通用门阵列的优点,具有编程灵活、可实现较大规模电路的特点,同时具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定、可实时在线检验等优点,因此广泛应用于产品的原型设计和产品生产之中。

1、CPLD在测试系统中的作用

随着计算机和微电子技术的迅猛发展,单片机技术被广泛应用到各种智能仪表、工业控制及家用电器控制领域。但是它们在提高电路板的集成度、增强系统功能的同时也带来了很多测试和维修上的问题。传统的测试仪器和设备(如万用表、示波器、逻辑分析仪等)已不能适应现代测试要求,更无法快捷地诊断出系统的故障所在,因此给一个产品的生产和维护带来了诸多困难。

为了提高诊断效率,我们设计了一套基于虚拟仪器的单片机电路板故障测试诊断系统。

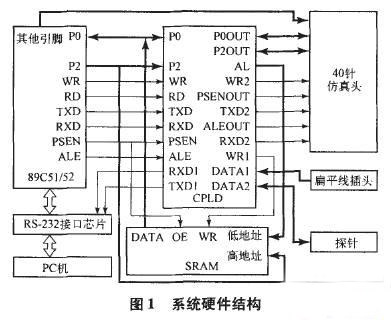

本系统接口的硬件部分由仿真cPu、sRAM、RS232接口芯片、各种接插件加上核心控制电路构成(见图1)。对于核心控制电路可以考虑两种方案:一种是采用TL集成电路块如74LS573、74璐135、74LS24、74璐245等几十个芯片构成;另一种是采用CPLD构成。

下面对两种方案进行比较。

1)可靠性

CPL/DFPGA的可靠性极高,几乎可将整个系统下载于同一芯片中,从而大大缩小了体积,易于管理和屏蔽,而传统的TTL器件数量多、体积大,由此带来的故障隐患大,可靠性低,故障诊断困难。

2)可调整性

CPL/DFPGA可以通过软件编程而对其硬件的结构和工作方式进行重构,它采用先进的JTAc-ISP和在系统配置编程方式,在十SV工作电平下可随时对CPLD进行全部或部分地在系统编程,其编程次数多达1万次,而传统竹L器件不能再改变其逻辑功能,即使设计有误也无法很快进行调整。

3)可移植性

由于开发工具的通用性、设计语言的标准化以及设计过程几乎与所用CPLD的硬件结构没有关系,所以设计成功的各类逻辑功能块软件有很好的兼容性和可移植性,它几乎可用于任何型号的CPLD中,而传统的TL器件根本不具有可移植性。

4)开发周期

由于相应的EDA软件功能完善而强大,仿真方式便捷而实时,开发过程形象而直观,兼之硬件因素涉及甚少,因此可以在很短时间内完成十分复杂的系统设计,而传统的TrL器件从设计原理图、印制版图到制板、调试至少需花几星期时间,更不用说调试成功需花的时间可能长达数月之久。

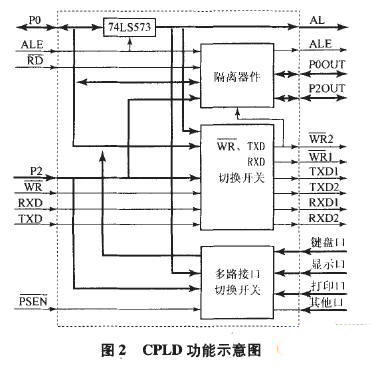

由以上比较可以看出,用CPLD实现系统硬件的核心控制电路更加合理。CPLD的功能示意图见图2。

本测试系统中,cPLD的主要功能是切换wR、TxD和RxD这3根信号线,因为CPU在通信状态和仿真状态时都要用到这3根信号线。当接口板在与PC机通信时,这3个信号输人CPLD后输出为wRI、TXDI和RXDI;当CPU执行测试程序发送测试数据到被测板时,它们又从CPLD输出切换为WRZ、TxDZ和RxDZ。CPLD的另外一个主要工作是隔离接口板上的邵口、咫口的地址数据线和ALE、PSEN等控制线,防止被测板上的故障影响到自身工作。从图1可以看到,即OUT、P2OUT、ALEOUT,PSENOUT正是印口线、PZ口线、ALE线、PSEN线经隔离后才送到仿真头的信号,而CPU的其他信号如PI口、T0,T1等则直接送到仿真头上。另外,输出信号AL是经过锁存的低地址信号线。测试结果的取回有3种方式:总线数据和SRAM、ROM的测试结果通过仿真头从邵OUT送人CPLD隔离后由即口送入CPU;显示接口、键盘接口等接口数据通过ro针或16针扁平电缆插头从DATAI送人CPLD隔离后也由印送人CPU;其他一些远离总线的电路节点则通过探针从DATAZ送人CPLD后再送人CPU。

2、CPLD的设计

CPLD的设计是硬件系统中最重要的一环。从需要使用的FO引脚和硬件资源考虑,决定选用Altera公司MAX700()S系列中的7128SLC84一15芯片。该芯片内部有128个逻辑块、64个FO引脚,PLCC封装,可以在+SV和+3.3V下工作。

硬件描述语言全部采用VHDL。这种语言的特点在于将一项工程设计或称设计实体(可以是一个组件、一个电路或一个系统)分成外部(或称可视部分)和内部(或称不可视部分)两部分,然后再设计实体的内部功能和算法。

如图2所示,在本测试系统中CPLD要实现以下功能:

a)用做单片机系统中的外部低地址锁存器,相当于74璐573。

b)用做通信CPu和仿真CPU之间的切换开关。

因为接口板中的CPU在与PC机进行通信时需要用到控制线TXD、RXD,在往SRAM中写数据时需要用到WR线,而在仿真测试用做仿真CPU时所有的3根总线均要提供给被测板,所以必须对两种状态都要使用的控制线进行切换。切换的方法是在单片机的程序中执行几条指令,这类似于Flash的防误操作方法。向外部数据存储器地址FFFEH写数据9H,即

MOVXDPTR,#OFFFEH

MOVA,#99H

MOVX @DPTR,A

就可以将CPU切换到仿真状态。

往FFFFH写数据55H,即

MOVX DPTR,#OFFFFH

MOVA,#55H

Mov xnDPTR .A

就可以将CPU切换到通信状态。

具体的原理是在CPLD内部用vHDL语言设计了一个切换开关。向FFFEH地址写9H,切换开关在WR下降沿检测到此时的低地址为FEH、高地址为FFH、数据为9H时,就将WR信号输出到WRZ引脚,而WRI引脚输出为高阻状态;同理,往FFFFH地址写5H,则将WR信号输出到WRI引脚,而WRZ引脚输出为高阻状态。因此,每次切换须同时满足3个条件(低地址、高地址、数据)均相同。这样,当用做仿真CPU时提供给被测板的数据地址空间几乎是全空间的,发生误切换的概率几乎没有。

c)用做取回测试结果通道的切换开关。因为被测单片机电路板有可能不止一个FO接口,每个接口的测试数据都要由刊口送人单片机,这就需要一个切换开关来控制几条通路的数据输人以防止数据冲突。

采用的方法是给每个通路人为地分配一个程序存储空间地址,如键盘口为8082H、显示口为8083H、打印口为8084H等,使用MOVC指令来打开通道,即

MOVDPrR,#8082H

CLRA

MOVC A,@DPTR+A

这是将键盘口的测试结果通过8针的扁平电缆取回。

MOV DPTR,#8083H

CLRA

MOVCA,@DPTR+A

这是取回显示口的数据,同理可取回其他口的数据。

具体原理是在CPLD中设计了一个多路转换开关,以键盘口为例,转换开关的条件是当PSEN为低,低地址为82H,高地址为80H时输人键盘口的数据,不理会其他口的数据。

d)隔离接口板与被测板上的邵口、PZ口及控制线。如果不隔离两个板上的三总线,当被测板发生故障必将影响接口板,使得接口板根本无法工作,更谈不上对被测板进行故障诊断。PI口不用隔离是因为PI口不属于三总线。

具体的工作原理是用CPLD模拟单片机内部即口的时序,即先送出低地址,再送出数据。分析PO口读写外部数据存储器的时序可知,读周期中,低地址在ALE为高电平时送出,而数据在RD上升沿时读人;写周期中,低地址也在ALE为高时送出,外部器件在WR为低电平时打开,保证数据在低电平时有效写人。

在后面波形图中可以看到时序符合数据的有效读人和送出。P1口没有特别时序要求,输人CPLD后直接输出。

e)直接驱动一个LED灯闪烁。通过计数AEL次数来翻转电平,这样可以判断CPLD或接口板上的单片机是否工作正常。

3、CPLD的仿真

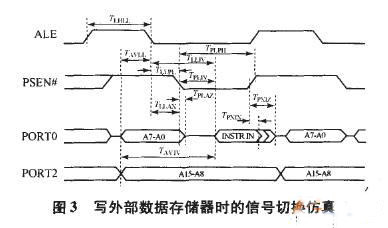

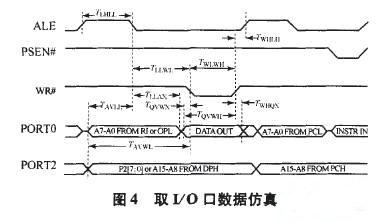

在用VHDL语言完成CPLD的设计并编译通过后就可以进行波形仿真,仿真主要是验证设计的时序是否满足实际的运行情况,所以仿真的条件须大致模拟系统的实际工作条件。本系统模拟的条件是晶振为11.092MHz的单片机时序。

按照单片机写外部数据存储器的时序进行切换WR、RxD、TXD信号仿真,从仿真波形图上可以看出,在发出切换到仿真CPU指令后WR入RxDZ、TxDZ能在下一个周期分别输出WR、RxD、TxD信号,而wRI、RXDI、TXDI都延迟几纳秒后变成高阻;同理,在发出切换到通信CPU指令后也能正确地切换。仿真图如图3所示。

按照单片机读外部程序存储器时序进行取I/0口数据仿真,从仿真波形图上也可看出,在发出取I/0口数据的MOvc指令后,数据结果延迟一段时间后开始出现在数据总线上,但只要在PSEN上升沿来到时数据还能保持,CPU就可以有效读人。仿真图见图4。

另外,数据线、地址线的隔离也比较理想,可保证数据线上的数据有效写人外部器件和有效读入数据。

4、结束语

经过实践证明,本测试系统接口应用CPLD后大大简化了电路,提高了系统整体性能,使系统具有了集成度高、灵活性强、可靠性高、易于升级和扩展等特点。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码