HDL仿真器基于事件的仿真算法

目前,HDL仿真器主要有三种实现算法(机制):基于时间的算法(Time-Based)、基于事件的算法(Event-Based,EBS)和基于周期的算法(Cycle-Based,CBS)

基于时间的算法适合处理连续的时间及变量,其会在每一个时间点对所有的电路元件进行计算。但是,在大部分情况下,每一个时间点只有约2%~10%的电路处于活动(运行)状态,所以该算法效率非常低。

基于事件的算法适合处理离散的时间、状态和变量。该算法只有在电路状态发生变化时才进行处理,只仿真那些可能引起电路状态改变的元件。仿真器响应输入引脚上的事件,并将值在电路中向前传播。目前来说,该算法效率最高,且应用最为广泛,大部分的商业仿真器都是基于该种算法进行开发的。用某仿真器厂家的宣传语,就是“Evaluate When Necessary”。

基于周期的仿真算法以时钟周期为处理单位(与时间无关)。其旨在时钟边沿进行计算,不管时钟周期内的时序,且只是用两值逻辑(0和1)。该算法主要针对的是大规模设计(尤其是数字IC设计),且只能应用于同步电路。

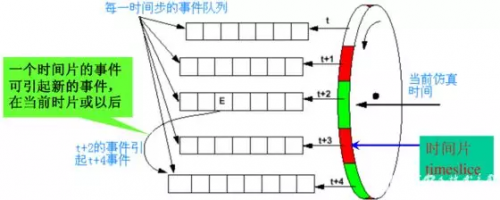

下面详细介绍一下基于事件的仿真算法:

仿真器在编译数据结构时建立一个事件队列;

只有当前时间片中所有事件都处理完成之后,时间才能向前;

仿真从时间0开始,而且时轮只能向前推进。只有时间0的时间处理完后才能进入下一时间片;

在同一个时间片内发生的事件在硬件上是并行的;

理论上时间片可以无限,但实际上受硬件(如电脑的CPU等)和软件(如该仿真软件是否支持多线程技术等)的限制。

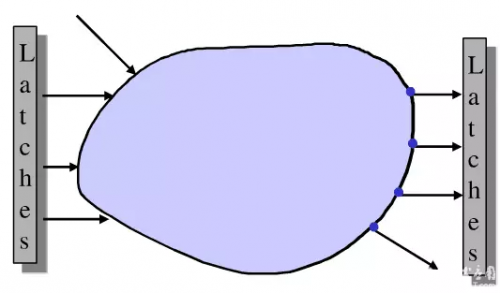

而基于周期的算法只会在时钟的边沿来计算组合逻辑的输出结果,因此基于周期的算法速度更快,内存的使用效率更高。同时,因为基于周期的算法不允许进行严格的时间约束,所以其仿真时间精度没有基于事件的算法高(since cycle-based simulators do not allow detailed timing specificity, they are not as accurate. )。基于周期的算法的原理图,如下图所示:

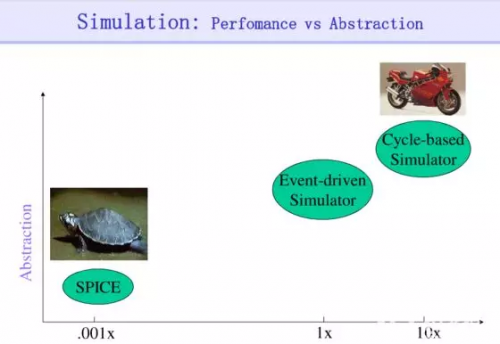

基于事件的算法,基于周期的算法和传统的电路仿真软件SPICE的比较图:

目前基于事件的算法的仿真器(EBS Simulator)主要有:

Modelsim、ActiveHDL、NC-Verilog、Verilog-XL、VCS(Verilog)、Scirocco(VHDL)等。

基于周期的算法的仿真器(CBS Simulator)主要有:

Modelsim、Synopsys Cobra等。

其中Modelsim同时支持EBS和CBS。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码