FPGA设计开发软件Quartus II的使用技巧之: 典型实例-SignalTap II功能演示

5.10典型实例9:SignalTapII功能演示

5.10.1实例的内容及目标

1.实例的主要内容

本节旨在通过给定的工程实例——“正弦波发生器”来熟悉AlteraQuartusII高级调试功能SignalTapII和IntentMemoryContentEditor的使用方法。同时使用基于AlteraFPGA的开发板将该实例进行下载验证,完成工程设计的硬件实现。在本节中,将主要讲解下面知识点。

·QuartusII原理图输入方式。

·QuartusII约束设计。

·QuartusII工程编译。

·QuartusII硬件下载。

·SignalTapII在线调试。

·IntentMemoryContentEditor在线修改片上ROM数据。

通过这些知识点,按照实例的流程,读者可以迅速地掌握使用QuartusII软件高级调试技巧。

2.实例目标

通过详细的流程讲解,读者应达到下面的目标。

·熟悉QuartusII原理图设计方法。

·熟悉SignalTapII在线调试方法。

·熟悉IntentMemoryContentEditor在线修改片上ROM数据的方法。

5.10.2实例详解

本实例将使用图解的方式将整个流程一步一步展现给读者,使读者能够轻松掌握开发的流程。

5.10.2.1工程系统框图

本实例使用QuartusII自带的宏模块(MegaWizardPlug-inManager)来设计逻辑功能,并使用嵌入式硬件逻辑分析仪观察结果。

正弦函数发生器的原理比较简单,硬件实现也比较简单:首先设计一个ROM用来存放正弦函数的幅度数据;用一个计数器来指定ROM地址(也就是相位)的增加,输出相应的幅度值。这样在连续的时间内显示的就是一个完整的正弦波形。

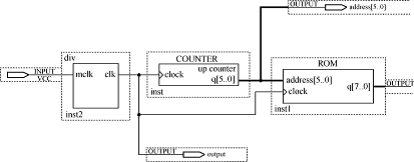

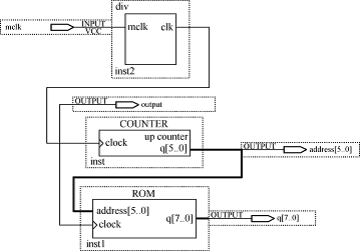

系统的电路图如图5.40所示。

图5.40系统电路图

div模块是分频模块,可以用前面设计过的分频器的程序生成模块(symbol),也可以使用Altera的计数器宏模块来生成分频器。

5.10.2.2添加分频器模块

1.将分频文件添加到工程

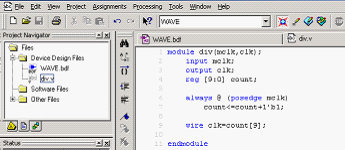

将分频器模块div.v加入到工程中,在工程中打开分频器模块div.v(分频器程序由读者完成),如图5.41所示。

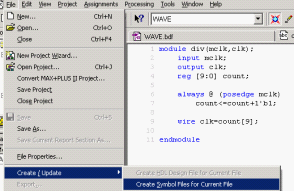

2.产生.bsf文件

选择“File”/“Create/Update”/“CreateSymbolFilesforCurrentFile”选项。软件会自动分析div.v程序的语法错误,如图5.42所示。

图5.41分频器VerilogHDL文件

图5.42生成模块菜单

3.修改程序语法错误

如果出错则修改错误,直到没有错误为止。此时软件会自动生成div.bsf文件,此文件为原理图中的模块图形。

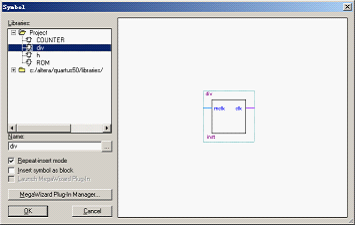

4.在原理图中加入分频器模块div.bsf

在原理图文件中单击“”按钮, 就可以加入刚刚建立的模块,如图5.43所示。

就可以加入刚刚建立的模块,如图5.43所示。

图5.43在原理图中添加分频器模块

5.10.2.3添加QuartusII系统自带宏模块

ROM和计数器都可以通过QuartusII自带的宏模块生成。

1.建立ROM初始化文件

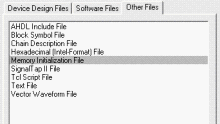

在菜单中选择新建文件,在“OtherFiles”中选择“MemoryInitializationFile”选项,如图5.44所示。

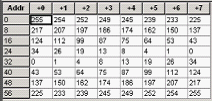

填入如图5.45所示的正弦波幅度数据。当然也可以用MATLAB、C++或Excel的函数生成数据。保存文件,命名sin.mif。

图5.44新建ROM初始化文件图5.45输入正弦波幅度数据

2.添加自带宏模块

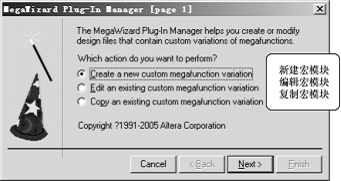

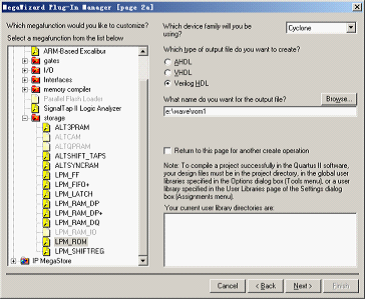

在“Tools”菜单中选择“MegaWizardPlug-PnManager”选项,出现如图5.46所示的对话框,选择新建宏模块单击“Next”按钮。

图5.46引用自带宏对话框

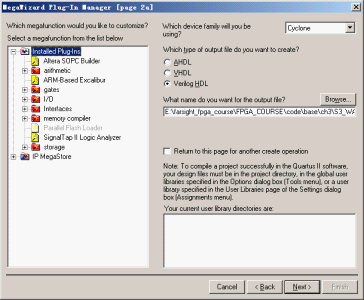

图5.47左侧是QuartusII自带的免费的宏模型,可以看到Quartus提供了很多免费的IP核。

其中ROM在storage目录中,计数器counter在arithmetic目录中。

3.添加ROM

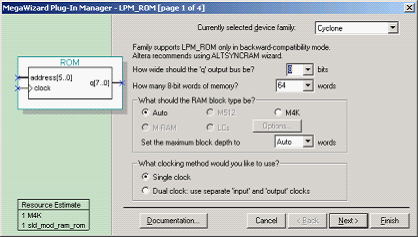

在storage中选择ROM,并在右侧的选项栏中选择Cyclone系列芯片,outputfile类型选择VerilogHDL,并在下方选择ROM文件的生成地址及名称,如图5.48所示。

图5.47选择系统自带宏模块

图5.48选择ROM宏模块

单击“Next”按钮,设定ROM基本参数,包括ROM的位宽q、地址位宽(存储深度)和时钟。一般ROM的时钟选为单时钟控制Singleclock,如图5.49所示。

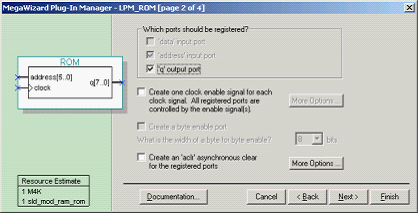

单击“Next”按钮,设定ROM其他参数,设定输出寄存器、时钟使能端和异步清零。如果选中“qoutputport”,则会在输出端加一级寄存器,如图5.50所示。

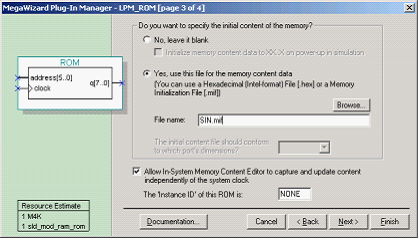

单击“Next”按钮,接下来在对话框中填入ROM初始化文件,并选中“allowin-systemmemory”选项,并选择名称为“NONE”,如图5.51所示。

图5.49rom宏模块基本参数设置

图5.50设置ROM宏模块其他参数

图5.51设置ROM宏模块初始化文件

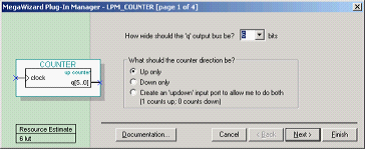

单击“Next”按钮,完成设置,向导生成的文件如图5.52所示。

图5.52设置ROM宏模块完成

4.添加计数器

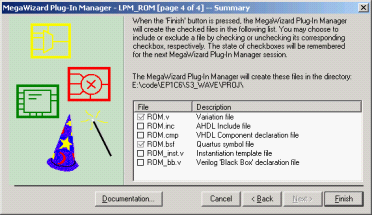

引入计数器作为ROM的地址,当计数器地址递增时,相应的ROM的地址递增(正弦波的相位增加)。同样的在“MegaWizardPlug-InManager”中选择arithmetic数学库中的“LPMCOUNTER”宏模块,添加计数器,如图5.53所示。

图5.53新建计数器模块参数

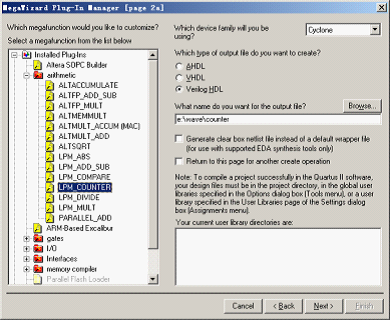

本实例中用的ROM宽度为8,深度为64,也就是数据宽度是8位,可以存64个数据。ROM有64个地址,因此计数器的位宽要定义为6位,如图5.54所示。

图5.54设置计数器宏模块参数

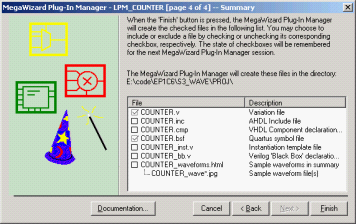

一直单击“Next”按钮,使用系统默认设置,直到生成如图5.55所示的文件输出。

图5.55完成计数器宏模块设置

5.10.2.4添加端口

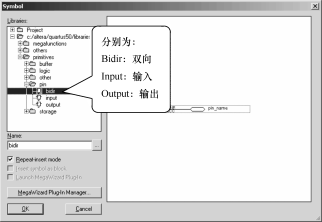

要添加输入输出端口,选择 按钮,打开如图5.56所示的对话框,然后选择需要增加的端口形式。

按钮,打开如图5.56所示的对话框,然后选择需要增加的端口形式。

图5.56加入输入输出端口

添加后双击端口,给端口命名,总线型端口要命名name[N..0]的格式,如图5.57所示。

图5.57完成工程原理图输入

5.10.2.5编译工程

按照2.5节进行语法分析,指定FPGA设备,指定管脚,整体编译程序。在本实例中只需要对主时钟管脚进行分配,即pin_153。

5.10.2.6使用SignalTapII观察波形

1.建立SignalTapII文件

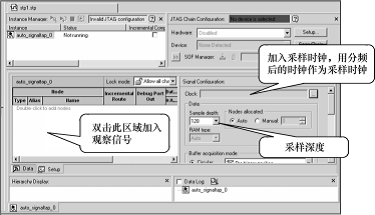

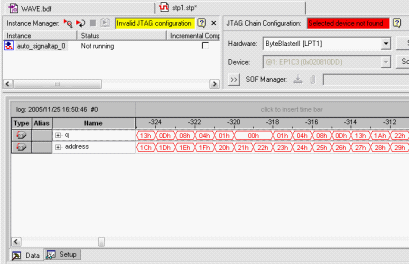

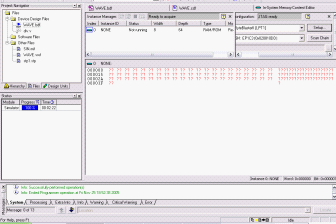

在菜单中选择“Tools”/“SignalTapIILogicAnalyzer”选项,打开如图5.58所示界面。

图5.58新建SignalTapII文件

作如图5.59所示的设置。

图5.59SignalTapII文件设置

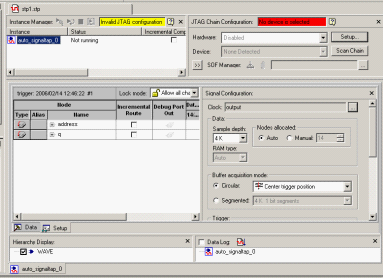

SignalTapII基本设置需注意以下问题。

(1)分频时钟作为采样信号,不要放到被观察的信号中。

(2)采样信号不宜用作主时钟,可以用作分频后的时钟,采样条件可用Centertriggerposition。

下载程序,就可以看仿真的波形了。

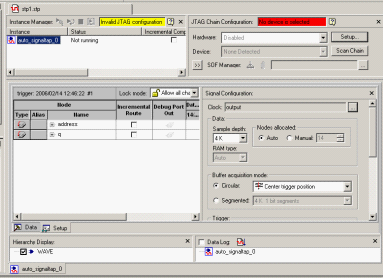

2.设置SignalTapII高级触发条件

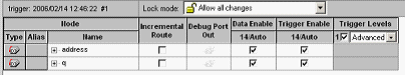

在如图5-58所示的添加观察信号区域窗口中,将TriggerLevels选项改为Advanced,将Basic改为Advanced,则会弹出高级触发设置页面,如图5.60和图5.61所示。

图5.60打开SignalTapII文件高级触发设置

图5.61SignalTapII文件高级触发设置

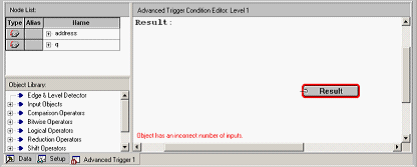

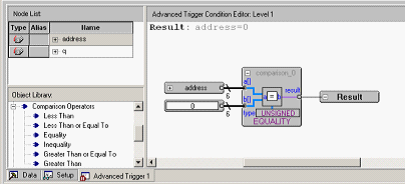

本例中设置为当地址信号address=0时开始触发。从“nodelist”中拖入address信号,在“ObjectLibrary”/“ComparisonOperator”中加入equality,最后加入“InputObjects”/“BusValue”。得到如图5.62所示的触发条件。

图5.62SignalTapII高级触发设置结果

3.运行SignalTapII并观察波形

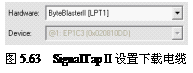

首先整体编译工程,在菜单栏中单击 按钮,开始编译。之后使用JTAG模式将程序下载到FPGA中运行。打开SignalTapII文件,选择如图5.63所示的下载电缆。

按钮,开始编译。之后使用JTAG模式将程序下载到FPGA中运行。打开SignalTapII文件,选择如图5.63所示的下载电缆。

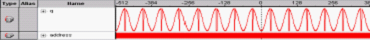

在InstanceManager中单击 按钮进行一次触发,将会得到如图5.64所示的波形。

按钮进行一次触发,将会得到如图5.64所示的波形。

图5.64观察采样数据数字显示波形

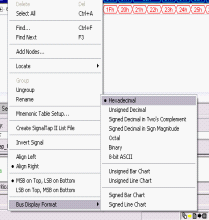

因为开发板硬件没有AD/DA功能,要想看模拟信号的输出也可以用逻辑分析仪来完成。在信号名(比如q信号)上单击右键,选择“BusDisplayFormat”/“UnsignedLineChart”选项,如图5.65所示。

图5.65观察采样数据模拟显示波形 图5.66观察采样数据模拟显示波形结果图

此时,就可以显示如图5.66所示的模拟波形了。

5.10.2.7使用在线ROM编辑器

嵌入式存储数据编辑器是通过JTAG下载电缆来观看FPGA中ROM加载的数据的,不仅能观看,还能在线修改数据,无需重新编译与下载。

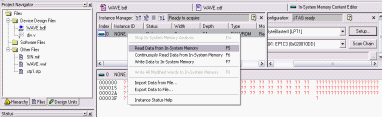

1.打开ROM编辑器

选择“Tools”/“InsystemMemoryContentEditor”选项,打开如图5.67所示的rom编辑器。

图5.67打开在线ROM编辑器窗口

2.选择下载电缆

使用打印口LPT1下载电缆,如图5.68所示。

图5.68设置下载电缆

3.选择ROM标号

点击设置ROM参数时指定的none的文件,将出现FPGA运行之中的ROM的数据,如图5.69所示。

图5.69选择ROM标号

4.读取ROM数据

右键单击“NONE”,选择“ReadDatafromSystemMemory”选项,就可以得到ROM中的数据了,如图5.70所示。

图5.70读取ROM数据

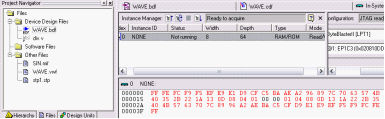

5.修改ROM数据

通过编辑器,可以修改ROM中的数据。例如可以把数据中的几个数改成0,然后单击“write”,再回到逻辑分析仪中观察波形,就可以发现其中的变化,如图5.71所示。

图5.71修改后ROM数据显示

5.10.3小结

上述训练流程就是一个完整的QuartusII硬件调试流程。虽然此训练实现的功能比较简单,但对于初学者来说,是一个不错的入门训练。其主要目的是让初学者对的设计有一个初步的了解。通过该训练来熟悉QuartusII的高级调试技巧,为今后的学习打下基础。

关键词: QuartusII SignalTapII FPGA

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码