FPGA设计开发软件Quartus II的使用技巧之: LogicLock逻辑锁定工具使用技巧

5.8LogicLock逻辑锁定工具使用技巧

5.8.1逻辑锁定方法学

逻辑锁定方法学(LogicLockMethodology)内容就是在设计时采用逻辑锁定的基于模块设计流程(LogicLockblock-baseddesignflow),来达到固定单模块优化的目的。这种设计方法学中第一次引入了高效团队合作方法:它可以让每个单模块设计者独立优化他的设计,并把所用资源锁定。

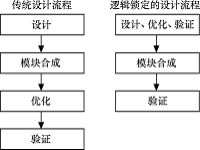

这样在合成顶层设计时就可以保持每个模块的性能,而且它还让逻辑模块可重复使用,提高了资源利用率,缩短了设计周期。逻辑锁定的基于模块设计流程与传统设计流程对比如图5.37所示。

图5.37两种设计流程比较

5.8.2逻辑锁定优势

性能不变,而设计周期更短。使用LogicLock约束,逻辑模块只需优化一次。通过约束达到性能要求后,LogicLock区域的回传机制将此性能指标保持不变。例如,设计人员可以在设计中使用一个PCI宏函数,锁定布局和性能指标。在设计中,加入其他逻辑模块或者在其他区域中改变逻辑都不会影响PCI核的性能。LogicLock流程减少了完成一个工程所需的设计周期数量。

更强的分层次设计流程。设计人员通过LogicLock流程,可以保持每个模块的特性不变,通过分层次区域实施很快地达到性能指标。采用LogicLock方法学,设计人员或者设计团队可以在设计中独立工作,完成布局布线,优化和对每个设计模块的验证。在集成阶段,只需对整个系统进行验证。布局和每个模块的性能保持不变。

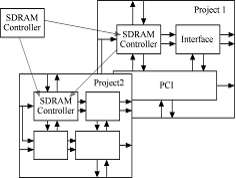

优化的设计重复使用流程。LogicLock约束可以由外部输入。由于LogicLock方法允许将单个约束过的设计模块输入到多个设计中去,因此设计可以方便地重复使用。如图5.38所示为工程师独立开发的模块在多个工程中使用的例子,模块在每个实施中都有相同的性能。

图5.38LogicLock设计的重复使用

5.8.3逻辑锁定参数设置

LogicLock区域参数设置在LogicLock区域中,设计人员可以控制布局。这些区域为真正的分层次设计提供基本构架,设计中改变一个模块不会影响到区域中其他模块的性能。表5.4所示为控制LogicLock区域行为的各种参数含义。默认的选项分别是浮动、自动、关闭和硬区域。

表5.4 LogicLock区域参数

参数 | 选项 | 特征 |

状态 | 浮动、锁定 | 浮动区允许QuartusII软件决定器件上的区域位置。锁定区是区域中用户定义的位置,在图形平面配置图上以实线边界标出,锁定区必须有固定的大小 |

大小 | 自动、固定 | 自动大小区允许QuartusII软件决定区域的合适大小,固定区域含有用户定义的形状和大小 |

保留 | 关闭、打开 | 保留特性允许用户定义区域中的资源能否用于没有分配给区域的实体。如果保留打开,则只有分配给区域的项目才可以在区域内布放 |

执行 | 硬、软 | 软区域有更宽松的时间约束,允许总设计的性能提高后,将一些实体置于区域之外。硬区域不允许将内容放置在区域边界之外 |

原点 | 平面配置图的任一位置 | 原点定义为LogicLock区域放置在平面配置图上时其左上角位置 |

5.8.4逻辑锁定流程

首先,分析整体资源利用率,如果采用的FPGA芯片容量足够,理论上只要保证重点模块的资源利用率,就能保证整体设计的性能;然后采用逻辑锁定的基于模块设计流程(LogicLockblock-baseddesignflow)进行设计,步骤如下。

(1)在Quartus®中综合单个底层模块。

(2)优化重点模块,进行逻辑锁定。

(3)反标(back-annotaing)。

(4)导出模块逻辑锁定约束信息,包括原级网表(atomnetlist)文件(.vqm)、布局信息(placementinformation)文件(qsf)和布线信息(routinginformation)文件(.rcf)。

(5)将这些约束文件导入顶层(top-level)工程中。

(6)编译和验证整个顶层设计。

(7)编译完成后,查看时序分析界面是否达到要求。

以上介绍的逻辑锁定的具体方法可以参照5.11小节。

通过应用一种新的设计方法学——逻辑锁定方法学(LogicLockMethodology),采用了模块化、团队化的设计流程,对重点模块进行优化,解决了传统设计流程无法解决的问题,同时对其他FPGA设计工程中类似的问题提供了可借鉴的思路。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码