FPGA设计开发软件Quartus II的使用技巧之: 编译及仿真工程

5.6 编译及仿真工程

5.6.1 编译

编译的步骤如下。

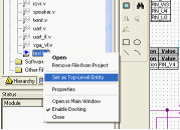

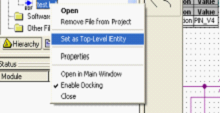

(1)首先把顶层模块设置为Top-Level Entry,如图5.15所示。

(2)选择“processing”菜单的“Start Compilation”选项进行编译,如图5.16所示。

图5.15 设置顶层模块 图5.16 开始编译

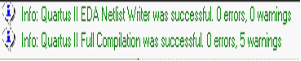

(3)查看“message”栏中的错误,改正直到没有错误为止。

图5.17 编译无错误

5.6.2 仿真

可以使用Quartus II Simulator在工程中仿真任何设计。根据所需的信息类型,可以进行功能仿真以测试设计的逻辑功能,也可以进行时序仿真。在目标器件中测试设计的逻辑功能和最坏情况下的时序,或者采用Fast Timing模型进行时序仿真,在最快的器件速率等级上仿真尽可能快的时序条件。

下面是利用Quartus II Simulator进行仿真的步骤。

(1)设置顶层模块。

Quartus II软件可以仿真整个设计,也可以仿真设计的一部分。通过指定工程中的某一个设计实体为顶层设计实体,即可仿真该顶层实体及其所有附属设计实体,如图5.18所示。

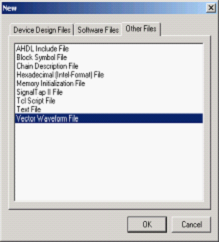

(2)建立波形文件。

选择新建其他文件对话框的“Vector Waveform File”建立.vmf文件,如图5.19所示。

图5.18 设置顶层模块 图5.19 建立仿真波形文件

(3)添加观察信号。

通过图5.20~图5.22向新建的波形文件添加观察信号。

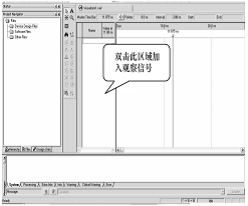

首先通过双击图5.20的空白区域添加观察信号。

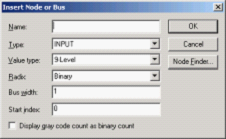

然后在弹出的对话框中填写要插入的信号名,如图5.21所示。

图5.20 在仿真界面中添加观察信号 图5.21 插入信号对话框

也可以使用Node Finder选择指定的信号,如图5.22所示。

(4)添加激励。

通过拖曳波形,产生想要的激励输入信号。可以通过如图5.23所示的工具条为波形图添加信号。

图5.22 “Node Finder”对话框 图5.23 波形控制工具条

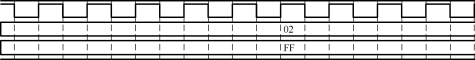

如图5.24所示是添加激励后的波形示例。

图5.24 波形示例

(5)功能仿真。

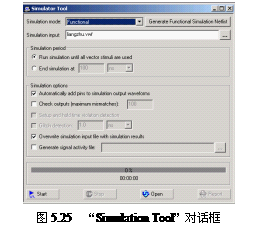

添加完激励信号后,保存波形文件。选择工具栏中“Simulator Tool”工具进行仿真,如图5.25所示。

首先做功能仿真,先单击“Generate Functional Simulation Netlist”按钮产生仿真需要的网表文件,然后把“Overwrite simulation input file with simulation result”选中(否则不能显示仿真结果),单击“Start”按钮进行仿真。

仿真完成后,单击“Open”按扭打开仿真结果,如图5.26所示。

(6)时序仿真。

功能仿真正确后,可以加入延时模型,进行时序仿真。将Simulation mode选为Timing模式,如图5.27所示。

图5.25 “Simulation Tool”对话框 图5.26 仿真结果

图5.25 “Simulation Tool”对话框 图5.26 仿真结果

图5.27 仿真模式设置

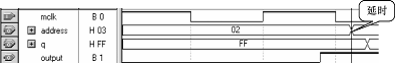

仿真结束后,输出的波形会出现延时,如图5.28所示。

图5.28 时序仿真结果的延时

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码