基于FPGA的循环冗余校验码设计

在现代数字通信中,要求信息在传输过程中造成的数字差错必须足够低。但由于通信信道存在噪声和传输特性不 理想等原因造成了信号

的码间串扰,导致信息在传输过程产 生差错。为了最大限度地保证通信过程中信息的完整性,需 要采用信道编码技术对可能发生的差错进行有效地控制,而 循环冗余校验码就是其中一个最有效的编码技术。

1 循环冗余校验码基本思想

循环冗余校验码是一种校错能力很强且使用非常广泛 的差错检验方法。循环冗余校验码采用在发送的有用码后面 加入校验码来实现数字通信传输过程中数据的差错检测,通 常的构成可以描述为:K位的有效信息数据串和R位的循环 冗余校验码并在一起传输。

1.1 循环冗余校验码生成基本原理

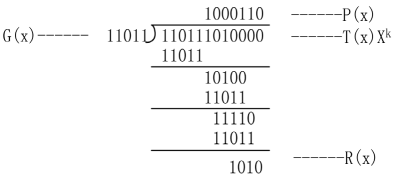

循环冗余校验码(亦称CRC码)在通信信号校错里广泛使 用。其基本原理是,在发送端:将要发送的数据串序列当作 一个多项式T(x)的系数(比如,多项式为T(x)=x5+x3+x+1,则 此多项式的系数就为101011,同时可以自定义一个k次幂的 称为生成多项式的多项式G(x),为了使原来的数据串序列在 后面加入校验码,就必须使其向左移,所以用Xk乘以T(x), 根据对二进制乘法的理解,得到的T(x)Xk,能起到把T(x) 原有数据串序列向左移动k位的结果。为了得到校验码,用 G(x)作除数,T(x)Xk作被除数,相除得到一个余数多项式 R(x)。然后将余数多项式R(x)并在待发送的数据串序列后 面,把这串新的数据串序列作为发送序列发送。在接收端: 再次使用自定义的生成多项式G(x)去除接收到的数据串序列多项式,如果相除所得到的余数多项式和在发送端计算得到的余数多项式相同,则表示信号传输正常,没有出现差错;

如果两者不相同,就表明信号传输错误,就必须检查各方面 因素,重新发送信息,直到两者相同为止。为了更直观地说明循环冗余校验码的生成过程、校验 过程,以8位的有效信息数据串和4位的循环冗余校验码并在 一起传输为例。

生成过程:

(1)假设要发送的数据串序列为11011101。

(2)自定义的生成多项式G

(x)=x4+x3+x+1,其中k=4,相对应的序列为11011。

(3)把待发送的数据串序列向左移动4位,后面补0,从 而得到新的数据串序列为110111010000。

(4)使用模2除法,用生成多项式序列去除新生成的数据 串序列。即

这样得到了余数多项式R(x)对应序列为1010。

( 5 ) 将 余 数 多 项 式 R ( x ) 对 应 序 列 并 到 新 数 据 串 序 列 后 面 , 得 到 带 有 循 环 冗 余 校 验 码 的 数 据 串 序 列 :

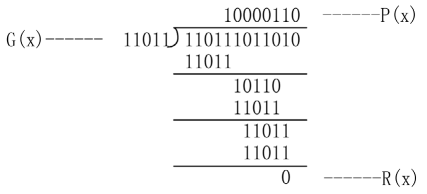

110111011010。 校验过程: 假 如 信 息 在 传 输 过 程 中 没 有 受 到 影 响 而 发 生 错 误 的话,接收到的带有循环冗余校验码的数据串序列必定可以被 在发送端所自定义的生成多项式整除,也就是:

1.2 生成多项式的注意事项 (1)生成多项式的最高位和最低位必须为1。 (2)当所要传输的数据序列任何一位发生错误时,用生

成多项式做模2除法(即加法不进位,减法不借位,实际上就 是数字逻辑里的“异或”操作)后要使相除后的余数不为0。 (3)对于不同的位产生错误时,要使余数也不同。

(4)对余数继续做模2除法时,要使余数循环。

2 Verilog HDL核心程序

2.1 Verilog HDL实现循环冗余校验码的生成代码

其中DXS表示生成多项式PROCESS(clk,rst_n )

VARIABLE dzl: STD_LOGIC_VECTOR(16 DOWNTO 0); VARIABLE sdzl: S T D _ L O G I C _ V E C T O R ( 1 1

DOWNTO 0); BEGIN

IF (clk'event and clk='1') THEN IF rst_n='0' THEN hsd_r<='0';

dcrco_r<=B"0_0000_0000_0000_0000"; ELSIF dload='1' THEN

dzl :=sdata&'0'&'0'&'0'&'0'&'0';

sdzl :=sdata;

IF dzl(16)='1' THEN

dzl(16 DOWNTO 11):=dzl(16 DOWNTO 11) XOR DXS; END IF;

IF dzl(15)='1' THEN

dzl(15 DOWNTO 10):=dzl(15 DOWNTO 10) XOR DXS; END IF;

IF dzl(14)='1' THEN

dzl(14 DOWNTO 9):=dzl(14 DOWNTO 9) XOR DXS; END IF;

IF dzl(5)='1' THEN

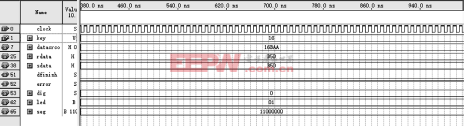

图1 循环冗余校验码的生成、校验仿真

dzl(5 DOWNTO 0):=dzl(5 DOWNTO 0) XOR DXS; END IF;

dcrco_r<=sdzl & dzl(4 DOWNTO 0);

hsd_r<='1'; ELSE hsd_r<='0'; END IF; END IF;

END PROCESS;

2.2 循环冗余校验码的校验代码

PROCESS(clk,rst_n)

VARIABLE rdzl: STD_LOGIC_VECTOR(16 DOWNTO 0); BEGIN

IF (clk'event and clk='1') THEN IF rst_n='0' THEN

rd_r <=X"000";

dfsh_r <='0';

err_r <='0';

ELSIF hrecv='1' THEN

rdcrc_r <=datacrci;

rdzl :=datacrci(16 DOWNTO 0); IF rdzl(16)='1' THEN

rdzl(16 DOWNTO 11):=rdzl(16 DOWNTO 11) XOR DXS; END IF;

IF rdzl(15)='1' THEN

rdzl(15 DOWNTO 10):=rdzl(15 DOWNTO 10) XOR DXS; END IF;

IF rdzl(14)='1' THEN

rdzl(14 DOWNTO 9):=rdzl(14 DOWNTO 9) XOR DXS; END IF;

IF rdzl(5)='1' THEN

rdzl(5 DOWNTO 0):=rdzl(5 DOWNTO 0) XOR DXS; END IF;

IF rdzl(5 DOWNTO 0)="000000"

THEN

rd_r < = r d c r c _ r ( 1 6DOWNTO 5);

dfsh_r <='1';

err_r<='0'; ELSE rd_r<=X"000"; err_r<='1'; END IF;

ELSE dfsh_r<='0'; END IF; END IF;

END PROCESS;

对循环冗余校验码的生成和校验进行了功能仿真,结 果如图1所示。

3 循环冗余校验码的应用

由于循环冗余校验码强大的校验能力,在不同领域, 循环冗余校验码的生成多项式位数也不同,根据IEEE官方 文件显示,为了更好地保证校验可靠度,现在的位数越来越 大,目前最长的循环冗余校验码已达到160位。下面简单介 绍几种常见的循环冗余校验码及其应用领域。

(1)USB接口用CRC5。对应的标准生成多项式:

P(x) = x5 + x2 + 1 (2)ATM协议等用CRC8。对应的标准生成多项式:P(x) = x8 + x2 + x + 1 (3)文件传输通信协议,X25协议等用CRC16。对应的标

准生成多项式:

P(x) = x16 + x12 + x5 + 1 (4)IEEE802.3标准用CRC32。对应的标准生成多项式: P(x) = x32 + x26 + x23 + x22 + x12 + x11 + x10 + x8 + x7 + x5 + x4 + x2

+ x + 1

(5)ISO 3309规定的CRC64。对应的生成多项式:

P(x) =x64 + x62 + x57 + x55 + x54 + x53 + x52 + x47 + x46 + x45 + x40

+ x39 + x38 + x37 + x35 + x33 + x32 + x31 + x29 + x27 + x24 + x23 + x22 + x21 +

x19 + x17 + x13 + x12 + x10 + x9 + x7 + x4 + x + 1

4 结语

循 环 冗 余 校 验 码 已 经 成 为 各 行 各 业 通 信 校 验 中 最 普 遍的校验方式。本设计将循环冗余校验码的生成与校验过 程进行细致的分析,最终采用Altera公司开发的FPFA芯片 EP1C12Q240C8进行结果验证。实验表明FPGA在实现循环 冗余校验码方面有着简单高效的优势。在未来实现更多位的 循环冗余校验中有着更深远的用途。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码