基于WCDMA接收机系统的低噪声放大器设计

摘要 介绍了低噪声放大器的基本工作原理,并对噪声源进行了分析。提出了采用先进的TSMC90 nm工艺,设计了一种基于WCDMA接收机系统的全差分拓扑共源共栅型低噪声放大器。该放大器片内集成了电感、电容。片外配置匹配网络。芯片测试结果表明:电路在2 GHz工作频率下,电压增益达到20 dB、噪声系数NF为1.4 dB、IIP3为-3.43 dBm。综合各项数据表明,该低噪声放大器具备良好的性能,可广泛适用于通讯系统之中。

随着半导体技术和无线通讯技术的发展,无线移动产品已得到广泛使用。作为无线信息接收的最前端部件,低噪声放大器具有其特殊的地位和作用,其性能尤其是噪声系数几乎决定了整个接收链路的噪声性能。本文着重从稳定性、噪声源、线性度、匹配网路关键点进行分析,并针对WCDMA接收机系统应用,设计了低噪声放大器,电路采用TSMC90nmCMOS工艺。芯片测试结果表明,该低噪声放大器,电压增益达到20 dB、噪声系数NF为1.4 dB、IIP3为-3.43 dBm。

1 低噪声放大器工作原理

低噪声放大器设计难点主要在于高增益、低噪声系数、高稳定性、低功耗以及良好输入输出匹配网路等关键指标上的平衡。下面着重从这些关键性能上,对低噪声放大器电路进行分析。

1.1 输入阻抗分析

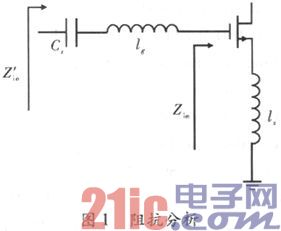

低噪声放大器LNA输入级结构通常为图1所示。输入MOS晶体管源级接电感L,栅极电感lg以及电容Cs为匹配网络。从图1电路分析得LNA输入阻抗Zin

式中,Cgs为输入晶体管的栅源寄生电容;gm为跨导,根据TSMC工艺技术文档可查,此输入管工作电流为2.65 mA,偏置电压为2.25 V的情况下,特征频率ωT约为30 GHz,因此可通过ls值来匹配出50 Ω纯电阻,Zin的虚部则可与Cs和lg匹配,使得Z’in的虚部为零。

若不考虑谐振工作频率而只考虑源阻抗匹配则无需lg电感,但LNA是窄带工作,因此必须确保在工作频率上谐振与lg作用相同。匹配网络本身具有增益,在工作频率上最好使得匹配网络的增益达到最高,即匹配网络谐振也必须在工作频率上。在设计过程中可通过观察,LNA和匹配网络各自的电压增益曲线来进行验证。根据工作频率2 GHz和阻抗匹配确定lg为22 nH,Cs为10 pF。图4为匹配网络电压增益。

1.2 噪声分析

图1匹配网络下LNA的噪声分析。其噪声源主要有MOS管的沟道噪声,电感lg的串联寄生电阻和MOS管栅极多晶电阻Rg的热噪声,以及信号源内阻的热噪声。沟道噪声

设计时需考虑匹配网络上的电感lg存在寄生电阻的,即电感的Q值不可能是无穷大,所以要尽量选用Q值高的电感应用。另外,还需尽量减小MOS管的栅极多晶电阻,在画版图时栅极输入线应尽可能短或减小连接孔电阻,而从噪声系数表达式看,也可通过调节gdo和特征频率来降低噪声系数。

1.3 线性度分析

线性度是低噪声放大器的一个重要指标,如何提高系线性度是设计的难点。图1中输入晶体管源极所接电感ls一方面起着输入阻抗匹配的作用,同时也可用以提高放大器的线性度,达到源极负反馈提高线性度的作用。输入晶体管的电流为

从式中可看出,若电感的阻抗远大于跨导的倒数,则电流是跨导的弱函数,而与输入电压可近似为线性关系。设计时可适当增大跨导gm,但功率不能过高,同时器件尺寸不可过大,以避免因线性度提高而导致其他指标变差。

1.4 增益和隔离度分析

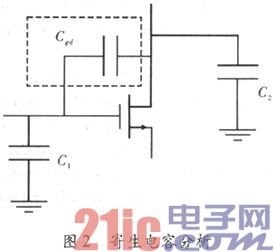

增益是低噪声放大器的原则性指标,如何提高其增益而不降低其他性能,是分析和设计的重点。图1共源管的寄生电容Cgd等效栅到地的电容和漏到地的电容分别为C1、C2。

C2≈A×Cgd,此时的C2直接为输出端的寄生电容,共源管的沟到电流将由C2和负载分流,负载阻抗值较大,而电容C2越大阻抗越小,从而分的电流也将越大,这也将降低增益,并将影响输出谐振网络。另外输入和输出可直接通过Cgd在高频下形成信号通路,这使得逆向隔离差甚至可能输入输出闭环不稳定。为了避免增益损耗和逆向隔离差的问题,可采用共源共栅结构取代共源结构的低噪声放大器LNA。在采用共栅管连接之后由于共栅管的栅极高频下为虚地,因此寄生Cgd形成的信号通路将避免,从而改善了逆向隔离性能且提高了稳定性。采用共栅连接C2将变小为

同时从漏往上看的阻抗变为

,这便增大了阻抗的电流增益,并将提高LNA的电压增益。

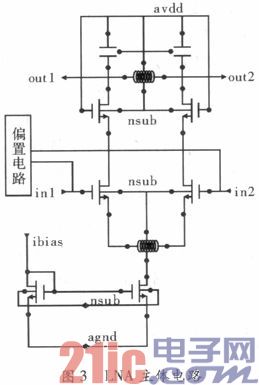

2 整体电路设计

通过对低噪声放大器LNA性能分析,综合设计了一个全差分拓扑型共源共栅结构的低噪声放大器,电路主体结构如图3所示。电路采用全差分输入和输出,差分输入一方面可提高放大器的增益,另外一方面可拓宽放大器的输入信号动态范围。采用共源共栅结构即可提高增益也可增强隔离度。负载通过电感和电容组成,而并非采用电阻,目的是减小输出级噪声。此外,输出还需匹配网络,通过其在2 GHz频率下谐振,产生一个虚拟的负载电阻。电路中采用TSMC电感为4抽头射频器件,有利于差分结构的对称使用。

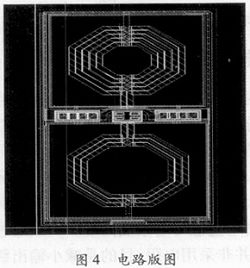

3 版图设计

整体上版图按照对称紧凑进行。同原理图类似,同样是上面布局为输出谐振电感,中间布局为电容和共源共栅放大器以及偏置电路的电阻,为了完全对称,偏置电路电阻采用了两个等值电阻并联,如图1所示。接下来布局为源级电感,最下方布局为偏置电路和电流镜的MOS晶体管,其W相同,只是finger数目不同,这有利于版图的对称和紧凑。版图连线上严格按照电流密度来设定线宽,高频信号线采用135°折线连接,连接孔处尽量采用多孔连接。由于不同的金属层的位置不同以及自身的单位长度上寄生电阻值的差异,因此选用金属层连接需充分考虑以上情况。金属5和金属6寄生电阻值小,且为顶层金属。因此电感和电容采用以上两层金属连接,版图上需尽量使差分输入线的寄生电阻小,LNA版图上充分的加大了线宽和减小连线长度以此减小噪声。

4 芯片测试

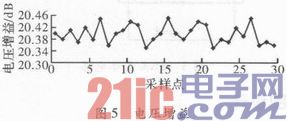

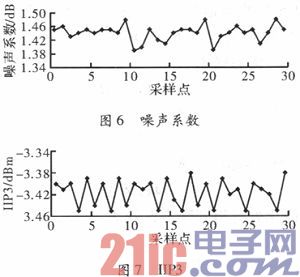

电路通过TSMC90nm工艺代工流片。主要测试点有噪声系数、线性度、电压增益等指标。线性度反应的是信号经过低噪声放大后的失真程度。其衡量指标有1 dB压缩点和IIP3 dB压缩点。1 dB压缩点反应的是信号随着强度增加,低噪声放大器对信号非线性放大。IIP3 dB是指信号频率附近的干扰信号同有用信号产生的三阶交条信号对有用信号的干扰程度。采用瞬态测试,输入一个大小为20 mV的2 GHz正弦信号,测试输出正弦信号的大小以测得放大器的增益。取30颗样片分别测试并记录其性能指标,电压增益、噪声系数、IIP3压缩点测试结果分别如下图所示。统计结果分析表明电路的一致性较高,满足应用要求。

5 结束语

文中基于Tsmc0.18μmCMOS工艺,设计了一个全差分的共源共栅低噪声放大器。在电路片内集成电感,在版图上布局。经样片测试结果表明,该电路可获得稳定的输出性能,且一致性高。正常工作条件下,平均电压增益达到20.4 dB,噪声系数为1.44dB,另外IIP3为-3.43 dBm。测试数据证明,该设计具有一定的推广性,可广泛应用于接收机前端放大。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码