建立FETching分立式放大器的一些提示

简介

用于光电二极管、压电以及其他仪器仪表应用的低噪声放大器所要求的电路参数一般是:极高的输入阻抗、低1/f噪声或亚皮安偏置电流等,而提供的集成产品无法满足这些要求。本文讨论使用分立元器件设计低噪声放大器的要求与挑战,并重点探讨了折合到输入的噪声以及失调电压调节。

高输入增益拓扑的限制

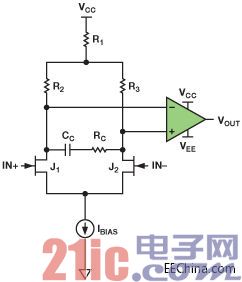

典型分立式放大器如图1所示,在高速运算放大器前使用匹配JFET器件实现的差分放大器,提供高输入阻抗和一定的初始增益。系统噪声主要由输入级产生,因此无需使用低噪声运算放大器。

图1. 高速、低噪声仪表放大器

不过,将输出稳定在低增益和高频率有一定难度。添加RC补偿网络、CC和RC后,即可实现稳定性,但这些元器件的最优值随增益而改变,增加了整体设计的复杂性。另外,大信号响应对于某些应用而言也过于缓慢。

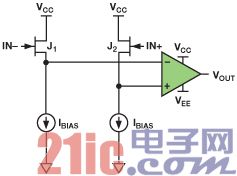

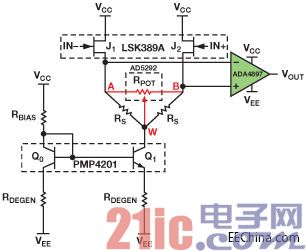

图2所示电路在单位增益处可获得相应的噪声性能,无需进行补偿。速度主要由运算放大器确定。该电路由三个主要部分组成:输出运算放大器、FET输入缓冲器以及对FET进行偏置的电流源。

图2. 单位增益稳定版本的放大器

输入级的单位增益配置对运算放大器的噪声性能有严格要求。在图1所示电路中,输入FET增益有限,从而减少了跟随级的噪声影响。在单位增益配置中,输入缓冲器和运算放大器的总噪声分离,因此需要使用低噪声运算放大器。

输入级电流源

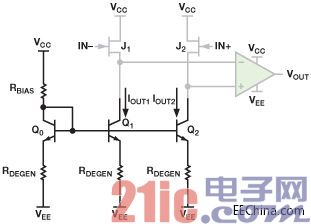

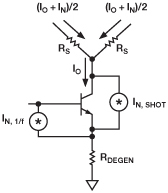

如果部署不当,则用于偏置FET输入缓冲器的电流源会对总系统噪声产生极大的影响。最大程度降低偏置噪声影响的一种方法,是在简单电流镜中添加衰减电阻,如图3所示。

图3. 带衰减的电流镜

流过晶体管 Q0 的电流镜像至晶体管 Q1 和 Q2。噪声源包括1/f以及晶体管的散粒噪声。增加衰减电阻可降低散粒噪声(系数为1 + gmRDEGENgmRDEGEN),但对1/f噪声不起作用。该噪声源以基极和发射极之间的电流建模,无法通过增加RDEGEN而得到改善。若要同时减少两种噪声源,就需要使用不同的电流源架构。

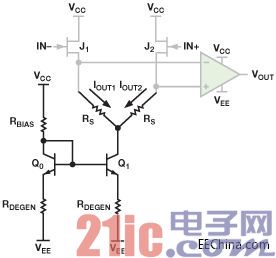

图4. 采用分流电阻的电流镜

修改后的电流镜如图4所示。该电流源所需的晶体管数目较少,允许使用双通道晶体管对代替四通道封装,同时降低尺寸和成本。噪声性能的提升极为明显,因为同时消除了散粒噪声和1/f噪声。晶体管Q0 电流镜像至晶体管 Q1。该电流通过一对电阻在集电极处分割,因此1/f和散粒噪声将会均分。由于噪声源来自同一个晶体管,因此它们是相干的。输出差分信号,因此噪声被消除,如图5所示。

图5. 显示噪声消除的电流源理想示意图

依然可以衰减电流镜晶体管,以便改善电流匹配和输出阻抗。电流由RDEGEN上的压降确定,因此晶体管匹配不如未衰减时来得重要。它允许使用几乎所有的匹配对,但集电极电容必须较低,以保持稳定性。两种方案的差分输入电容保持不变,因为两个输入器件的源间耦合主要由放大器的低差分输入阻抗决定。

出于测试目的,确定偏置电流的基准电压由连接 VCC的电阻设置。因此,如果VCC 发生改变,电路将比较容易产生性能问题。在实际方案中,应使用齐纳、带隙或IC基准电压源 代替电阻。

运算放大器

运算放大器确定整个放大器的速度、噪声、输出性能和失真,因此必须根据应用而选择。表1显示合适运算放大器的典型值。

表1. 相关运算放大器特性

ADA4897 是大部分高速检测应用的优秀备选器件,这类应用要求具备低噪声性能。对于高电压应用,ADA4898 也能胜任。该器件可采用±18 V电源供电,保持低噪声的同时仅消耗8 mA电源电流。两个放大器都采用复合设计,压摆率超过50 V/μs。

输入FET

输入FET确定放大器的输入特性。若要达到最佳性能,则要求FET具有良好的匹配、低噪声以及低输入偏置电流等特性。更重要的是,这些JFET可确定输入失调电压,因此它们必须良好匹配。对于LSK389而言,最大 ΔVGS 为 20 mV,这与 VOS 为 20 mV相当。后文将讨论降低这一相对较高失调电压的技巧。

表2. 相关JFET特性

放大器性能

下文示例中的放大器采用nJFET LSK389A、晶体管PMP4201 以及运算放大器ADA4897实现。评估板如图6所示。

图6. 放大器评估板,包含数字电位计连接

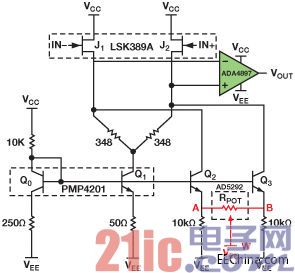

该放大器方案最明显的误差源是高输入失调电压。此失调电压大部分由输入FET的失配所造成,可高达10 mV。(LSK389数据手册声称失配可高达20 mV,但测试中从未看到如此高的数字)。增益为100时,输出失调为1 V,此时放大器基本无用。在该放大器可用作前置放大器之前,需调节高输入失调电压。采用数字电位计 AD5292可完成这一调节。本文介绍基于电位计位置进行失调调节的两种方法。

输入失调电压

放大器测试版本的输入失调电压在1 mV至10 mV范围内变动。输入JFET的失配是造成这一失调的主要原因。LSK389数据手册显示IDSS 的变化量可达10%之多,从而影响到器件的VGS,并引入失调电压。幸运的是,失调源于流过JFET的偏置电流不相等,因此提供这些电流的电流源可加以调节,补偿该误差。获得零失调电压的一种方法如图7所示。

图7. 使用电位计消除输入失调电压

数字电位计(如 AD5141 或AD5292)可用于调节流过输入器件的电流。表3显示这些器件的关键参数,这些器件包括通过SPI接口进行控制的三端电位计,可准确地放置游标,用于精确控制电阻。

表3. 数字电位计规格

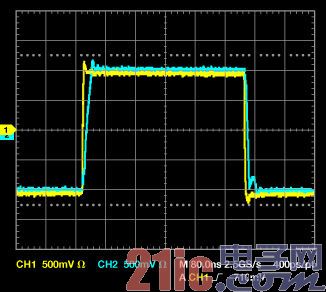

不幸的是,这些数字电位计的端点处具有高寄生电容(最高达85 pF),高频时会造成稳定性和振铃问题。图8显示带与不带该电位计的放大器步进响应。

图8. 放大器步进响应 a) 带电位计 b) 不带电位计 (用于提供失调调节)

85 pF寄生电容连接输入FET的源端与地,高频时产生极大的振铃与不稳定。一种替代的偏置设置如图9所示。该设置可降低输入失调电压,同时保持高频下的低噪声和稳定性。

图9. 使用电位计消除输入失调电压的替代方法

在上述两种偏置方法中,数字电位计用于调节流过每个FET的电流,直到它们的栅极至源极电压匹配,且输入失调电压达到最小值。然而,图9所示的偏置方案可确保电位计的高寄生电容不会产生高频不稳定性和振铃。它将图3和图4中两个不同的电流镜配置相结合来实现。 Q0/Q1 电流镜将其集电极电流分离,作为流入FET的主要电流,从而使偏置晶体管几乎不产生噪声。Q0/Q2/Q3 形成更为传统,但噪声更大的电流镜。这些信号经衰减后仅消耗总FET偏置电流的1%到2%(约30 μA)。它不足以引入大量噪声,但可提供足够的调节信号,轻松调节10 mV失调电压。更重要的是,它可确保电位计的寄生电容不影响输出。由于存在RS 分路器,使噪声保持在较低水平,因此可根据 Q2/Q3的衰减情况可靠调节失调,并且任何电位计寄生效应均不影响输出。图10显示电流镜调节后的步进响应。

图10. 放大器在电流镜处调节后的步进响应

数字电位计 提供调节失调电压的简便方法,允许在宽工作温度和电压范围内最大程度降低失调电压。AD5292集成20次可编程存储器,允许调节失调电压后永久储存游标位置。本电路使用AD5292 评估板连接板外失调调节电位计。对于更为紧凑的设计,可在板上集成数字电位计,并通过其片内串行接口引脚进行编程。

使用这种方法,通过AD5292 20 kΩ电位计可成功将LSK389/ ADA4897放大器的输入失调电压降低至数微伏。

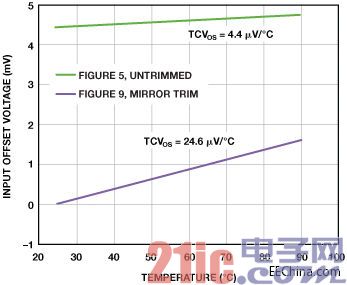

失调漂移

放大器未经过调节时,失调电压温度系数(或输入失调电压随温度上升而增加的比例)约为4 μV/°C。加入AD5292可将该数值提升至大约25 μV/°C。该结果如图11所示。

图11. 输入失调电压与温 度的函数关系

虽然漂移的变化幅度巨大,但放大器的动态范围依然有明显的改进。考虑增益为100且温度为85°C时,未经调节放大器的5 mV失调情况;此时,输出失调为:

VOUT = (VOS + TCVOS × T) × G = (5 mV + 4 µV/°C × 85°C) × 100 = 534 mV.

若相同工作条件下的失调调节为5 μV,则输出失调为:

VOUT = (VOS + TCVOS × T) × G = (5 µV + 25 µV/°C × 85°C) × 100 = 213 mV,

因此,动态范围改善300 mV以上。它同样可提供现场校准和系统级漂移校准,并且该调节技术可进一步改善精度性能。

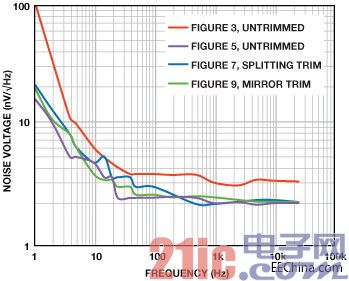

噪声

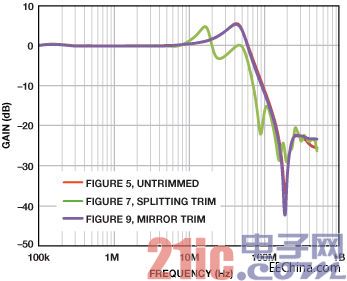

图12. 经不同方式调节后,折合到输入的噪声电压

图12显示不同放大器配置下的噪声密度。该放大器具有2 nV/√Hz的宽带噪声密度,电源电流为8 mA,性能相比现有集成式产品有所改善。10 Hz时,未经调节的1/f噪声为4 nV/√Hz;而1 Hz时为16 nV/√Hz。请注意,传统电流镜(红色曲线)的1/f和宽带噪声都要高出1.5至2倍,而调节后的总噪声几乎保持不变,如其他三根曲线所示。

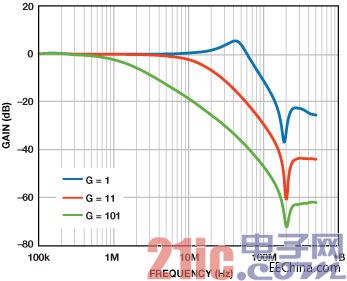

小信号传递函数

图13和图14显示不同增益与调节设置下的频率响应。请注意,经过 RS 调节的放大器不稳定,且未调节情况下的频率响应与电流镜调节后的频率响应相同。

图13. 不同增益下的未调节放大器带宽

图14. 电位计处于不同位置时的单位增益带宽

输入偏置电流

使用增益配置和检测电阻测量输入偏置电流。图4显示不同器件、电压和温度情况下的典型范围。

表4. 输入偏置电流值

结论

随着越来越多的应用要求使用具有高输入阻抗、低噪声和最小失调电压的专业运算放大器,使用分立式器件针对特定应用设计电路也变得越来越重要。本文叙述仅使用4个分立式器件,且具有可调输入失调电压功能的高速、低噪声放大器。文章讨论了每一级的设计考虑因素,并重点介绍了放大器的噪声性能,以及消除散粒噪声和1/f噪声的多种方法。采用运算放大器ADA4897和LSK389 JFET,设计并测试支持单位增益的放大器,该放大器折合到输入的噪声为2 nV/√Hz,且电源电流仅为8 mA。10 mV范围内的高输入失调电压通过AD5292数字电位计进行数字调节。本文还讨论了替代器件,以便适用于不同的应用与环境。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码