在不损失SNR的前提下,将高压信号转换成低压ADC输入

模/数转换器(ADC)电路设计中,特别是当系统设计人员需要处理各种摆幅的电压信号时,很容易产生的一个误区是缩小输入信号范围,以适应ADC的满量程范围,这将大大降低信噪比(SNR)。综合来看,相对于高压ADC,低压(5V或者更低) ADC的选择范围更宽。高电源电压通常会导致大的功耗,电路板设计也更加复杂,例如,需要使用更多的去耦电容。这篇应用笔记讨论了由于信号缩小所引起的SNR损失,如何量化这些损失,以及如何减小这些损失。

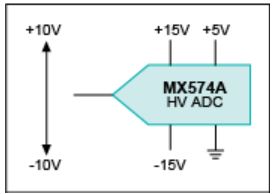

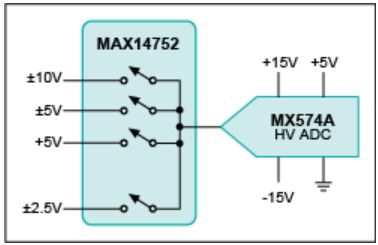

很多传感器或系统输出为高压或双极性消耗,比如,常见的±10V。当然,可以通过一些简单的方法将这些信号送入ADC,进而利用高压ADC处理这些宽范围输入信号,不会造成SNR损失。这些方案通常需要额外的高压电源,以满足输入量程及较大功率的需求(图1所示)。这些高压ADC同时也限制了信号调理(运放)方案的使用。如果信号需要复用高压和低压输入,实际电路的成本将更高(图2)。

图1:MX574A高压ADC能够支持较大的输入信号量程,但也消耗较高功率。为了实现这个方案,必须采用±15V双电源和+5V单电源供电。

图2:多路复用、双极性高压输入ADC系统。

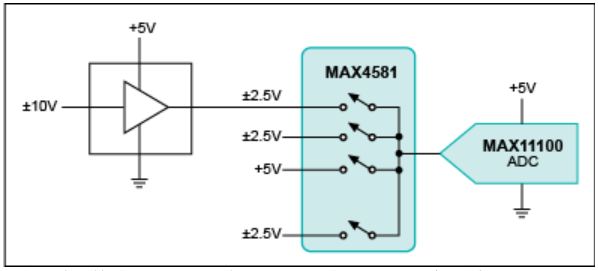

也可以使用一个输入运放,将信号缩小到低压ADC的满量程范围。该信号调理电路可以连接到一个单独的模拟开关输入口(如图3),将所有信号都限制在ADC输入范围以内。

图3:采用单片MAX11100低压ADC和复用器处理高压输入。

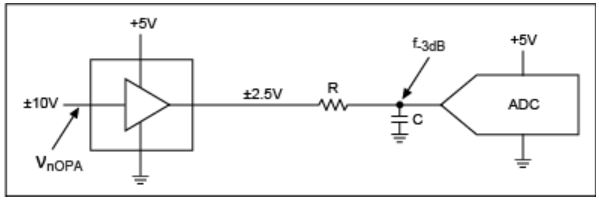

采用运放缩小信号电压范围时,可以将运放噪声等效为运放的输入噪声。这里主要有两个噪声源:运放参考输入噪声和压缩信号产生的ADC输入参考噪声。这两个噪声源组合成一个二次方程。此外,放大器噪声经过ADC输入带宽以及运放和ADC输入之间的抗混叠滤波器滤波,如图4所示。

图4:比例运放引入噪声,但该噪声经过RC滤波和ADC输入网络滤波。

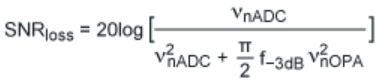

系统SNR(运放输入前端)公式为:

其中:

vnADC= ADC的输入RMS噪声

vnOPA= 运放的输入噪声

f-3dB= 单极点-3dB频率

对于给定的ADC满量程范围、ADC输入参考噪声、运放增益,有两个参数会影响到最终的信噪比损失:滤波器截止频率和放大器输入参考噪声。

如果信号源具有低频成分,可通过设计滤波器使其具有更高的输入噪声容限(在保证低功耗、低成本需求的同时,会牺牲一定的噪声性能)。如果ADC限制了系统带宽,则需要运放具有足够低的输入噪声,以达到SNR的要求。

举一个例子,输入信号为±10V,而ADC满量程输入为5VP-P,ADC SNR为92dB。此时,放大器衰减系数是4倍(将输入调整到满量程)。数据手册提供的ADC输入噪声是44.4nVRMS。假设滤波器截止频率为10kHz,如果采用输入噪声为10nV/√Hz的运放,则损失信噪比为:

SNR(loss) = 0.035dB

如果没有使用滤波器,ADC带宽为10MHz,为了将SNR控制在同等水平,则要求输入噪声为0.3nV/√Hz,设计中很难达到这样的要求。

对于同样10MHz带宽的ADC,如果我们允许SNR(loss) = 0.5dB,则要求运放噪声指标为4nV/√Hz,这一点很容易做到。

目前,具有更高集成度、设计更灵活的解决方案允许不同信号范围的输入,轮训采集每个通道时,编程相应通道的输入增益优化SNR。比如,Maxim的MAX1300系列16/14位ADC提供最多8路输入信号,如图5所示。MAX1300可接受双极性输入信号,最高±12V,只需单5V供电,由此减少了外围器件和供电电源数,进而缩小PCB面积。

图5:MAX1300 ADC具有可编程输入量程(单电源供电支持双极性输入),每个采样可编程放大倍数,内部基准。

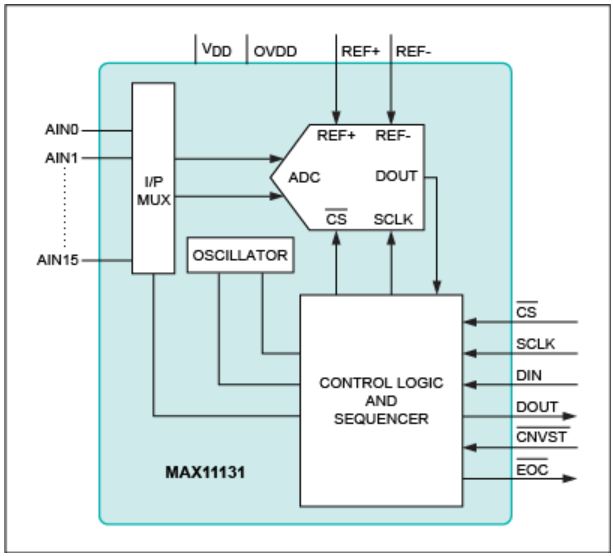

12位MAX11131、16通道、3Msps ADC同样提供了设计灵活性。该器件采用SampleSet?技术,用户可以灵活配置模拟输入通道的采样顺序,允许多达256种任意扫描顺序(图6)。SampleSet技术还允许以非对称形式设置每个通道的扫描频率,灵活处理各个通道的高/低频信号。

图6:MAX11131功能框图,3Msps、12位、16通道ADC提供灵活的SampleSet多路轮询功能。

综上所述,实际应用中,对于给定的系统带宽和SNR损失容限,可以通过加入一个比例放大器将高压信号转换到ADC满量程范围规定的低压信号。对于多量程输入的系统,采用这种方式可以有效地把不同摆幅信号输入到一个多通道的低压ADC。Maxim提供全面的16位到24位数据转换器方案,并在器件内部集成了抗混叠滤波器,非常适合这类应用。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码