基于Multisim的数字钟实验电路的设计与仿真

在电子技术实验教学中,构建学生的电路设计理念,提高学生的电路设计能力,是教学的根本目的和核心内容。数字钟电路的设计和仿真,涉及模拟电子技术、数字电子技术等多方面知识,能够体现实验者的理论功底和设计水平,是电子设计和仿真教学的典型案例。文中采用了555 定时器电路、计数电路、译码电路、显示电路和时钟校正电路,来实现该电路。

1 系统设计方案

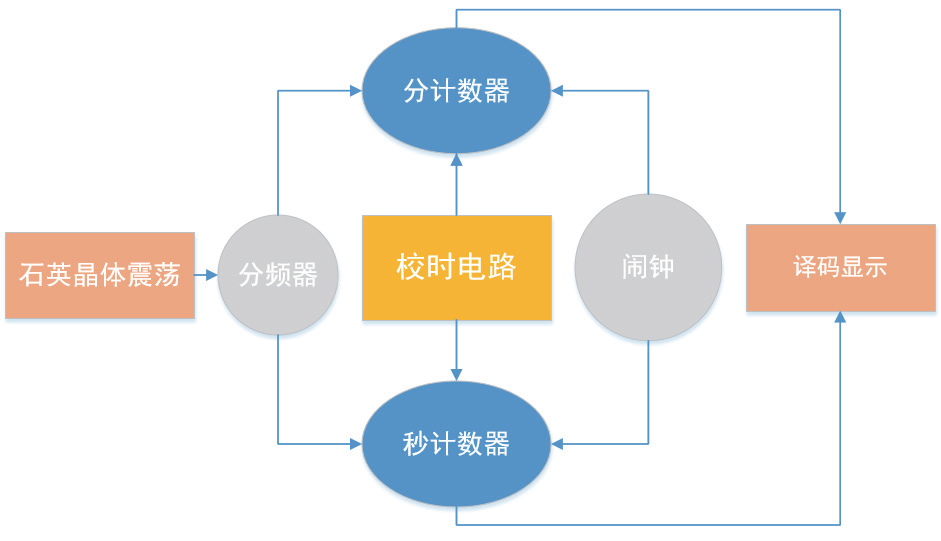

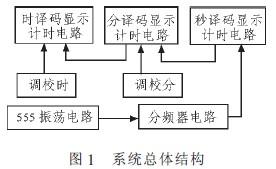

数字钟由振荡器、分频器、计时电路、译码显示电路等组成[1-3]。振荡器是数字钟的核心,提供一定频率的方波信号;分频器的作用是进行频率变换,产生频率为1 Hz 的秒信号,作为是整个系统的时基信号; 计时电路是将时基信号进行计数;译码显示电路的作用是显示时、分、秒时间;校正电路用来对时、分进行校对调整。其总体结构图,如图1 所示。

2 子系统的实现

2.1 振荡器

本系统的振荡器采用由555 定时器与RC 组成的多谐振荡器来实现, 如图2 所示即为产生1 kHz 时钟信号的电路图。此多谐振荡器虽然产生的脉冲误差较大,但设计方案快捷、易于实现、受电源电压和温度变化的影响很小[4]。

2.2 分频器

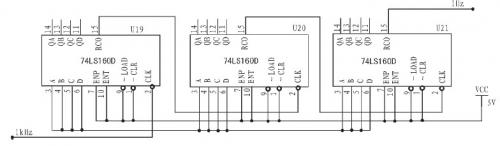

由于振荡器产生的频率高, 要得到标准的秒信号,就需要对所得到的信号进行分频。在此电路中,分频器的功能主要有两个:1) 产生标准脉冲信号;2) 提供电路工作需要的信号,比如扩展电路需要的信号。通常实现分频器的电路是计数器电路,选择74LS160 十进制计数器来完成上述功能[5]。如图3 所示,555 定时器产生1 kHz 的信号,经过3 次1/10 分频后得到1 Hz 的脉冲信号, 为秒个位提供标准秒脉冲信号。

2.3 时间计数器

计数器是一种计算输入脉冲的时序逻辑网络,被计数的输入信号就是时序网络的时钟脉冲,它不仅可以计数而且还可以用来完成其它特定的逻辑功能,如测量、定时控制、数字运算等等。

本部分的设计仍采用74LS160 作为时间计数器来实现时间计数单元的计数功能。时间计数器由秒个位和秒十位计数器、分个位和分十位计数器、时个位和时十位计数器构成。数字钟的计数电路的设计可以用反馈清零法,当计数器正常计数时反馈门不起作用,只有当进位脉冲到来时,反馈信号将计数电路清零,实现相应模的循环计数。

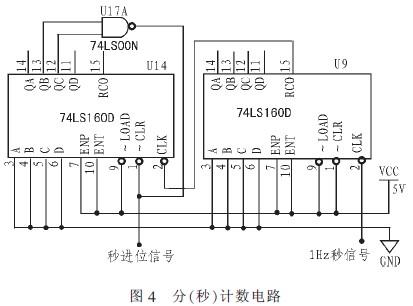

2.3.1 分(秒)计数器

分(秒)计数器均为60 进制计数,如图4 所示。它们的个位用十进制计数器74LS160 构成,无需进制转换,信号输入端CLK 与1 Hz 秒信号相连,进位输出作为十位的计数输入信号。十位采用反馈清零法将十进制计数器74LS160 变成六进制计数器,因为清零端为低电平有效、所以将QB、QC与非后连接到清零端, 即计数器的输出状态为“0110”时QB、QC 输出高电平与非后为低电平实现有效清零并对下一级进位。两级电路组成一位60 进制计数器,其计数规律为00→01→…→58→59→00。当秒计数满60 后向分个位提供一个进位信号,同理当分计数满60 后向时个位提供一个进位信号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码