基于MPSoC的以太网接口设计与实现

研究了以太网在多核系统中的数据通讯,设计了以太网IP核到MPSoC网络资源的硬件接口。阐述了设计中各模块的实现功能和设计方法,通过仿真和FPGA验证结果表明,以太网接口数据通讯具有实时和高吞吐率。实现了多核系统与网络数据的信息传递,硬件设计结构简单、性能稳定可靠。

随着电子信息技术发展,网络通信在日常生活中应用越来越广泛,以太网技术经历了10 Mbit·s-1到10 Gbit·s-1的发展历程。当前电子设备网络化、多媒体技术、数字图像处理技术成为研究的热点,片上多核系统(Multi-processor system-on-chip,MPSoC)在复杂数字系统中成为主要的硬件结构方案。这类系统通常用以太网完成数据通信,以太网接口设计与实现是一个关键部分。

数字系统规模不断增大,随着市场激烈竞争,系统开发周期要求也变得苛刻,目前,片上多核系统基于IP核的设计成为了主流趋势。系统性能的提高,片上集成的处理器数量也不断增多,基于网络结构的片上多核系统相比总线结构的设计优势越来越显著。Xilinx公司和Ahera公司开发的FPGA芯片针对不同型号,都提供了许多不同类型和不同功能的IP核。然而,复杂数字系统,采样FPGA实现,在开发难度和成本上占有明显优势。

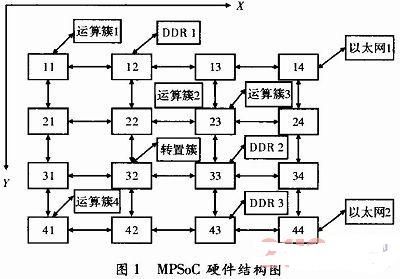

1 MPSoC系统架构

MPSo采用NoC(Network-on-Chip,NoC)通讯结构,处理器和IP核通过资源接口与网络通讯。系统结构如图1所示,处理器与IP核采用总线通讯方式形成簇结构,簇、以太网模块和DDR模块通过资源接口与网络进行通讯。图中运算簇集成了两个处理器,完成数据运算,转置簇集成一个ARM控制器承担数据的行与列交换,DDR模块为片外存储芯片的控制器,以太网承担着系统的数据通讯模块,主要实现系统的数据传输。

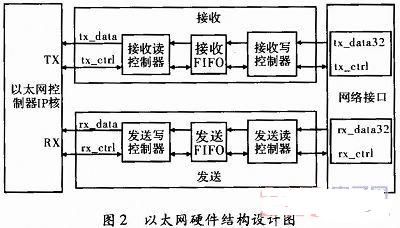

2 以太网接口设计

以太网模块设计主要完成以太网控制器IP核用户端接口协议与多核系统网路通讯协议的转换。以太网接口硬件结构设计如图2所示,以太网控制器IP核为Xilinx公司ISE软件例化生成的千兆网控制器。接收模块完成系统网络数据输出到以太网控制器IP核用户端数据输入的协议转换,发送模块承担以太网控制器用户端数据输出到网路数据输入的协议匹配。网络接口模块为多核系统通讯资源接口。

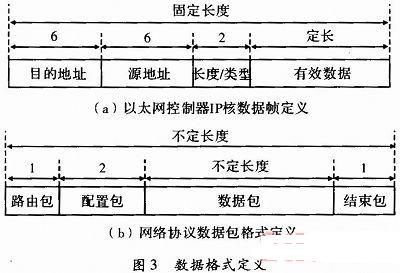

2.1 帧格式定义

图3所示为两种协议的数据格式定义。以太网IP核用户接口数据以帧格式定义数据的输出或输入,数据宽度为8位,帧数据长度范围为64~1 518 Byte,在具体硬件设计中一般选择固定数据长度传输,使硬件结构设计简单。具体格式如图3(a)所示,先输入的数据为目的网卡的网络地址,数据长度为6Byte。其次是6 Byte的源片网络地址。接着为帧传输定义的类型或数据传输长度,长度占2 Byte,数据长度通常在数据帧比较短情况指定。如0010,表示后面传输的16个数据是有效的,传输多余长度的数据,以太网控制器IP核默认为无效数据。而采用类型定义来传输帧,在数据传输长度范围内,结束控制信号以前的数据都表示为有效数据。文中选用512的固定数据传输长度和8 000标识的帧类型完成硬件设计。

网路接口数据包格式如图3(b)所示,数据深度定义为变长,数据宽度为34位,为多核系统实时高效的数据传输提供良好的协调作用。第一个数据为系统网络协议的路由包,其后一个数据为配置信息,称为配置包。接着为不定长度有效数据包。有效数据包发送结束后,紧接着发送一个数据结束包。

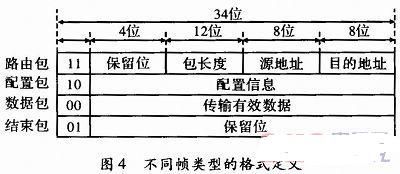

网路数据包中不同包类型的格式定义,具体描述如图4所示,数据高2位标识不同包格式类型。当高2位为11 B时,标识为路由包,其中第28~17位表示传输的数据长度,第16位到第9位定义数据源传播的网络坐标地址,低8位定义为数据通讯的目的网络地址,剩下数据位定义为保留位。当高2位为10B时,标识为配置包,其他位根据通信需求,设置不同配置信息。当高2位为00B时,标识为数据包,剩余位为传输的有效数据信息。当高2位为01B时,标识为结束包,其它位为保留位。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码