针对实时应用的并行与多核性能

实时系统需要快速和可预见的响应,这历来是出了名的实施难题。随着多核处理器的使用,这个困难已经变得越来越大。在本文中,XMOS的市场营销总监Andy Gothard先生概述了XMOS的xCORE多核微控制器系列如何提供了一种方法,为实时系统带来了并发处理的优势……

在处理器中采用多核体系架构的主要原因有两个:要尽量避免持续性的工艺线宽缩小所带来的局限性——实际上是避免摩尔定律的限制——或以一种更有效方法来解决某些类型的问题。在这两种情况下,系统开发人员都不得不应对同样的问题;创建在多个内核上同时运行的软件。

在现实世界中,各种活动不是以线性方式进行的。即使是在诸如工厂生产线这样的经典线性活动中,其他任务也是相伴主要生产流程而发生的;如子系统的组装、轮胎成型并安装在车轮上等等。

计算机已经普遍采取了不同的策略:从早期的实现方法开始,计算机体系架构已迫使开发人员利用单个处理器的线性瓶颈。但是,从20世纪70年代开始,经常有人试图打破这一栉楛。

有些应用自然适合于并行运行;通常是那些个中的大问题可以很容易地分成多个较小任务的情况,这些小任务可以同时得到解决。经典的应用是天气预报或大型物理科学问题。这些类别的问题是由部署了成千上万个相同处理器的大型超级计算机来解决的。

包括现今的智能手机在内的其他应用,都使用了几种不同的处理器,包括传统中央处理单元、图形处理单元、数字信号处理器和专用逻辑。

而最近多核芯片备受人们关注。这些集成了两个或两个以上处理器的单个器件最初被看作是一种可持续获得更多处理能力、同时使用更少功率的方法,并且已被部署在台式电脑以及类似应用中。

虽然制造这些类型的多核芯片在物理上相对简单,但它们也提出了部署方面问题:在台式环境中,现有应用并不是为多个处理器设计的,一般都是一个应用运行在一个独立的内核上,而操作系统也管理为其他核分配其他任务。

用于开发和调试运行在多核器件上的应用的新工具正在不断涌现,但这些仍然不是简单的任务。特别是调试还是很困难,因为在两个或两个以上处理器运行软件的时候,当一个错误发生时,依赖于重新创建一个系统准确状态的许多标准调试技术已不再适用。

在观察嵌入式应用、特别是实时应用的时候,问题就变得更大了。即使是用一个传统单核处理器,也很难开发实时系统。一个特别问题是对一个紧急需求的反应,处理器通常不得不接收一个中断,暂停当前正在处理的、包括存储设置的操作,然后对中断做出反应。这需要时间,但更糟糕的是,它需要的时间并不总是可以预测的。如果有多个处理器,这种不确定性会变得更大。处理器之间的消息传递通常是通过共享的内存,这又是不确定的。

一种不同的体系架构

XMOS的xCORE体系架构是专为解决诸多这类问题而创立:特别是,它设计的目的就是要通过一个并发多核体系架构来解决实时应用的问题。

该体系架构的基础是逻辑内核,这种内核是一个能够以可确保的最低指令速度顺序执行程序的32位处理单元。逻辑内核组合在一起构成了逻辑块(tiles),每个逻辑块可容纳最多达八个内核。而实体器件可包含一个、两个或四个逻辑块。入门级器件xCORE XS1-L4 -64有一个带有四个内核和400 MHz时钟速度的逻辑块。基于硬件的调度器为每个内核分配执行的时间条,所以在这种情况下,每个内核都有100 MIPS的执行速度,或每个周期花10ns来执行任务。这种可预测的执行速率是确定性的核心,所以使xCORE非常适合实时应用。

在一个内核上运行的任务可以是一个更大问题的子集,就像一个大规模并行超级计算机的非常小型版本;或者它们也可以是不同的应用,就像是多应用器件的一个版本。

一个逻辑块上的内核共享内存。当一个内核正在执行一项任务时,它可不使用任何缓存而访问全部内存。这消除了不确定性的另一个可能的来源:任务间的通信和同步不需要软件实时操作系统(RTOS)。取而代之的是包括IN和OUT指令的指令集。IN输入来自一个源的一个数据字,而OUT发送一个数据字。如果两项任务在一个通道上通信,则IN指令被阻止,直到OUT已被执行。通信速度快,而任务可以同步。

I/O引脚是完全可配置的。一组逻辑函数,即xCORE-Port,位于I/O引脚后面,并连接到一个逻辑处理器内核,以便在需要的时候创建外设。在xSOFTip库中提供了多样化的标准外设,包括各种UART、I2C、SPI、USB、以太网、CANbus、LIN和丰富的专业音频接口。由于这些接口是以软件定义的,它们可以自由地被定制:用户也可以创建他们所需要的任意专用接口。

在使用不止一个逻辑块时,无论在同一器件上或另一器件上,通信是通过一种名为xCONNECT的专用高速体系架构实现的。此时,运行在一个逻辑块上的各个内核上的任务可以使用内存来交换数据,它们还可以通过通道来交换数据并同步数据。xCONNECT将通道扩展到其他逻辑块上的内核,无论这些逻辑块是在同一个芯片上或是在其他芯片上,是否在同一个电路板上或者甚至是其他电路板上。

xCONNECT的逻辑机制是一个通过XMOS链路来连接一个交换机网络。从任务的角度来看,它通过一个通道发送一条消息,因为它将与同一逻辑块中的另一个任务通信。在这种情况下,这条消息打开了交换机来来创建一个路由,该路由可在一段通信会话结束时被关闭,或保持打开来运载数据流。一则空的消息可以被用来建立任务之间的同步。典型延时是每跳100 ns,每个链路的带宽可高达400 MBit/s。

这便为扩展一个应用的可用资源提供了一种简单的途径:它很容易增加更大的处理能力、更大的内存和更多的I/O,而不会损失确定性。

当然,xCORE器件采用了XMOS专有的可配置多核微控制器体系架构。但在很宽广的应用范围内,ARM Cortex处理器是被一个巨大的生态系统所使用和支持的领先内核,该生态系统由工具、合作伙伴和软件等成员组成。与此相适应的是,XMOS已经创造了一类全新的低能耗可编程SoC产品,它将xCORE技术与超低功耗ARM Cortex M3处理器结合在一起。xCORE技术支持所需外设精确组合的软件配置,并能以时序精确的执行来支持最严格的硬实时要求。xCORE-XA系列扩展了这些功能,让开发人员可以利用丰富的ARM生态系统,包括可以大大加快产品设计时间的标准代码库。

开发

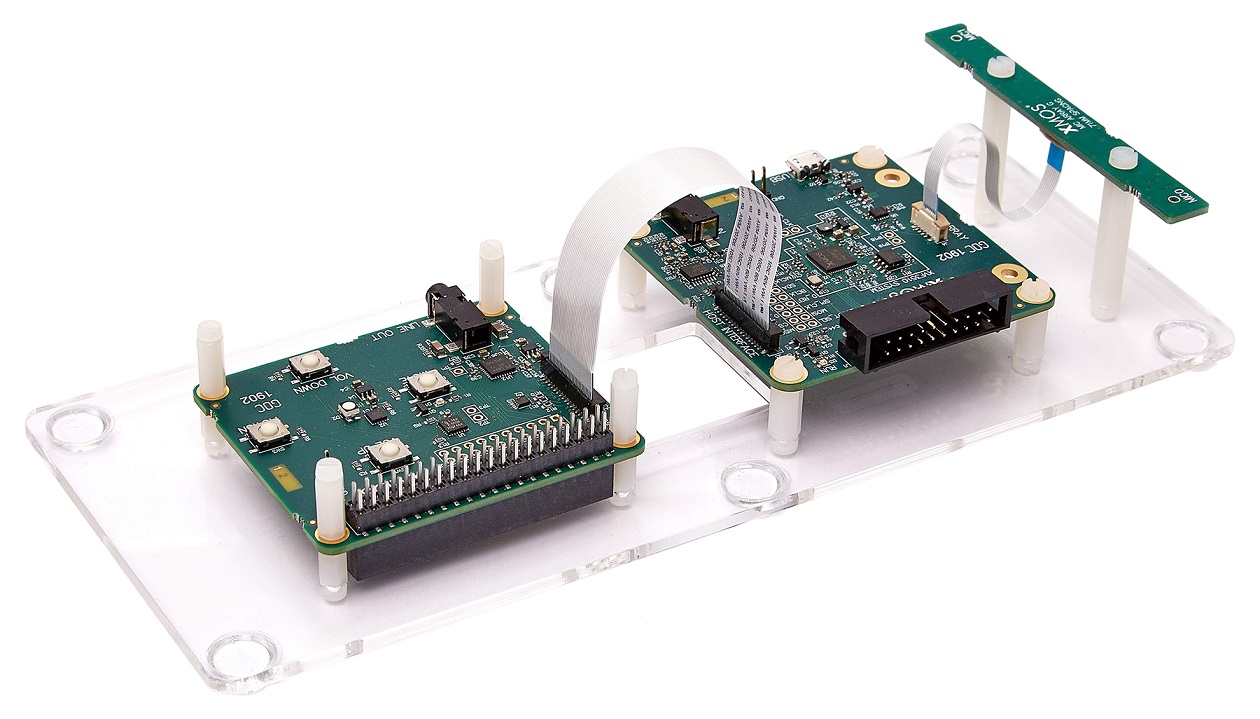

电子产品中许多新进展的致命弱点是缺乏足够的开发工具。从一开始,XMOS就已经把重点放在了提供一流的工具。极为丰富的xCORE系列开发板(sliceKIT)得到了xSOFTip软件外设和xTIMEcomposer Studio开发工具的支持,其中包括一个编译器、调试器、仿真器、静态代码分析仪,以及xSCOPE软件逻辑分析仪。

XMOS时序分析仪(XTA)是一个基于形式化方法的工具,用以确保开发的代码满足应用的时序要求,这对于实时系统至关重要。它可以用来进行二进制代码的分析,以生成在最好和最坏时序情况下的时序路径图形化显示。另外,衍生于系统规范的时序判断可以内置于代码中,XTA将报告这些条件是否已经被满足。

xSIM为xTIMEComposer Studio增加了一个全功能仿真器,而xSCOPE可提供电路中在线调试。xSCOPE的界面类似于一个传统示波器,但它以非常高的性能提供了高级别的信息。与目标系统的USB 2.0连接是通过一个由xCORE提供支持的XTAG调试适配器实现的,它提供了高达1MSPS的数据传输速率。数据也可以存储起来作为一份日后分析用的文件。

对xCORE的编程是在汇编程序中进行的,可以使用C或C++。对于C和C++,一组简单的语言扩展提供了用于描述并行性和并发性的机制。这些还定义了数据流和事件,并可以用于高级脚本。该编译器是基于LLVM项目的开源编译器。

xSOFTip功能单元块被用于I/O和信号处理及协议。它们采用C语言编写而成,并在xCORE上执行,提供了部署灵活性。xSOFTip Explorer是一个图形化接口,它提供了对库的访问,并允许功能单元块被配置为满足某项特定规范。该工具了解一个特定功能单元块的资源需求(如处理器内核数量、I/O引脚、存储器和时钟的资源等),并能为一种实现提供最合适器件预估。

对于调试任务,开源的GNU调试器已经进行了扩展,可与多内核和通道资源一起使用。

xTIMEcomposer Studio是基于Eclipse的开源集成化开发环境(IDE),它可从XMOS网站免费下载。

凭借一种结合了应用灵活性与时序确定性的创新体系架构、一个丰富的开发环境,以及在实际应用中批量部署的良好记录,XMOS正在为实时应用带来并行处理能力。

应用

客户应用1:索尼

索尼公司在其PHA-2便携式耳机放大器中采用了xCORE技术。

PHA-2将多个高保真发烧友级USB接口与一个高解析度DAC以及一个高品质耳机放大器结合在一起,所有东西都集成在一个很小的便携式产品中。它与USB Audio Class 2和DSD(直接数字流编码)技术兼容,为使用索尼Walkman系列便携式音乐播放器、Windows和Mac电脑,以及iPad、iPod和iPhone的收听者提供了更高质量的音频体验。

索尼PHA-2基于XMOS的业界领先的USB音频解决方案,使用了xCORE产品代码为XS1-U8-64的8核多核微控制器。它能够支持采样率高达192kHz和解析度为全24位的音乐文件,可提供录音室品质的数字音频。

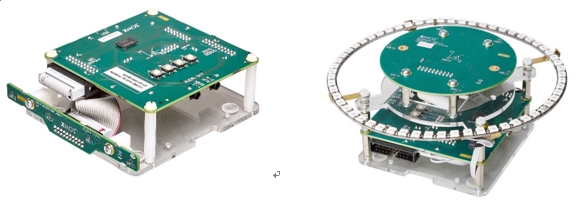

客户应用2:Synapticon

Synapticon为机器人提供嵌入式计算和控制系统。一台机器人的手臂有多个电机,其中每一个通常都有其自己的控制器。这为开发人员在控制这些电机和管理它们之间通信两个方面都带来了挑战。为了解决这个问题,位于斯图加特的Synapticon开发出了一款核心处理器板C22,它基于两个xCORE L16芯片,在一个低功耗30 mm×30 mm电路板上提供了等效于于一个32核处理器的能力。此板减少了元件数量,提供方便而高确定性的控制和通信,并且还可为系统开发提供一种可实现更高级别抽象的方法。

附录:术语

逻辑处理器:每个xCORE逻辑块包含4至8个逻辑处理器,该处理器是一个虚拟32位计算引擎。

端口:xCORE Port是一套轻量级逻辑函数,它们位于I/O引脚后面,并通过连接到一个逻辑处理器内核来创建外设。在xSOFTip库中提供了多样化的外设,包括UART、I2C、SPI、USB、以太网、CANbus和丰富的专业音频接口。

逻辑块:xCORE体系架构的物理子单元,单个芯片带有一个或多个逻辑块。

sliceKIT:sliceKIT将开发板和参考设计组合在一起,并可以结合起来构建各种更复杂的系统。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码