一种基于FPGA的多路数字信号复接系统设计

摘要 数字复分接技术是数字通信网中的一项重要技术,能将若干路低速信号合并为一路高速信号,以提高带宽利用率和数据传输效率。文中在介绍数字复接系统的基础上,采用VHDL对数字复分接系统进行建模设计和实现。并利用乒乓操作和先进先出存储器(FIFO)对复接器进行设计,利用帧同步器对数据进行分接。以QuartusII8.0为仿真软件,对设计进行仿真验证,仿真结果表明,设计实现了复接系统,便于修改电路结构,增强了设计的灵活性,且节约了系统资源。

数字通信系统中,为了提高信道的利用率,使多路信号在同一条信道上传输时互相不产生相干的方式称为多路复用。在时分复用中,将时间划分为若干时隙,各路信号在时间上占用各自的时隙,即多路信号在不同时间内被传送,各路信号在时域中互不重叠。数字复接终端是将若干低速率码流变换成一路高速率码流的设备。应用可编程逻辑门阵列(FPGA)芯片实现复接系统便于修改电路结构,增强了设计的灵活性,并节约了系统资源。

1 多路复接系统设计要求

(1)实现两路数据的同步复接。(2)支路速率为32 kbit·s-1。(3)按位复接。(4)帧同步码字为10 bit:“1 0 1 1 0 1 0 01 1”。(5)帧长128 bit。

2 数字复接系统基本原理

2.1 数字复接系统

数字复接终端的作用是将低速数据码流变换成高速数据码流的设备。将两个或两个以上的支路数字信号按时分复用方式合并成单一的合路数字信号的过程称为数字复接;完成数字复接功能的设备称为数字复接器;在接收端将一路复合数字信号分离成各支路信号的过程称为数字分接。数字复接器、数字分接器和传输传道共同构成了数字复接系统。

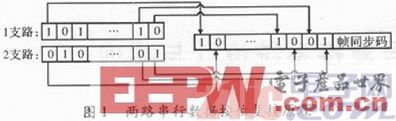

2.2 按位复接

复接的方式有:按位、按字和按帧复接等方式。本文采用按位复接的方法,方法是每次仅依次复接每一个支路的一位码,又称比特复接。复接后的码序列中第一个时隙中的第一位表示第一路的第一位码;第二位表示第二路的第一位码;依此类推,则第n位表示第n路的第一位码。2路串行数据按位复接原理框图如图1所示。

3 数字复接系统的建模与仿真

3.1 复接器总体设计方案

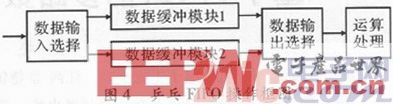

复接器的设计方案如下:首先对两支路串行数据数字信号进行按位复接合成一路信号;用FIFO定义2个128 bit帧格式,帧同步码为10 bit“1011010011”,采用乒乓操作对合路数据每118位依次存储到FIFO中,即将合路数每118位插入一个帧同步码,形成128位的帧。乒乓操作是输入合路数据流通过输入数据选择单元等时地将数据流分配到两个FIFO数据缓冲区。当FIFO缓冲区1写入数据操作时,从FIFO缓冲区2中读取数据操作;当FIFO缓冲区1读数据操作时,FIFO缓冲区2中进行写操作;如此循环,可实现2路数据复接,具体如图2所示。

3.2 复接器关键模块设计

(1)合路模块。合路模块功能是将两路串行数据按位复接成一路数据,合路模块输出的是未接入帧同步码的数据,对于各支路数据输入需使用clksel时钟作为控制。合路输出为y信号,D0、D1是两路串行数据,clksel是两支路控制输出信号。从仿真图3中可看出,其能将D0和D1合成一路信号y输出,仿真结果正确。

(2)乒乓操作FIFO模块。乒乓操作FIFO模块的功能是对合路数据加入帧同步码。乒乓操作FIFO框图如图4所示。乒乓操作处理流程如下:输入数据流通过输入数据选择单元将数据流分配到两个数据缓冲区。在第1个缓冲周期中,将输入的数据流缓存到数据缓冲模块1;在第2个缓冲周期中,通过输入数据选择单元的切换,将输入的数据流缓存到数据缓冲模块2。同时,将数据缓冲模块1缓存的第1个周期的数据通过输出数据选择单元的选择,送到运算处理单元进行处理;在第3个缓冲周期,再次切换数据的进入与输出缓冲模块。

空满信号的产生是设计FIFO的关键之一,本文通过异步的比较读写指针ptr以及读写指针的MSB进行判断,然后产生两个异步的空满标志信号送入读写模块进行同步,最后向外界输出两个同步的空满信号。图5的方框内可看出空判断信号atmpty和满判断信号afull是取反的关系。当一个RAM数据读完时,另一个RAM写满。

图6中input,是M序列伪随机码,“10011101”作为测试信号。可认为M序列伪随机码是由两支路信号合路而得到的信号。从仿真波形可看出,空满判断信号rmsb和wrsb1互为取反关系,满足要求。rptr是读地址信号从FIFO的首地址开始读取数据的。wptr写地址信号是从FIFO的第10个存储单元开始写入数据的,这是因为FIFO的前10个存储单元使用的是做帧同步码“1011010011”。zongshu信号端是随机码加入帧同步码后的输出。

3.3 分接器关键模块设计

图7是分接器的原理框图。定时发生器为帧同步系统提供帧定位标志信号;帧同步系统用来检测所传输数据码流中的帧同步码;比特分接电路则用于将串行数据转换为并行数据。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码