运算放大器--单通道、双通道、四通道优缺点及结构

Bob Widlar曾提出一个重要观点,即集成电路(IC)的设计依据应该是比例和匹配,而不是电阻和晶体管的绝对值。这个原理同样适用于需要多个运算放大器的PCB(印制电路板)设计。

双通道运放真的是两运放,还是一硅片具备两功能?

人们常常认为双通道运放等同于两个单通道运放,但在电路板上,单片双通道IC与两个单通道IC之间还是存在一些细微差别,这些差别可能会给新的设计带来问题。由于两个运放在相同的单个硅片上并排放置,因此在使用双通道放大器时需要考虑电气和散热因素。

业界研究热效应已经有30多年的历史了,并且在Solomon引用的一篇前50强IEEE论文有详细的论述 [1]。随着运放输出电压的改变,散热量也随之改变,会有一个热波穿过整个芯片传播到输入级,使芯片失去平衡,并表现为一种电气信号。热波能够同时影响两个运放,即使它们在电气上是分开的。

另外还有电气效应。为了减小裸片尺寸,进而降低成本,像偏置电路和相关启动电路等部分可能为两个运放所共享。如果一个运放超出了正常工作范围,并导致偏置电路出现故障,那么另一个运放也会发生故障 [2]。另外,由于只有一对电源引脚,邦定线和裸片上的一些金属化层将承载两个运放的总电流。一个放大器吸收的电流将产生IR压降,并通过随频率改变的PSRR指标反映到另一个运放上。

优点

任何事物都不可能十全十美,因此使用双通道运放既有优点也有缺点。有些优点是显而易见的。首先,单次插入比两次插入更省制造成本。其次,大多数半导体制造商的双通道运放报价通常要低于两个单通道运放的成本。通过合并子电路,裸片面积通常小于单通道运放的两倍。再者,高速自动化测试设备(ATE)受类似运放这样的单个功能的处理时间的限制,因此每个功能的测试成本也更低。在封装成本方面也是如此。最后,由于两个电路在晶圆上靠得非常近,它们之间的电气特性 (通常会规定)也非常匹配。

缺点

不过也存在一些缺点。将两个或四个功能放在一个封装中会增加功耗。对于低带宽、低电压(低功耗)运放来说,这种功耗的增加对结温的影响很小,仅上升5℃。而对驱动低阻抗负载(如同轴电缆)的高速运放而言,这种结温上升会非常明显,大概有30℃。由于裸片应力原因,四通道运放的最大失调电压将高于双通道或单通道运放[3]。在某些情况下,双通道运放的失调电压会比单通道运放高,四通道运放的失调电压将比双通道运放高[4]。

串扰也是个问题,它源自两个效应:热效应和电气效应。如前所述,从一个部分发出的热波将使另一个部分的输入级失去平衡,这表现为低频反馈。另外,由于只有一对电源引脚,邦定线电阻对所有部分都是公共的,因此一个部分引起的大负载电流将在邦定线上造成IR压降。运放的PSRR不是无限的,因此某部分将被耦合到其它部分。PSRR随频率升高而下降,因此在约5kHz至10kHz频段可以看到这一现象。

版图设计考虑

为了真正理解这些效应发生的原因,有必要了解单通道、双通道和四通道运放的内部构造输入级电路

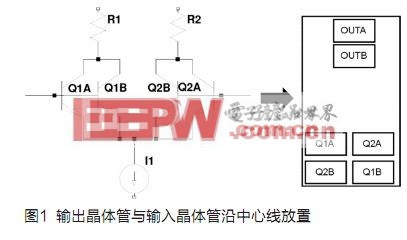

运放的第一级通常是差分对电路,可以是如图所示的NPN或PNP双极性电路,也可以是N沟道或P沟道MOSFET,或N沟道或P沟道JFET。它们面临一个同样的问题:如果两边的温度有差异,即使相差只有1/10,电路也会变得不平衡。当增益为10万倍或以上时,这将对输出电压造成影响。当输出级电路存在功耗时,热波将越过裸片传播到输入级。如果输入级离得比较远(相对而言),等温线将近似平行线。如果两个输入晶体管的位置摆放得比较合适,热波将同时到达两个晶体管,这时平衡几乎不会受到影响。这是一个好主意,但我们可以做得更好。将晶体管分成两个部分,并进行交叉耦合,那么从某个角度传来的热波将同时影响两个部分,影响程度将低于两个独立晶体管的情形。也许George Erdi在 uA725中首次应用的就是这种方法[5]。“交叉耦合四通道”具有多方面的含义,这里讨论的是其最通用的含义。输出晶体管和输入晶体管应沿着图1所示的中心线放置。

关键词: 运算 放大器 单通道、双通道、四通道

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码