同步异步复位与亚稳态可靠性设计

异步复位相比同步复位:

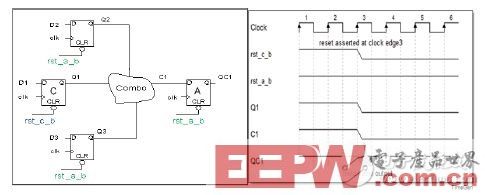

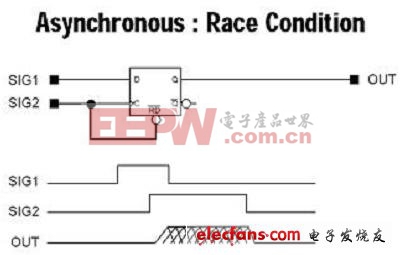

1. 通常情况下(已知复位信号与时钟的关系),最大的缺点在于异步复位导致设计变成了异步时序电路,如果复位信号出现毛刺,将会导致触发器的误动作,影响设计的稳定性。

2. 同时,如果复位信号与时钟关系不确定,将会导致亚稳态情况的出现。下面先给出一个例子,然后就亚稳态进行重点讨论。

亚稳态的定义(说明):

在 Howard Johnson 的《High Speed Digital Design: A Handbook of Black Magic》一书中,专门就逻辑电路的亚稳态作了专门的分析。由于 timing margine 不够,电路的输入没有能够上到所需要的逻辑电平高度,导致逻辑器内部不得不花费额外的时间使得输出达到所需的稳定逻辑状态,这个额外的时间,我们也叫作决断时间(resolution time)。在 Johnson举的例子里,逻辑器件的逻辑电平是用电容来维持的,如果时序不够,就好像给电容充电不足。

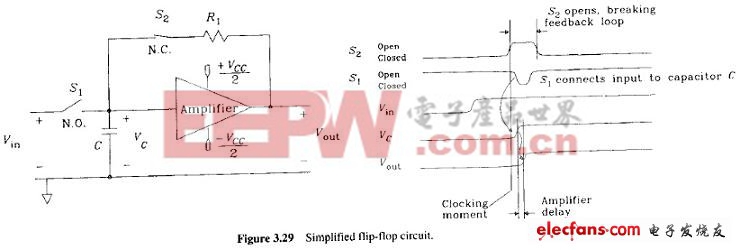

Howard Johnson 在书中(P123 页-3.11.2)用一个 flip-flop 的例子来说明亚稳态(metastable behavior)。

书中用一个 amplifier,两个 switch,一个电容来模拟 flip-flop 的工作状态。电容用来保存电路的逻辑电平,两个 switch 状态的改变可以模拟数据的输入和 flip-flop 的工作状态。在flip-flop开始翻转之前,输入数据的逻辑电平存储在电容里,然后flip-flop通过一个switch S1断开与输入端的连接,同时通过 amplifier(带有一个正反馈环)开始进行内部的翻转机制。

从输入端 switch S1断开,和正反馈环上的 switch S2闭合开始,amplifier 就处于一个幂指数形式的中间态,或者说是不稳定态(形象地说就是“工作中”),可以用如下式子表达:

V(out)=V(in)exp[kt]。

其中 V(in)表示输入逻辑的电平,V(out)表示输出的逻辑电平。k 是一个时间常数,它和 amplifier 的带宽以及正反馈环路有关。

我们看到,如果 flip-flop 在用电容对输入电压采样的时间过短,也就是所谓的时序不够,就会导致 V(in)的值很小,对于 flip-flop 就需要花很长的时间使得输出逻辑 V(out)达到标准电平,也就是说电路处于中间态的时间变长,使得电路“反应”变迟钝。这就是我们所说的“亚稳态”。

从 Johnoson 的一系列试验可以看出,随着 timing margine 不足程度的加深,逻辑电路“反应”会越来越慢,当超过一定的极限时候,逻辑电路就没有输出。

可以说,电路亚稳态的存在,会给时序设计带来很多连锁反应。因此 ,对于高速逻辑电路的设计,充分的 timing margine 是必需的。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码