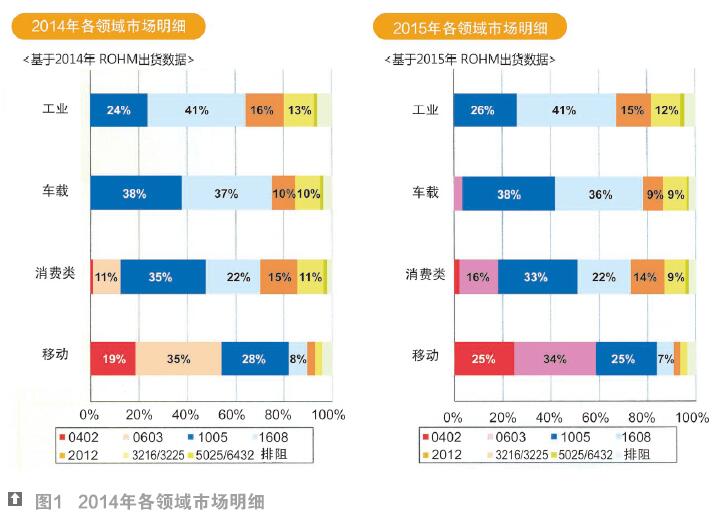

隔离式ADC架构利用分流电阻进行三相电能计量

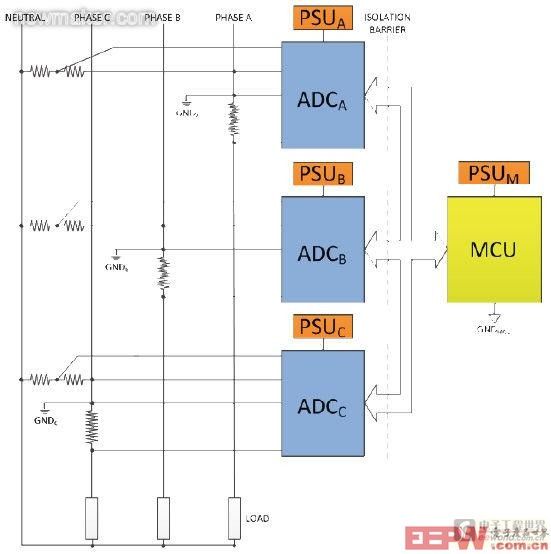

图3. 具有分流电阻、独立电源和隔离通信的三相电表

理想情况下,所有相电流和电压都应同步采样,以便利用瞬时值进行全面的三相分析。但是,各相的ADC读数完全独立,因为不存在ADC同步。这是这种架构的第一个局限。使用电流互感器或罗氏线圈的电表则不存在这种问题,因为它们可以使用一个计量模拟前端(AFE)来同时读取所有相电流和电压。

这种架构的另一个问题是高器件数:一个MCU、三个ADC、三个多通道数据隔离器以及四个电源。使用CT的电表不存在这个问题,因为电路板通常具有一个MCU、一个计量AFE和一个电源。

那么,如何构建一款具有分流电阻的优势,器件数对于这种架构而言最少(即一个MCU、一个电源和三个ADC),并且能对所有相电流和电压同步采样的电表呢?

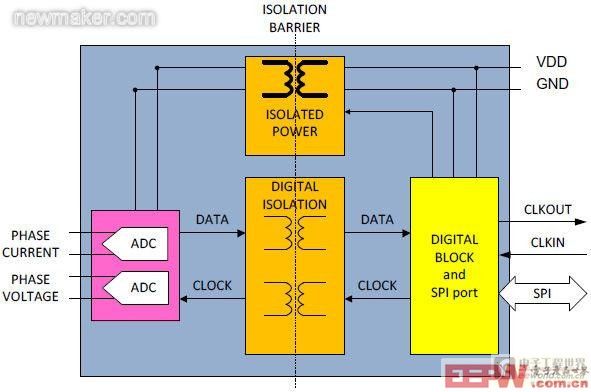

隔离式ADC架构

答案是构建一种集成至少两个ADC、一个隔离式DC-DC转换器和数据隔离器,并能使属于不同芯片的ADC同步采样数据的芯片(图4)。MCU的电源VDD也为此芯片供电。采用芯片级变压器技术的隔离式DC-DC转换器为ADC的第一级提供隔离电源。一个ADC检测分流电阻上的电压,另一个ADC利用分压器检测相至零线电压。由分流电阻极点之一所确定的地就是芯片隔离侧的地。ADC为sigma-delta型,仅第一级放在芯片的隔离侧。第一级输出的位流经过芯片级变压器,后者是隔离数据通信通道的一部分。芯片的非隔离侧收到位流,滤波后将其变为24位字,然后通过SPI串行端口提供给外部。

芯片级变压器技术对这种新型ADC架构的贡献最大。与光耦合器相比,ADI公司获得专利的iCoupler数字隔离器更可靠、尺寸更小、功耗更低、通信速度更快、时序精度更佳。但这还不够。隔离式sigma-delta调制器上市已久,采用光耦合器或芯片级变压器。芯片级变压器技术的最重要贡献是伴随isoPower隔离式DC-DC转换器,它可以与ADC、数字模块、隔离数据通道一同集成到一个表贴薄型封装中。

图4. 新型ADC架构包括双通道ADC、数据隔离和一个隔离式DC-DC转换器

信息利用极高频PWM脉冲传输到隔离栅另一侧。由此产生的高频电流会在电路板中传播,引起边沿和偶极子辐射。隔离式DC-DC转换器的负载仅由sigma-delta ADC的第一级构成,其幅度是已知的。因此,线圈是针对已知负载进行设计,从而可以降低一般与DC-DC转换器相关的辐射,并且无需四层电路板。使用这种架构的IC时,电表制造商可以使用两层电路板,并通过所需的CISPR 22 Class B标准。

为使与MCU的接口尽可能简单,芯片的数字模块对来自第一级的位流进行滤波,并通过简单的从机SPI串行端口提供24位ADC输出。电表每一相都有一个隔离式ADC,因此获得一致ADC输出的挑战仍未解决。如果采用同一时钟工作,则所有相上的ADC第一级可以在同一时刻采样。如果图4中的CLKIN信号产生自MCU,则这很容易实现。另一个方案是使用一个晶振为一个芯片产生时钟,然后利用缓冲CLKOUT信号为所有其它隔离式ADC提供时钟。控制所有隔离式ADC以在同一时刻产生ADC输出。现在,电表就能利用分流电阻检测电流,执行精确、全面的三相分析。

图5显示一款采用三个隔离式ADC的三相电表。该电表仅有一个电源为MCU和隔离式ADC供电。MCU利用SPI接口从各IC读取ADC输出。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码