基于AXIe中PCIe高带宽及多模块同步数据传输的高速图形传输系统

通道间时钟偏移 (Channel-to-channel skew)

E-Beam 系统的硬件设计可确保通道间的时钟偏移最大不超过 2ns。自外部同步信号产生器开始,低偏移扇形输出缓冲器(fan-out buffer)即用于外部同步信号产生器之中,做为将工作频率及同步信号分配到各机箱切换模块的用途。另外,切换模块除提供 PCIe总线自动切换功能外,也负责切换 STRIG、SYNC及相关频率信号,将这些同步信号分配到各插槽上的数据传输模块。在数据传输模块方面,除特别注意各频率及数据信号在PCB上布线都须使用相等路径长度外,在电路输出部分也都采用低偏移缓冲器。最后处理过的数据会由Avago 平行光纤发射器 (AFB-810BHZ-TX) 输出。综合考虑 FPGA 内部绕线及制程、光纤、连接器及 PCB 路径等因素后,计算所得的总体通道间时钟偏移可小于 1ns 以下。

高带宽图形传输

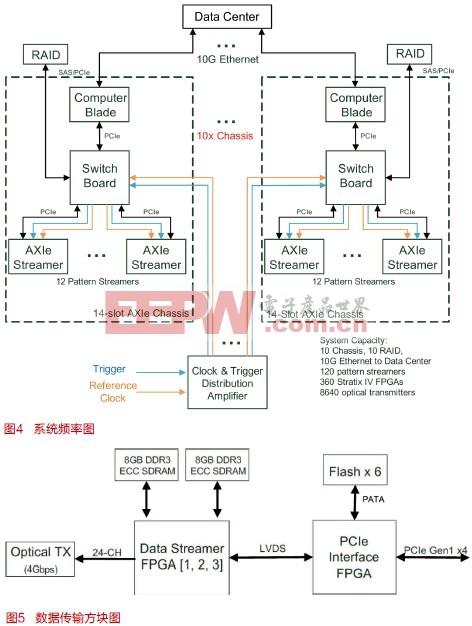

除了跨 10 个机箱下严格的通道间歪斜的要求之外,系统还要求能够实时传输大量数据到光纤输出通道。各图形传输模块配备四组高性能的 FPGA;一颗负责PCIe驱动接口,另外三颗各负责 24 个光纤通道的驱动接口,即单一数据传输模块可提供 72 个光纤输出通道。

集成电路图案数据先自 RAID 磁盘阵列读出后加载主板刀锋服务器的内存,再经由PCIe 总线做直接内存存取(DMA, direct memory access)传输到个别的数据传输模块。数据传输模块上的 PCIe FPGA 接收 DMA 数据并存入模块上的闪存,然后再传输到各图形传输 FPGA 对应的 DDR3 内存储存。图形传输 FPGA 内建有客户自定的解压缩算法,解压缩后的数据会通过光学发射器做同步数据输出。示意图请参见图 5。

其中DDR3 内存切割为两个区块,以便实现「乒乓(ping-pong)」技术,也就是可让大量数据同时间进出内存以优化读/写带宽。各光纤输出通道的图形档案大小可达 300MB,换句话说,一个插满12张数据传输模块的机箱总共会需约260GB的档案大小。

先前提到符合经济效益的产出标准为每6分钟要完成一片晶圆,所以整体上会需要至少725MB/秒的连续数据带宽,通过这样的运作模式,另一组完全不同的晶圆电路图文件,也可在前片晶圆制作完成前可完成下载,以实现少量多样的高性能产出。

总结

凌华科技基于FPGA架构的AXIe 图形传输系统,对于无光罩 E-Beam 微影制程应用,提供高效率集成电路图形数据处理、传输,以及数据同步的解决方案,整体系统跨通道间时钟偏移低于 2ns,且应用AXIe的几项特色,包含可提供大功率电源、有效散热及高可靠度及扩充性,可符合实际半导体生产制程的需求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码