ISE入门三部曲

此时我们可以查看RTL级的原理图,双击 View RTL Schematic,并选择Start With a schematic of the top-level block,点击OK如图13所示,然后将出现一个模块,上面有我们写的输入输出。

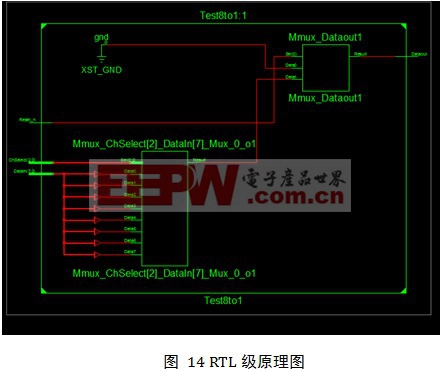

双击模块,将出现如图14所示的原理图,查看原理图,可以查看原理图是否与自己的设计一致,利于检查连线错误等。如果逻辑比较简单,查看原理图即可知道设计的目标是否达到,例如本例中的8路选择器,从综合生成的原理图可以看出,正常情况(Reset_n信号无效)是一个8路选择器,复位时输出为零;当逻辑比较复杂时,原理图庞大,无法仔细去比对是否达到自己的目的,此时就需要进行软件仿真。

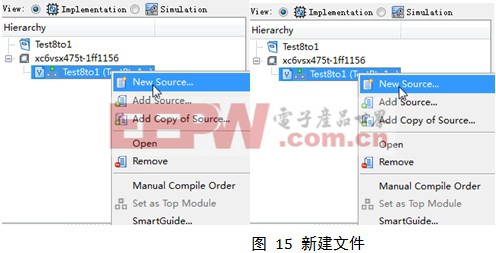

那么我们首先编写TestBench程序,点击菜单栏的Project(或者右键单击到工程的文件),NewSource 选择 Verilog Test Fixture,输入文件名TestModule ,点击Next,选择要关联的源文件,这里只有一个源文件 Test8to1,如果有多个源文件,则需选择对应的需要仿真的文件,然后点击Next。

关键词: ISE 8路选择器 Verilog 工程建立 入门 常见错误

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码