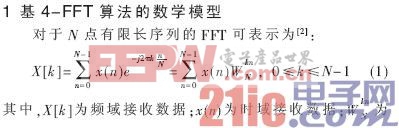

基于FPGA的可配置FFT_IFFT处理器的设计与实现

目前,正交频分复用OFDM(Orthogonal Frequency Division Multiplexing)技术已经成为未来宽带无线接入系统的基本实现技术之一,其抗多径衰落和高频带利用率的优点被广泛应用于无线通信系统中,是解决高速数据在无线信道中传输的首选方案[1]。

式(4) 表明首先对X[k] 取共轭, 然后对其进行FFT变换, 对其结果再取一次共轭, 乘因子1/N, 这样就实现了IFFT 与FFT 处理模块的复用。

2 可配置FFT/IFFT 处理器设计

2.1 FFT/IFFT 处理器整体结构

可配置FFT/IFFT 处理器整体结构如图1 所示。图中, 基4 蝶形单元主要完成输入的4 路并行计算。OFDM数字基带数据流需要高速连续处理[3], 故FFT 处理系统在输入、输出均采用了乒乓处理, 共需要4 组存储单元,一组存储单元需要4 块RAM;RAM 地址产生单元主要

生成存储单元写入及读出数据的地址, 数据选择模块主要完成了乒乓操作RAM 的数据选择;ROM 及其地址产生单元主要在控制单元的控制下将旋转因子送入蝶形单元, 配置单元控制不同点数的数据流操作及其相应地址配置。

FFT_IFFT处理器是OFDM系统中数据处理的核心单元,是OFDM系统中数据正交调制和解调的关键。本文设计实现了一种用于P2P移动无线通信手持终端产品,采用单碟形4路并行结构,兼容802.11g协议,可配置FFT_IFFT处理器,在处理速度、实现面积、功耗方面均满足802.11g系统及手持移动无线通信终端的要求。

2.2 FFT/IFFT可配置方案

由基4算法分析可知,要分别完成1 024、256、64点的FFT计算,需要的迭代级数分别为5、4、3级。由于1 024点的FFT运算可分解为4个256点的FFT运算,而256点的FFT运算又可分为4个64点的FFT运算,64点的FFT运算经过3级迭代就可求出。可以通过简单的模式控制实现多点数的配置,如图2所示。其中5级蝶形计算单元,每级蝶形单元结构一致,采用顺序蝶形计算,当选择模式0时,数据直接送入第一级,进行1 024点的5级运算;选择模式1时,数据通过选择器跳过第1级,数据送入第2级,从而完成256点的4级迭代运算;选择模式2时,数据通过选择器跳过第1级和第2级,数据送入第3级,从而完成64点的三级迭代运算。这样就可以正确简单地实现系统要求的配置要求。

2.3 基本蝶形运算单元设计

蝶形运算单元的设计是整个FFT/IFFT处理器设计的关键。完成蝶形运算的一次复数乘法包含4次实数乘法和2次实数加、减法,如果将乘数扩大1位,可将计算化简为3次实数乘和5次实数加/减法。为了提高处理速度,本设计采用四级流水线处理方式,有效地减小了关键路径时延。蝶形单元的数据从RAM输入及输出到RAM需要2个时钟周期,这里引入2级流水;对输入数据的实部和虚部分开并行计算,一次复数乘法只需3个乘法累加器即可完成,用4个加法器及4个减法器即可完成基4蝶形单元后续数据处理,再次引入二级流水。整个蝶形单元处理时间为4个周期,采用四级流水线结构后,以较小的资源代价有效提高了处理器的时钟频率。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码