全功能SPI接口的设计与实现

摘要:SPI(Serial Peripheral Interface,串行外围接口)是Motorola公司提出的外围接口协议,它采用一个串行、同步、全双工的通信方式,解决了微处理器和外设之间的串行通信问题,并且可以和多个外设直接通信,具有配置灵活,结构简单等优点。根据全功能SPI总线的特点,设计的SPI接口可以最大发送和接收16位数据;在主模式和从模式下SPI模块的时钟频率最大可以达到系统时钟的1/4,并且在主模式下可以提供具有四种不同相位和极性的时钟供从模块选择;可以同时进行发送和接收操作,拥有中断标志位和溢出中断标志位。

关键词:全功能SPI;时钟极性和相位;串行通信;微处理器;中断控制

SPI串行通信接口是一种常用的标准接口,由于其使用简单方便且节省系统资源,很多芯片都支持该接口,应用相当广泛。但是现有文献和设计多数仅实现了SPI接口的基本发送和接收功能,对SPI接口的时序控制没有进行深入的研究。全功能SPI接口应具有四种不同的时钟模式,以适应具有不同时序要求的从控制器。文中主要研究SPI接口的时钟时序,并用具体电路实现具有4种不同极性和相位的时钟,最后通过仿真验证和FPGA验证。

1 SPI控制器典型结构

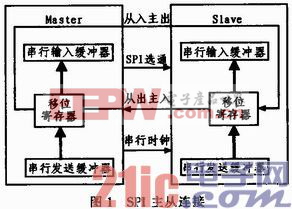

SPI模块中的典型结构是用于通信的主从2个控制器之间的连接,如图1所示。由串行时钟线(SPICLK)、主机输入从机输出线(SPISOMI)、主机输出从机输入线(SPISIMO)、SPl选通线(SPSTE)4条线组成。当CPU通过译码向主控制器写入要传输的数据时,主控制器通过串行时钟线来启动数据传输,将会在串行时钟线的一个边沿将数据移出移位寄存器,而在串行时钟的另一个边沿将数据锁存在移位寄存器中。SPI选通线是SPI控制器的使能端,可以选择多个从机,实现一主多从的结构,只要SPI选通信号将要选的从机处的选通信号变为低电平就能够连接成功。

2 全功能SPI控制器设计

2.1 SPI控制器内部结构

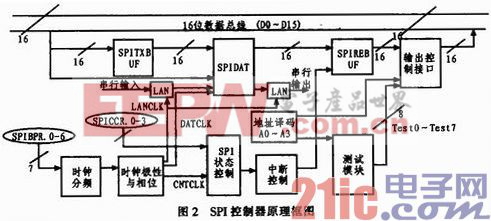

SPI控制器的原理框图如图2所示,其中主要包括:

1)SPI控制器的内部寄存器

SPI操作控制寄存器(SPICTL),SPI状态寄存器(SPISTS),SPI波特率设计寄存器(SPIBRR),SPI接收缓冲寄存器(SPIRXBUF),SPI发送缓冲寄存器(SPITXBUF),SPI串行数据寄存器(SPIDAT),SPI中断优先级控制寄存器(SPIPRI)。

2)SPI控制器内的功能模块

时钟分频模块(Frequency Divider),内部时钟产生电路(Clk_Occur),状态控制机(Srate Control),中断控制(IntContro1),测试模块(Test),输出控制模块(Dateout Control)。

2.2 SPI控制器工作原理

图2给出了SPI控制器的基本原理框图。SPI控制器可工作在主模式和从模式下,由于在主模式下需要提供相应的时钟给从控制器,较从模式下工作更为复杂,所以将用工作在主模式下的SPI控制器描述内部工作原理。

在开始传送数据前,需将SPI控制器进行配置,设定时钟波特率(SPIBPR),时钟相位和极性,需要传送的字符位数(SPICCR)。基本配置结束后,向SPITXBUF和SPIDAT2个寄存器内写入要传送的数据时,将会起动一次发送和接收操作。如果有正在传送的数据,向SPITXBUF内写入数据,新的数据将在当前数据传送结束后自动进行发送和接收操作。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码