基于微处理器的嵌入式配置模式

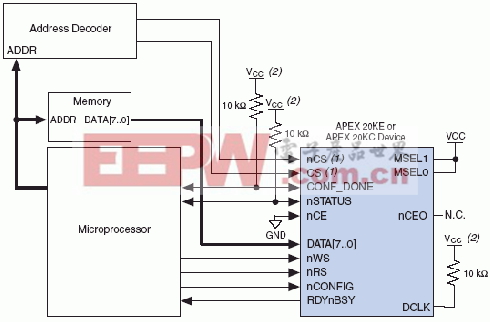

图 3 使用微处理器的被动并行异步配置电路

3 被动并行异步配置

如同被动串行配置一样,被动并行异步配置也包括三个阶段:复位、配置和初始化。被动并行异步配置电路图如图3所示。当nSTATUS或者nCONFIG为低电平时,器件处于复位状态。微处理器在nCONFIG管脚产生一个由低到高的跳变启动FPGA的配置。当nCONFIG变高后,器件脱离复位状态,并且释放漏极开路的nSTATUS管脚,FPGA准备接收配置数据,配置阶段开始。在配置阶段,微处理器FPGA当作存储器,进行写操作,即微处理器先使片选有效,然后把8比特数据送到Data[0:7]管脚上,并配置管脚RDYnBSY到低电平,表示FPGA正忙于处理配置数据,微处理器可执行其它功能。在RDYnBSY低电平期间,FPGA使用内部振荡器时钟处理配置数据。当FPGA准备接收下一字节的配置数据时,它驱动RDYnBSY到高电平。微处理器检测到这一高电平,便送下一字节数据到配置管脚。为了节省一根用来检测RDYnBSY的I/O线,可采用读存储器的方法读FPGA,其中nRS为存储器读信号,在nRS有效期间,RDYnBSY信号被送到数据线D7上。也可以不检测RDYnBSY,也不读FPGA,简单地等待延时tBUSY(max)+tRDY2WS+tW2SB之后就写下一个配置数据字节。FPGA每处理一字节配置数据后,若发现错误就会将nSTATUS拉低,暗示配置出错。微处理器可以检测这一错误,并重新进行配置。如同被动串行配置一样,FPGA在正确接收所有配置数据后,将释放CONF_DONE信号,于是该管脚被外部上拉电阻拉高,表示配置结束,初始化开始。

4 配置数据文件的生成

Altera的MAX+PLUS II或Quartus II开发工具可以生成多种格式的配置文件,用于不同配置方法。不同目标器件,配置数据的大小不同。配置文件的大小一般由二进制文件(扩展名为.rbf)决定。Altera提供的软件工具不自动生成.rbf文件,需要按照下面的步骤生成:①在MAX+PLUS II编译状态,选择文件菜单中的变换SRAM目标文件命令;②在变换SRAM目标文件对话框,指定要转换的文件并且选择输出文件格式为.rbf(Sequential),然后予以确定。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码