基于Avalon总线接口的UPFC控制器IP核设计

3 系统验证

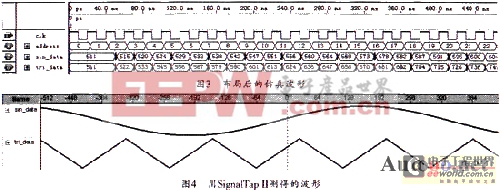

使用Quartus5.1对UPFC控制器IP核的Verilog程序进行综合时,可选用Altera公司的CycloneIIEP2C35评估板。该板有33216个逻辑单元,105个M4k存储模块,35个18×18乘法单元,4个PLL和475个I/O脚。UPFC控制器IP核在Quartus 中编译通过,即可利用波形编辑器对其进行功能仿真。图3是其功能仿真波形。实际上,Quartus提供有嵌入式逻辑分析仪SignalTap II,可以对输出信号进行实时测试。在实际监测中,通过SignalTap II可将测得的样本信号暂存于目标器件的嵌入式RAM中,然后通过器件的JTAG端口和USB Blaster下载线将采得的信息传出,并送入主机进行分析。图4为UPFC控制器IP核输出的实际波形图。

4 结束语

本UPFC控制器IP能使输出正弦波频率跟电网频率保持一致,且输出正弦波的幅值和相位可根据需要进行调节;输出的三角载波的频率、幅值和相位保持不变。同时,将UPFC控制器IP核和Nios II相结合还可提高系统的抗干扰能力。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码