40纳米500MHz DSP核心的时钟设计与分析

4) 计算同级延时,

ESi,corner=Di,corner/ESDcorner

5) 理想上,每个接收端应可跨角点地拥有同等的级数,例如,对于接收端j,

ESj,corner1=ESj,corner2=…

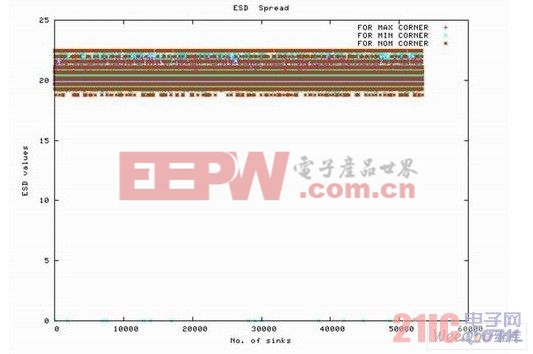

图6和图7所展示的例子是相同级数以及两种实现方式的扩展。在图6中,ESD扩展拥有从18到23的一种更好分布。在图7中,微捷码自带CTS结果显示了从27到37的一种分布。

图6使用新时钟设计方法的 ESD扩展

图7使用微捷码自带CTS的ESD扩展

新时钟设计方法已经实施于40纳米DSP核心。事实证明,使用这种方法的CTS单元门数要比使用微捷码自带CTS工具的少了17%。鲁棒性低偏斜时钟树分布现已成功实现。实验结果显示,新设计方法在降低保持缓冲器门数方面可起到很好效果。同时这种设计方法还可用于H-tree时钟结构。未来工作中,我们还将部署更多分析来改善功耗。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码