基于FPGA的双模前置小数分频器的设计简介

频率合成技术是现代通讯系统的重要组成部分,他将一个高稳定和高准确度的基准频率,经过四则运算,产生同样稳定度和基准度的频率。分频器是集成电路中最基础也是最常用的电路。整数分频器的实现比较简单,可采用标准的计数器或可编程逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。本文利用VerilogHDL硬件描述语言的设计方式,通过ModelSimSE开发软件进行仿真,设计基于FPGA的双模前置小数分频器。随着超大规模集成电路的发展,利用FPGA小数分频合成技术解决了单环数字频率合成器中高鉴相频率与小频间隔之间的矛盾。

1 双模前置小数分频原理

小数分频器的实现方法很多,但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为K的小数分频,K可表示为:![]()

式中:n,N,X均为正整数;n为到X的位数,即K有n位小数。另一方面,分频比又可以写成:![]()

式中:M为分频器输入脉冲数;P为输出脉冲数。![]()

令P=10n,则:![]()

以上是小数分频器的一种实现方法,即在进行10n次N分频时,设法多输入X个脉冲。

2 电路组成

每个周期分频N+10-n.X,其电路双模前置小数分频器电路由÷N/N+1双模分频器、控制计数器和控制逻辑3部分组成。当a点电平为1时,进行÷N分频;当a点电平为0时进行÷N+1分频。适当设计控制逻辑,使在10n个分频周期中分频器有X次进行÷N+1分频,这样,当从fo输出10n个脉冲时,在fi处输入了X.(N+1)+(10n-X).N个脉冲,也就是10n.N+X个脉冲,其原理如图1所示。

3 小数分频器的Verilog-HDL设计

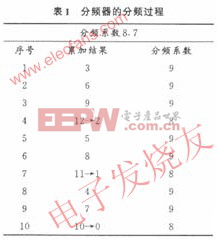

现通过设计一个分频系数为8.7的分频器来给出使用VerilogHDL语言设计数字逻辑电路的一般设计方法。这里使用÷8/9双模前置分频器,按照前面的分析,可以通过计数器计数先做3次8分频,后做7次9分频,即可得到平均分频系数8.7。由于从N分频切换到N+1分频和从N+1分频切换到N分频都会产生一个随时间增长的相位移,如果简单的先进行3次8分频后做7次9分频将会产生很大的相位波动。考虑到该小数分频器要进行多次8分频和9分频,那么就设法将两种分频混合均匀,这种“均匀”工作是通过计数器来完成的,在这里只讨论一位小数的情况,下面简要介绍这种混合的方法:

每进行一次分频,计数值为10减去分频系数的小数部分,各次计数值累加。若累加结果小于10,则进行N+1分频,若大于10或等于10,则进行N分频。该例中计数值为(10-7)=3,前3次累加结果都小于10,所以为9分频,第四次累加结果为12,则去掉十位数后累加结果变为2,同时进行8分频,表1给出了该分频器的分频过程。

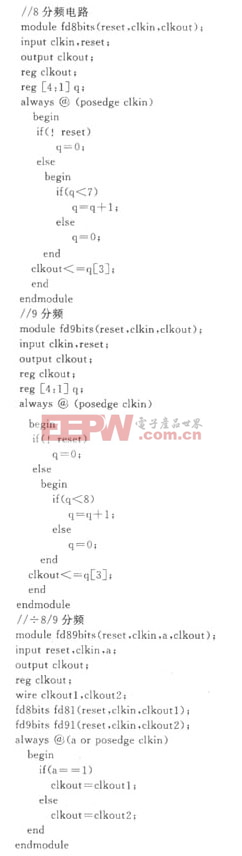

若分频系数后为两位小数,则用100减去分频系数的小数部分。用VerilogHDL设计÷8/9双模前置分频器的描述程序如下:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码