通信领域采用FPGA芯片嵌入式系统分析方案

2.3.2 Slave SelectMap 模式的配置流程

Slave SelectMap 模式下提供时钟的是外部器件,本方案中的液晶拼接屏幕时钟信号是CCLK 使用ARM 芯片的通用IO 进行模拟。同时,该模式下数据管脚有8 个,因此在每个CCLK 的上 升沿,FPGA 可以读入1 个字节的数据。需要注意的是这1 字节的最高位是D0,而不是一 般微处理器默认的D7,在电路板布线和编写配置程序时应给予相应改变。

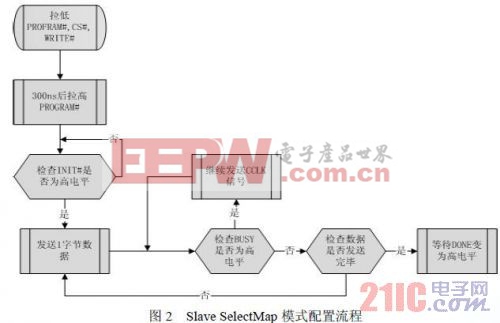

配置过程的具体流程如图2 所示。

接收完配置数据后,DONE 管脚会被拉高。但这并不是表示配置过程已经结束,系统仍 需要时钟来进行后续的上电启动工作。为保证上电配置过程的正确进行,最好的办法是将配 置文件中的所有数据写入FPGA 中之后,然后继续输出CCLK 信号,直到DONE 管脚被拉高。之后,再输出8 个周期的CCLK,保证配置能正常完成。

根据上述流程,配置程序的主要函数的伪码如下。

1.初始化函数SelectMAP_Init,在其它函数之前运行。

SelectMAP_Init(){

将ARM 通用IO 设置为对应的SelectMap 管脚信号;

设置 PROGRAM#,CS#和WRITE#管脚为低电平;

延时至少300ns;

设置 PROGRAM#为高电平;

循环检查INIT#是否变为高电平;

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码