高加速度条件下的时钟源管理设计

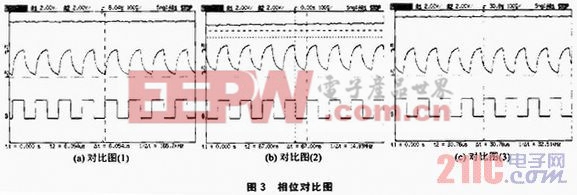

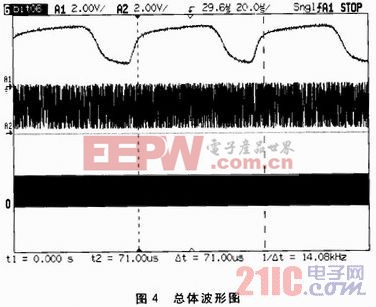

图2为晶振的模拟通道和数字通道的对比图。图3为在频率合成图幅值是![]() 之间硅振荡器和晶振的相位对比图。图4为总体波形图,包括频率合成图、硅振荡器输出图和晶振的逻辑分析输出图。

之间硅振荡器和晶振的相位对比图。图4为总体波形图,包括频率合成图、硅振荡器输出图和晶振的逻辑分析输出图。

从图3中可以清晰地看出,在范围之内相位差是比较小的,上升沿的转换是可以一致的。而在范围之外相位差就比较大了,上升沿与下降沿相对应,转换会有跳变,不能实现平稳转换。通过平稳转换电路实现的转换跳变不明显,示波器上没有明显的跳变反应。

4 结论

通过实验得出的波形与理论相符,在平稳转换条件下能够实现稳定转换,这为下一步在高加速度条件下实现时钟的精度校准提供了可行依据,也为其他的诸如单片机芯片不同频率下的转换提供了实验依据和简易方法。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码