适用于WLAN IEEE80211a标准的双模前置分频器设计

1 电路设计

1.1 电路总体架构

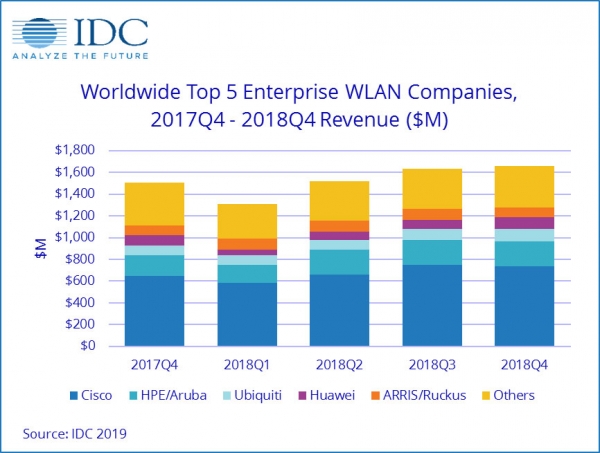

双模前置分频器的基本结构如图1所示,包括三个部分:同步2/3分频器,由异步除2分频器构成的分频器链,以及反馈部分。控制信号MC控制分频比,当MC=1时为32分频,当MC=O时为33分频。

图l双模前置分频器结构图

本设计基于上述传统结构,通过减少高频同步分频器单元中MOS管的个数,达到降低功耗的目的。

1.2 同步分频器设计

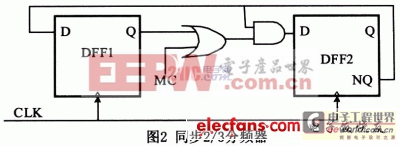

同步2/3分频器的结构框图如图2所示,它是整个分频器工作频率最高的部分,亦是决定前置分频器速度和功耗的关键部分。

MC为逻辑高电平时,电路实现2分频;MC为逻辑低电平时,电路实现3分频。采用同步2/3分频器,大大减少了工作在高频部分MOS管的数目,从而同步部分的功耗有所下降。同时将“与”门设计在D触发器中。这种集成“与”门的触发器不但简化了电路设计,而且避免了单独设计逻辑门所带来的寄生参数的影响,减少了速度损失,从而很好地缓解了工作速度和功耗之间的矛盾。

1.3 优化功耗

从以上的分析可以看出,电路最大的功耗来自同步2/3分频器,但无论是同步2/3分频器还是异步分频器链都必须采用D触发器,因此设计好高速低功耗的D触发器是影响整个分频器速度和功耗的关键。

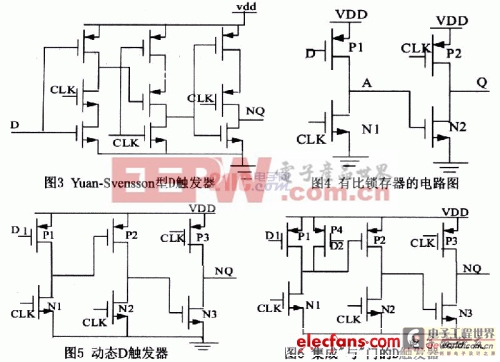

图3为常用的Yuan-Svensson型D触发器(下降沿触发),这种电路采用动态CMOS技术,从左至右由一个N-C2MOS级,一个P- PrechargeCMOS级和一个P-C2MOS级组成。相对于传统的静态分频器,它的各项性能已经有了明显的改善,但是由于大多数MOS管既是前级的负载管又是后级的驱动管,每一级三个MOS管叠加带来了大的RC延迟,所以就算减小其尺寸也不能提高速度。为此我们对图3中的C2MOS电路进行改进,用钟控伪PMOS反相器代替N-C2MOS,这样MOS管的数目、负载电容都有减小。同样用钟控伪NMOS反相器代替PC2MOS,构成图4所示的动态有比锁存器,当时钟信号为低(高)电平时锁存器工作在求值(保持)模式,与Yuan-Svensson结构的D触发器相比具有更低的RC,因此减小了功耗和传输延迟。

需要注意的是,当图4的锁存器工作在求值模式时(CLK为低电平),如果此时输入信号D由高电平向低电平变化,则输出Q的状态发生翻转,导致误操作。于是需要在锁存器的输入端加上一级时钟伪PMOS,如图5,以防止图4所示的锁存器工作在求值模式时输入端D电压发生由高到低的翻转,保证锁存器的输出在单个周期仅可以改变一次。图5即为本文采用的负边沿触发的动态D触发器,相比于图3所示的YuanSvensson D触发器,动态D触发器的晶体管数目减少了三个,增强了时钟的驱动能力,不仅提高了电路的工作频率,而且大大降低了功耗。同时将“与 ”门集成到DFF中去,如图6所示。仿真结果表明这种集成“与”门的D触发器工作速度有一定提高,同时也降低了电路的功耗。在同步2/3分频器中,DFFl采用的是不带“与”门的D触发器,DFF2采用带“与”门的触发器。

1.4 异步除2分频器

经过同步2/3分频器分频后,信号的频率已经降低。由于方波驱动较长分频链时,可能引起模块内部某点的高电平陷落,从而造成整个电路的逻辑混乱。由于同步分频器中D触发器的NQ端输出的高电平不稳定,可以通过在Q端添加缓冲器予以解决。仿真结果表明,用该触发器组成的异步链可在速度、频率和功耗间达到很好的折衷。

2 电路的调试与仿真

调试时,首先要确定P1管与Nl管的宽长比(W/L)以保证时钟为高电平时,图4所示的锁存器N2管总保持在关断状态,电路处于保持模式,因而输出 O点的电压保持不变。当时钟从高变为低时,锁存器进入求值模式,此时如果输入D为低电平,这时N2管和P2管都导通,要求P2管的上拉能力比N2的下拉能力弱,以保证Q点输出VOLQ比下一级门电路的输入电压VIL低,即输出在低电平范围内。

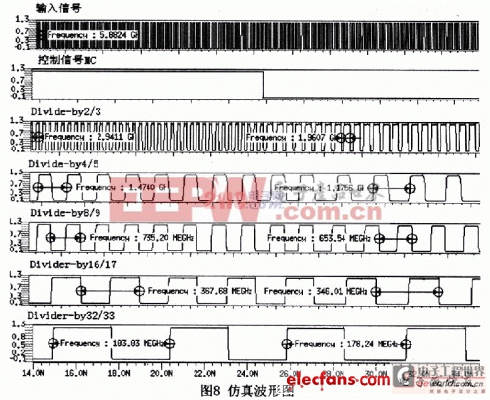

采用TSMC90nm CMOS工艺,电源电压1.2V,使用Mentor公司的Eldo软件对本设计进行仿真,仿真结果显示,输入频率为5.8GHzH寸,电路功耗仅为O.8mW。

3 结论

对于一个双模前置分频器来说,工作的速度(输入信号的频率)和功耗是其性能最重要的两个参数,本文采用动态有比D触发器的结构,相比于传统的 Yuan-SvenssonTSPC D触发器,MOS管的数目减少了3个,这个对于VLSI来说将大大提高了其集成度,因此有着更好的工作频率和更低的功耗。并在此基础上设计了一个前置分频器。完全覆盖了WLAN IEEE802.11a通信标准的所有频段。采用TSMC90nmCMOS工艺,电源电压1.2V,运用Mentor公司的Elod软件对本设计进行仿真,电路工作在5.8GHz时功耗仅为0.8mW。电路最高工作频率可达到6.25GHz。

关键词: WLAN IEEE80211a 双模 分频器

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码