浮点LMS算法的FPGA实现

引言

LMS(最小均方)算法因其收敛速度快及算法实现简单等特点在自适应滤波器、自适应天线阵技术等领域得到了十分广泛的应用。为了发挥算法的最佳性能,必须采用具有大动态范围及运算精度的浮点运算,而浮点运算的运算步骤远比定点运算繁琐,运算速度慢且所需硬件资源大大增加,因此基于浮点运算的LMS算法的硬件实现一直以来是学者们研究的难点和热点。

文献[1]提出了一种适合于FPGA(现场可编程门阵列)实现的自定义24位浮点格式和一种高效结构的多输入FPA(浮点加法器),这种结构的多输入FPA与传统的级联结构相比不仅可增加运算速度,还能大量减少所需的硬件资源。

本文正是基于这种高效结构的多输入FPA,在FPGA上成功实现了基于浮点运算的LMS算法。测试结果表明,实现后的LMS算法硬件资源消耗少、运算速度快且收敛性能与理论值相近。

1 浮点运算单元的设计

1.1 浮点加法器的设计

一般说来,双输入浮点加法器需要以下操作步骤:

a) 对阶操作:比较指数大小,对指数小的操作数的尾数进行移位,使操作数的阶码相同。

b) 尾数相加:对对阶后的尾数进行加(减)操作。

c) 规格化:规格化有效位并且根据移位的方向和位数修改最终的阶码。

在用FPGA进行数字信号处理的系统中,一般处理的数据都是经A/D采样送出的信号,其分辨率一般取12~16位,取18位有效位数即可满足绝大多数的情况。同时,目前FPGA 芯片内集成的乘法器均是18×18位的硬核。据此,文献[1]自定义了一种24位的浮点数据格式。

该格式的浮点数所表示的具体值可用下面的通式表示:

式中:m为18位补码数。

小数点定在最高位与次高位之间,这样m即表示-1~1之间的小数;e为6位补码数,范围为-32~31。且规定当m=0,e=-32时值为0。

传统的多输入浮点加法器结构如图2所示。以8输人为例,需要7个双输入FPA通过3级级联而成。这种结构的算法的顺序时延含有大量的重复步骤。如3级双输入FPA运算就有3次相同的规格化操作,如果将3级规格化操作用1级操作来代替,不仅可大大缩短运算时延,还可减少所需硬件资源。

基本运算单元不再是传统的双输入FPA,而是根据FPA的一般运算步骤构造的算法结构,通过大量采用并行运算从而大大减小运算时延。以8输入的对阶操作为例,改进算法的8输入对阶操作只需顺序进行3级比较操作、1级减法操作及1级移位操作即可完成;而采用图2所示的并行算法,则需顺序进行3级比较操作、3级减法操作及3级移位操作,相对于改进算法来说增加了2级顺序减法操作及2级移位操作时延。

1.2 浮点乘法器的设计

浮点乘法器与浮点加法器相比,不需要对阶等系列操作,实现起来相对简单示。

首先将输人数据的18位补码直接相乘得36位乘法结果,由于尾数的小数点定在最高位与次高位之间,相乘结果的绝对值小于1,故截取第35~18位为尾数乘法结果。尾数乘法结果与相加后的指数一起进行规格化输出即完成浮点乘法功能。

2 浮点LMS算法的FPGA实现

2.1 LMS算法的一般步骤

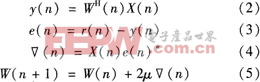

Widrow和Hoff在1960年提出了LMS算法,它是取单个误差样本平方的梯度作为均方误差梯度的估计,算法的步骤如下:

式(2)~式(5)中:y(n)为输出信号;X(n)为输入矢量;W(n)为抽头系数矢量;r(n)为参考信号;e(n)为误差信号;(n)为梯度矢量;μ为步长因子。

由式(2)~式(5)可知,LMS算法的所有运算均由加法及乘法操作组成,易于硬件实现。算法步骤其实为递推公式,且步骤中多处需进行多输入加法操作,这样,采用高效结构的多输入浮点加法器即可大量节约硬件资源并提高运行速度。

2.2 算法的FPGA实现

采用浮点LMS算法对自适应横向滤波器进行了实现。输入信号为500 kbit/s的伪随机序列加高斯白噪声,采样频率为4 MHz,采样数据为18位补码,共7级抽头系数。这样,由式(2)~式(5)可知,将第1步(式(2))、第2步(式(3))组合起来则需并行进行7个乘法操作,再进行一次8输入的加法操作;第3步(式(4))为并行进行7个乘法操作;第4步(式(5))需并行进行7个加法操作,其中肛取2-5,则其乘法操作在FPGA实现时可用移位操作代替。

采用的开发环境为ISE7.li,编程语言为VHDL,综合工具为Synplicity7.0,仿真工具为Modelsim6.0,FPGA处理时钟频率为64 MHz。

基于浮点运算的LMS算法所需硬件资源较少,运算速度高(最高时钟频率大于64 MHz),可以满足系统设计要求。

不同信噪比条件下FGPA实现后的仿真结果与理论仿真结果的对比图。由图中可清楚地看出,在FPGA上实现的浮点LMS算法的收敛性能与理论值非常接近。

3 结束语

LMS算法的理论虽然十分成熟,但浮点LMS算法的硬件实现因浮点运算单元的硬件资源消耗大、运算速度慢等缺点,从而一定程度上限制了LMS算法在需要快速数字信号处理场合中的应用。本文根据文献[1]提出的高效结果的多输入浮点加法器,成功地在FPGA上实现了浮点LMS算法。仿真测试结果表明,实现后的LMS算法硬件资源消耗少、运算速度

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码