为您的转换器选择正确的时钟(4)

预计结果

正确设计适当的时钟电路是比较困难的任务。但只要牢记本文涵盖的各个方面,对实现成功的设计大有帮助。总之,宽带噪声必须适合所需的信噪比性能,时钟杂散必须适合所需的杂散输出水平。许多SW(软件)工具有助于成功的设计,包括ADIsimPLL[3]和ADIsimCLK[4]。这些工具可从参考文献段落中提供的链接免费下载。

图21“典型时钟电路”显示的是典型的时钟净化、合成和分配网络。该网络旨在拾取不太干净的输入时钟,例如网络时钟,消除大部分时钟抖动并产生稳定的基准源,后者则可用于在此基础上合成任何所需的数据转换器时钟。图中未详细显示可用于合成本振和其他导出时钟的额外PLL网络,但其设计方式类似。

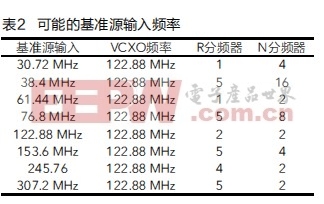

在典型应用中,时钟和合成器必须与外部来源同步。许多情况下,必须接受特定频率范围,例如表2“可能的基准输入频率”所示。此外,这些外部基准源一般会带来相对大量的噪声。为此,需要较窄的环路滤波器。由于该合成器的输出是固定频率,且需要较高性能,应优先选择VCXO而不是VCO,以确保高性能和极低的输出相位噪声。在此示例中,选择了Taitien的122.88 MHz VCXO。该应用选择了ADF4002 PLL。由于是固定频率应用,锁定时间不是首要因素,因此窄环路滤波器有助于尽可能减少基准源噪声。对于此应用,选择了1 kHz环路滤波器,如图22“时钟净化PLL”所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码